掌握简单的Makefile文件编程

Makefile描述整个程序的编译、链接规则

其中还包括了工程中用到的那些源文件及需要产生的目标文件

1)Makefile编程规则

目标(唯一):依赖(可多个)

命令...

伪目标

.PHONY:clean //声明clean命令为伪目标 clean: rm -f *.o led.elf led.dis //命令,删除所列出的中间文件

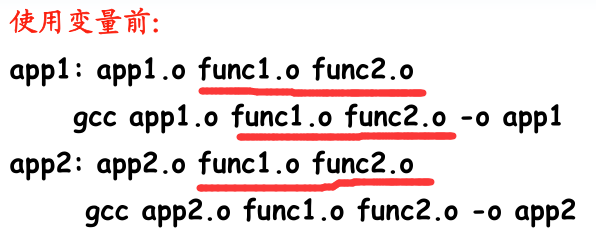

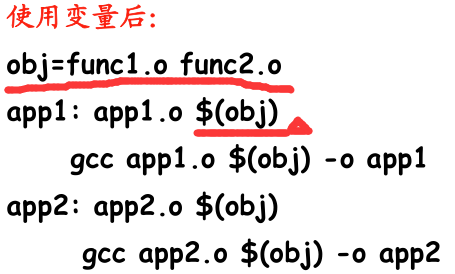

2)用变量代替连续出现的东西

3)默认变量

$@ : 代表目标

$^ : 代表所有依赖 $< : 代表第一个依赖

例子:

all:led.bin //最终目标 led.bin: led.o arm-linux-ld -Tled.lds -o led.elf led.o //交叉链接器 产生链接.elf arm-linux-objcopy -O binary led.elf led.bin //交叉转换器 将elf格式文件转换为二进制bin格式的文件(开发板可执行) %.o : %.S //相同规则命令合并 arm-linux-gcc -g -o $@ $< -c //-g添加GDB可调试功能 -o产生.o文件 -c编译依赖的一个文件 .PHONY: clean clean: rm *.o led.elf led.dis //删除中间文件