一、Moore有限状态机中,电路的输出取决于机器的状态而与其输入无关。

1 module MooreFSM(sel, clk, z_out); 2 input sel, clk; 3 output z_out; 4 reg z_out; 5 6 parameter S0 = 0, S1 = 1, S2 = 2, S3 = 3; 7 reg [1:0] mooreState; 8 9 always@(posedge clk) 10 case(mooreState) 11 S0:begin 12 z_out <= 1; 13 mooreState <= (!sel)?S0:S2; 14 end 15 S1:begin 16 z_out <= 0; 17 mooreState <= (!sel)?S0:S2; 18 end 19 S2:begin 20 z_out <= 0; 21 mooreState <= (!sel)?S2:S3; 22 end 23 S3:begin 24 z_out <= 1; 25 mooreState <= (!sel)?S1:S3; 26 end 27 endcase 28 endmodule

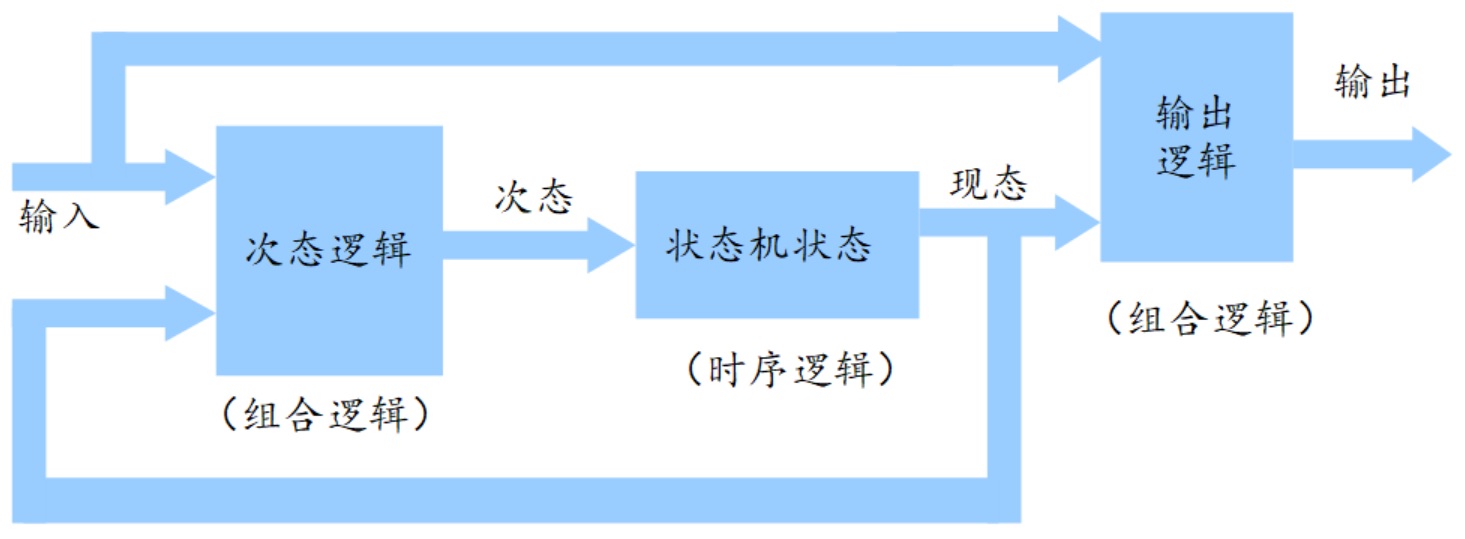

二、Mealy有限状态机,输出既取决于机器状态,又取决于其输入。

1 module MealyFSM(sel, clk, rst, z_out); 2 input sel, clk, rst; 3 output z_out; 4 reg z_out; 5 6 parameter ST0=2'b00, ST1=2'b01, ST2=2'b10; 7 reg [1:0] CurrentState, NextState; 8 9 //timing logic 10 always@(posedge rst or posedge clk) 11 if(rst) 12 CurrentState <= ST0; 13 else 14 CurrentState <= NextState; 15 16 //combinational logic 17 always@( * ) 18 case(CurrentState) 19 ST0:begin 20 z_out = sel ? 1:0; 21 NextState = sel ? ST2:ST0; 22 end 23 ST1:begin 24 z_out = sel ? 1:0; 25 NextState = sel ? ST0:ST1; 26 end 27 ST2:begin 28 z_out = 0; 29 NextState = sel ? ST1:ST2; 30 end 31 default:begin 32 z_out = 0; 33 NextState = ST0; 34 end 35 endcase 36 37 endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号