verilog基础---always

在verilog中,always块是一种常用的语句,可以是很简单的功能模块,也可以是结构最复杂的部分。

一般always语句可以分为两类电路。一种是组合逻辑。一种是时序逻辑。

第一类:组合逻辑

//-----1.1 组合逻辑 --------

Always @ (*)

Begin

If(a>b)

Q = 1;

Else

Q = 0;

end

//------- end -------------//

如1.1所示,就是一个简单的组合逻辑always块,它应该是被综合成一个一位的比较器。

//---- 1.2 组合逻辑 缺少敏感信号 ------

Always @ (a)

Begin

If(a>b)

Q = 1;

Else

Q = 0;

end

//------- end -------------//

代码 1-2 也是一个组合逻辑,与 1-1 不同的是,敏感信号列表中只有a没有 b。

我们知道,在 Verilog 语法中, always 块的含义是一个重复执行的语句。

那么 1-2 会综合成一个比较器:

- 当 a 发生变化时,q 发生变化

- 当 b 发生变化,由于 b 不再敏感信号列表中,所以 q 不变

这是一个彻头彻尾的软件思维,世界上不存在这种电路,综合器多半会综合一个与代码 1-1 一样的电路,然后报一个警告。

编写组合逻辑的 always 块,使用 * 代替敏感信号列表是一个简单方便而且不容易出错的好办法。

第二类:时序逻辑

//----- 2-1 时序逻辑 -------

reg [1:0] q;

always @ (posedge clk)

begin

q <= q + 1'b1;

End

注意:这里使用的是阻塞赋值,我们的 q 这个时候被综合成一个寄存器,而不是一个软件上的变量。

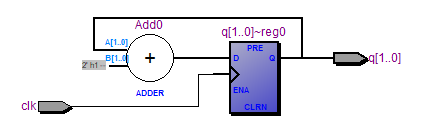

代码 2-1 是一个时序逻辑单元,它应该被综合成一个计数器,每当时钟的上升沿,q 自增一。综合后的 部分 RTL 图如下:

// 2-2 时序逻辑 ,带异步复位

reg [1:0] q;

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

q <= 2'b00;

else

q <= q + 1'b1;

End

综合后的 RTL 图如下:

代码2-2综合成一个带有清零端的 D 触发器,其余与 2-1 无异。

转载地址:https://blog.csdn.net/weixin_36590806/article/details/117255196

always语句注意点:

1、不要在不同的always块内为同一个变量赋值。即某个信号出现在<=或者=左边时,只能在一个always块内。

2、不要在同一个always块内同时使用阻塞赋值(=)和非阻塞赋值(<=)。

3、在使用always块描述组合逻辑时使用阻塞赋值(=);使用always块描述时序逻辑时使用非阻塞赋值(<=)。

4、任何在always块内被赋值的变量都必须是寄存器型(reg)。

5、always的敏感列表中可以同时包括多个电平敏感事件,也可以包括多个边沿敏感事件,但不能同时有电平和边沿敏感事件。另外,在敏感列表中,同时包括一个信号的上升沿敏感事件和下降沿敏感事件是不容许的,因为这两个事件可以合并为一个电平事件。

HHH~~~~

浙公网安备 33010602011771号

浙公网安备 33010602011771号