xilinx的transceiver调试

使用平台:vivado2018.03

使用IP:UltraScale FPGAs Transceivers Wizard(1.7)

主要目的:在questasim上仿真transceiver成功。

使用XCZU系列在vivado2018.03上建立工程,

选择IP Catalog-->FPGA Features and Design--> IO Interfaces --> UltraScale FPGAs Transceiver Wizard

设置界面

仿真验证过程:

1、对代码的初步验证,结果不通过。

在修改代码后,仿真能正常出波形,立马就验证了下rx和tx的数据。

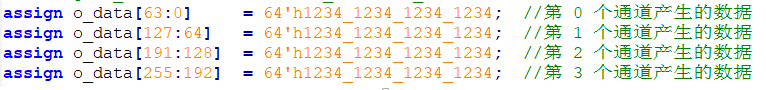

对tx的四个通道写入了四组相同的数据

仿真得出的rx内容:

发现数据与tx的数据不相同,但是数据很有规律的变化。可以理解为数据没有对齐。

2、在数据中加入同步码,并根据同步码,来纠正数据。

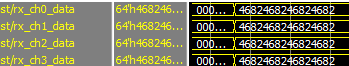

故在发送数据前面加一个同步码,用来校验数据位。

在发送端,加入了一个同步码,同步码内容如下:

然后,在接收端,进行识别同步码:

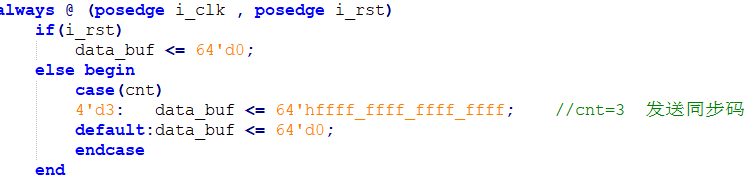

先缓存,连续两个相邻数据内容

![]()

根据内容,计算需要移位的多少:

内容有点长,所以只截图了一部分

根据 需要移位的多少 进行数据对齐

3、固定数据结果验证,结果通过

结果验证:

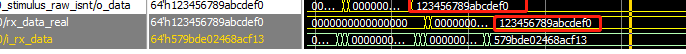

在发送端,还是继续发送64'h1234_5678_9abc_def0的数据内容,观察接收的数据在处理后是否正确:

截图中:

o_data: 是第一个通道的发送数据;

Rx_data_real : 是进行移位之后的正确数据;

i_rx_data:是transceiver接收到的原始数据。

通过图中观察到,Rx_data_real 和 o_data 值是一样的,更改是可以的。

4、随机数验证,结果通过

然后通过把数据内容更换为随机数观察:

![]()

发现数据还是有点对不上。怀疑是数据延迟太多,以至于找不到对应的数据,

故在把发送的数据内容更换为“计数器的计数”

![]()

通过观察发现,从tx的内容产生,到rx接收并移位完成,有16拍时钟的延迟,所以才导致在随机数中没有找到对应的数据。

重新进行随机数验证,通过往前后多查找一些数据,

![]()

往后16拍查找数据:

![]()

发现, Rx_data_real 和 o_data 值是一样的。

原创:https://blog.csdn.net/weixin_36590806/article/details/111067326

转载请说明出处。