xilinx的zynq平台的简易工程搭建

本文主要讲述 zynq平台的简单工程搭建,从pl端到ps端的工程。

这个工程要搭建一个ps端的iic接口,pl端个led灯接口。

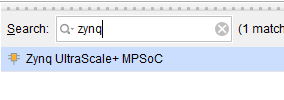

使用的软件:vivado 2018.3.

pl端:

由于使用到了zynq,所以在pl端必须使用原理图模式搭建工程。

原创链接:https://blog.csdn.net/weixin_36590806/article/details/111387559。

支持转载。

1、所以在自己的工程中,"Create Block Design" 创建自己的zynq

2、在界面中添加

3、选择主时钟

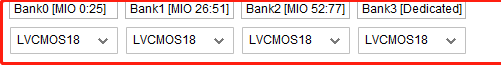

4、选择bank电压,这个要和自己的原理图对应

5,选择iic和串口,串口是用于打印的。

6、选择ddr的配置,我的原理图中的ddr4型号是:MT40A512M16LY-075:E

7、添加GPIO的ip,可以使PS和PL能联通普通的io。这个就不说了。

8、都设置后,点击自动连接按钮,使其自动连线。![]()

连接完之后的block如下图所示:我这里私自添加了一个pl端的iic。

9、确保没有错误后,点击“Generate Output Products”![]()

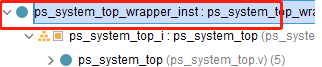

10、再点击“Create HDL Wrapper”生成Verilog文件![]()

这样我们刚刚创建的block就生成了我们熟悉的Verilog

ps端:

1、在pl端的sdk搭建完毕后,选择“Export Hardware”,导出hdf文件

2、导出后,使用Launch SDK 打开sdk的工程。

3、“Exported Location ”是刚刚导出的hdf文件位置。

“workSpace”是创建sdk工程的文件夹。

打开之后,新建工程

4、

“project name”自己取个帅气的名字。

“OS Platform”表示就是进行裸机运行。

然后添加自己的代码,就可以运行了。

5、自己编写C代码,这个也不说了。

然后还加上在sdk中烧录bit文件和sdk的文件;

1,在“xilinx-->program FPGA"中可以烧录bit文件。

2,在“run as --> 1Launch on Hardware”中烧录elf文件

浙公网安备 33010602011771号

浙公网安备 33010602011771号