DDS正弦信号发生器

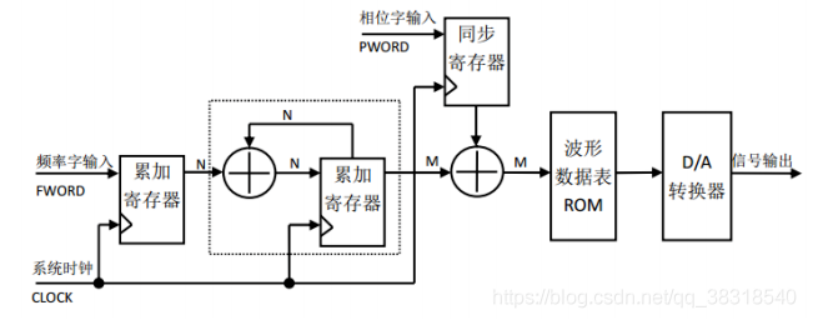

DDS的基本工作流程就是通过相位的累加,得到当前的相位值,然后用当前的相位值(转换为ROM地址)进行查表,得到相应的幅值,然后输出

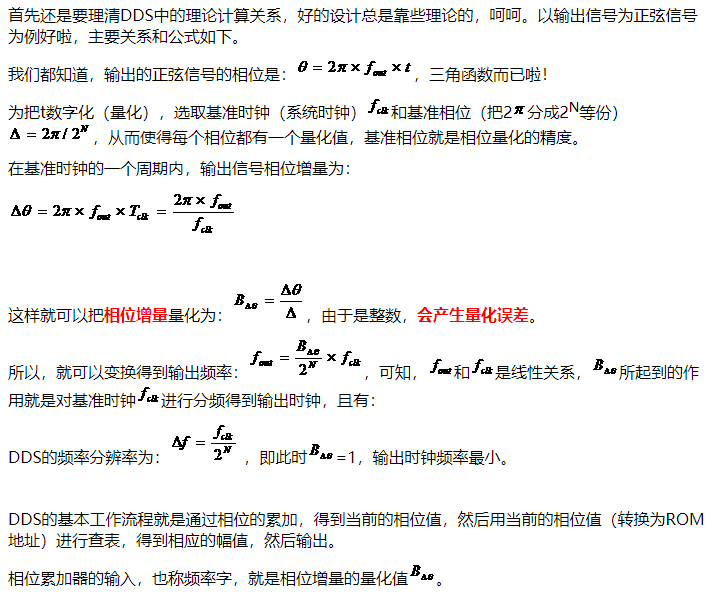

通过一些计算得出一个公式:

DDS正弦发生器的输出频率计算表达式:

fo = (fclk/2^N)*K

fo:输出正弦信号频率;fclk:输入脉冲频率(比如定时期中断频率);N:定时器里面的累加器的位数;比如32位、19位;N其实包含了DA位数,或者叫正弦波数据的数据位宽(256个数的正弦就会占N中的8位)。K:频率控制字,个人理解为累加器的累加因子,也就是每次进入定时器加多少。比如32位累加器,da值数据位宽占8位,则定时进入后累加K,一直累加到累加器的最高8位有数据变化,则输出AD值。

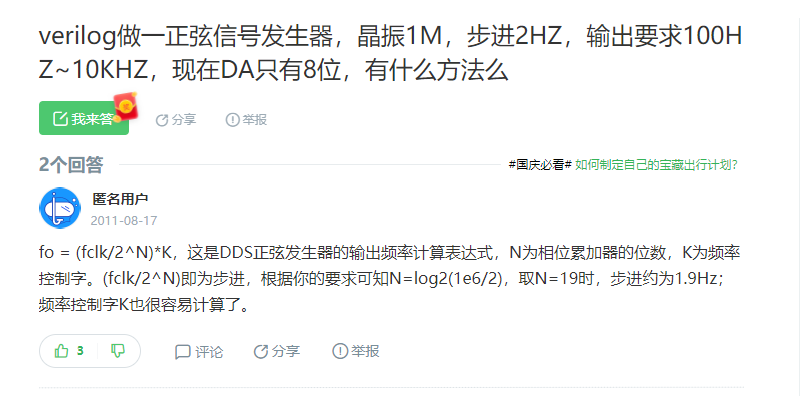

举例:

其实1.9HZ既是步进,也是能输出的最低频率,这时频率控制字=1,已经低于要求的100HZ。当要输出100HZ时,K=100*2^19/1e6约等于52.

程序例子:

用excel或者python算出256个点的sin值:

volatile unsigned char waveform[256] = {128, 131, 134, 137, 140, 143, 146, 149,

152, 156, 159, 162, 165, 168, 171, 174, 176, 179, 182, 185, 188, 191, 193,

196, 199, 201, 204, 206, 209, 211, 213, 216, 218, 220, 222, 224, 226, 228,

230, 232, 234, 236, 237, 239, 240, 242, 243, 245, 246, 247, 248, 249, 250,

251, 252, 252, 253, 254, 254, 255, 255, 255, 255, 255, 255, 255, 255, 255,

255, 255, 254, 254, 253, 252, 252, 251, 250, 249, 248, 247, 246, 245, 243,

242, 240, 239, 237, 236, 234, 232, 230, 228, 226, 224, 222, 220, 218, 216,

213, 211, 209, 206, 204, 201, 199, 196, 193, 191, 188, 185, 182, 179, 176,

174, 171, 168, 165