会员

周边

新闻

博问

闪存

众包

赞助商

Chat2DB

所有博客

当前博客

我的博客

我的园子

账号设置

会员中心

简洁模式

...

退出登录

注册

登录

JsDakey

博客园

首页

新随笔

联系

订阅

管理

2022年6月11日

经典H桥电路的变体

摘要: 老师给了几个经典电路图,班里有些同学看不懂,我打算用通俗易懂的语言分析一下。希望通过我的解析,尽量能让他们搞透。 文接上回,定性分析了最基础的H桥驱动。现在我们把它改变一下,如下图 基本电路的外围新增了两个电阻和两个NPN。 先来说说工作原理,Q2、Q4各给一路电平信号,要求信号互补;Q2=1且Q4

阅读全文

posted @ 2022-06-11 00:47 JsDakey

阅读(246)

评论(0)

推荐(0)

2022年6月10日

经典H桥电路分析

摘要: 老师给了几个经典电路图,班里有些同学看不懂,我打算用通俗易懂的语言分析一下。希望通过我的解析,尽量能让他们搞透。 来看这个电路。这是一个最基础的H桥驱动电路。再具体分析之前,浅谈一下三极管的饱和以便后续的展开。 对于三极管,你可以把它粗略地等价成两个二极管的连接,如下图 箭头指向就是由P(posit

阅读全文

posted @ 2022-06-10 12:04 JsDakey

阅读(1736)

评论(1)

推荐(0)

2022年6月9日

第十章练习题

摘要: 1.题目:用状态机实现按循环码$000 \rightarrow 001\rightarrow 011\rightarrow111\rightarrow101\rightarrow100\rightarrow000$规律工作的六进制计数器 module cnt_6(clk,rst,cnt_out);

阅读全文

posted @ 2022-06-09 13:28 JsDakey

阅读(144)

评论(0)

推荐(0)

2022年6月8日

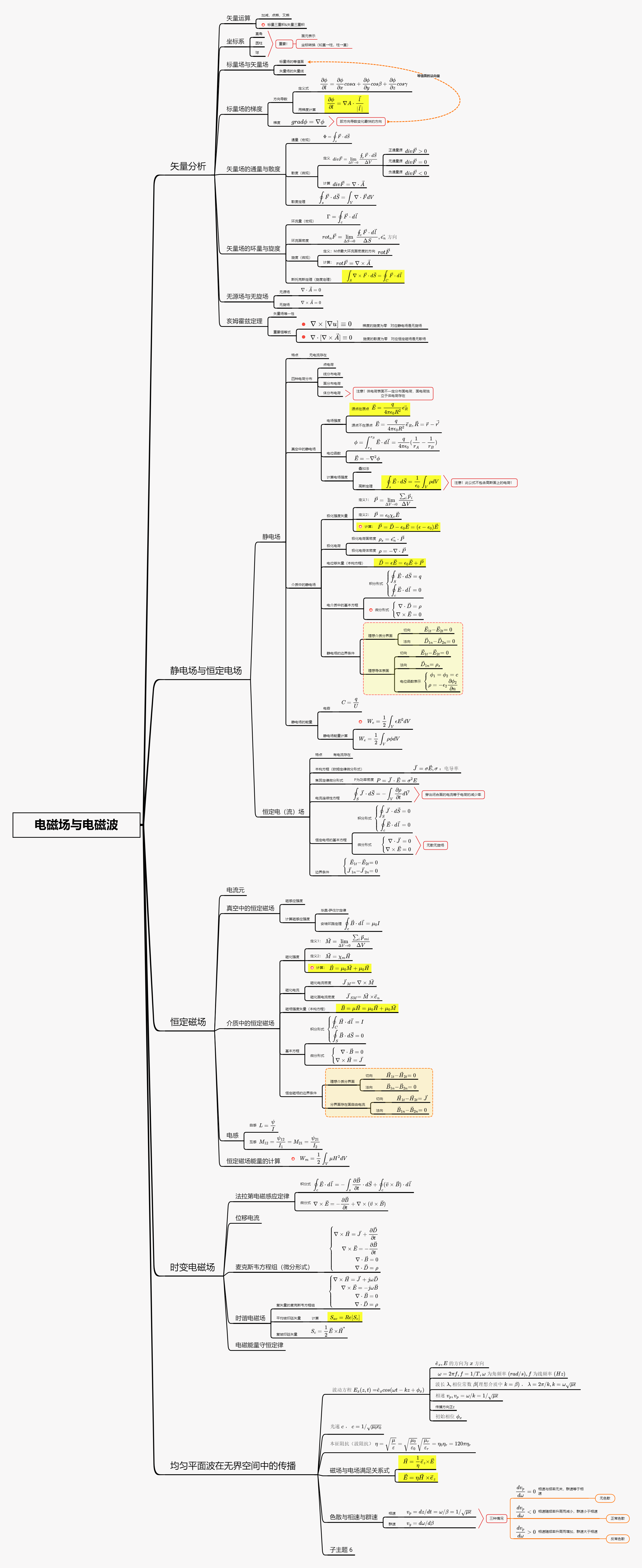

小结导图

摘要:

阅读全文

posted @ 2022-06-08 14:50 JsDakey

阅读(55)

评论(0)

推荐(0)

第八章课堂练习

摘要: 题目:设计一个四位双向端口模块 module BI4B(CTRL,DIN,Q,DOUT) input CTRL;//数据方向控制位,0时Q作输入,1时Q作输出 input [3:0]DIN; inout [3:0]Q output [3:0]DOUT; reg [3:0]DOUT,Q; always

阅读全文

posted @ 2022-06-08 14:31 JsDakey

阅读(114)

评论(0)

推荐(1)

第五章课堂练习2

摘要: 题目:设计加减可控的16bit计数器 module ADD_SUB_LOAD(CLK,RST,ADD_EN,SUB_EN,LOAD,DATA,CQ,COUT); input clk;//时钟信号 input RST;//复位信号 input ADD_EN;//加法标志位 input SUB_EN;/

阅读全文

posted @ 2022-06-08 14:14 JsDakey

阅读(82)

评论(0)

推荐(0)

第五章练习题_1

摘要: 1.题目:根据RTL图给出HDL描述 DFF的引脚功能: PRE与CLR均为异步控制信号;PRE置高,DFF输出为1;CLR置高,DFF输出为0; 分析:信号优先级为 \(CLR>PRE\);当ENA为1时,时钟启动,CLR为0时,模块清零,PRE为1时,模块置1;ENA为时钟控制信号, modul

阅读全文

posted @ 2022-06-08 12:53 JsDakey

阅读(225)

评论(0)

推荐(0)

2022年6月7日

第三章练习题

摘要: 1.题目:用循环语句设计一个逻辑电路模块,用以统计一个8位二进制数(8bit并行输入)中含1的数量 module for_cnt_1(a,b); input [8:1] a;//定义输入8位二进制数 output [4:1] b;//定义求和输出变量,因最多8个1相加,故要求四位位宽 reg [8:

阅读全文

posted @ 2022-06-07 21:01 JsDakey

阅读(451)

评论(0)

推荐(0)

第三章语法

摘要: 1.模块语句及表达 module name(a,b,c,d,e,f);//模块名(信号列表) input a,b; output c; inout d; input [4:1]e; output [4:1]f; endmodule input:单向输入 output:单向输出 inout:双向(输入

阅读全文

posted @ 2022-06-07 19:53 JsDakey

阅读(146)

评论(0)

推荐(0)

第一章问答

摘要: 问答_记关键词 Q1:EDA 技术与ASIC 设计和FPGA 开发有什么关系?EDA技术进行电子系统设计的最后目标是什么? A1:1.利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC 的设计和实现;2.FPGA和CPLD是实现这一途径的主流器件;3.FPGA和CPLD的应用是对ED

阅读全文

posted @ 2022-06-07 19:50 JsDakey

阅读(227)

评论(0)

推荐(0)

下一页

公告