锁存器和触发器

锁存器

基本双稳态电路

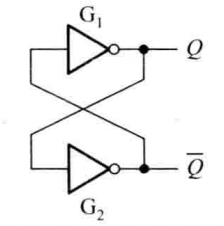

电路图如下:

若Q=1,则电流在电路中流动后又进一步保证Q=1;反之亦然。故只要该电路进入了一个状态,他就会保持这个状态下去,具有存储的效果(当然,其没有控制机构不能作为真的存储设备)。我们可通过检验Q电平水平得知其所处的状态。

SR锁存器

基本SR锁存器原理

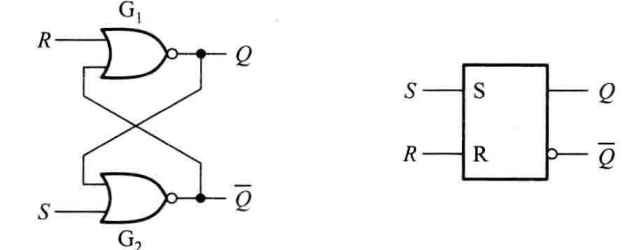

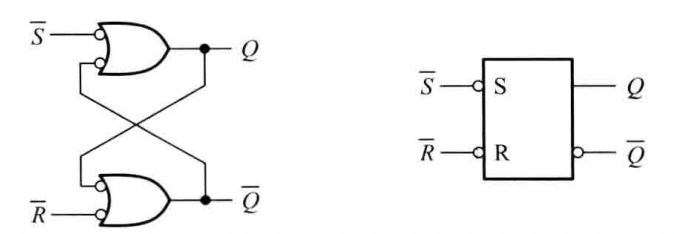

基本SR锁存器电路图如左下,逻辑符号如右下:

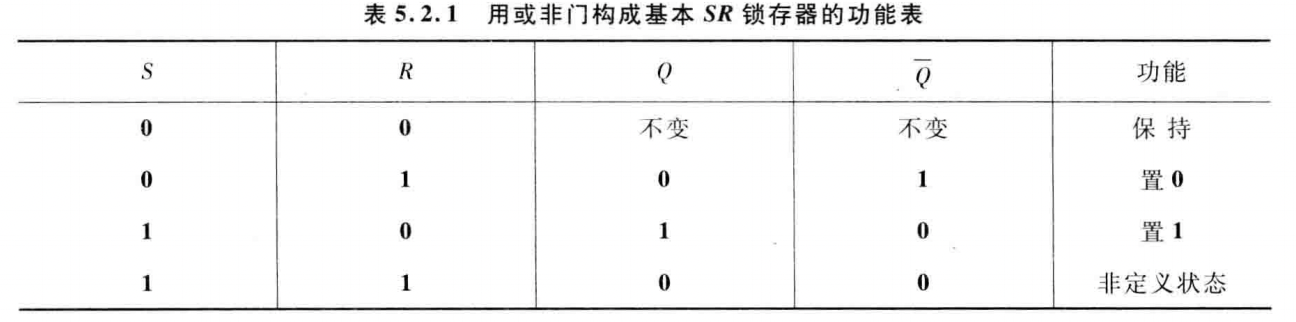

真值表如下:

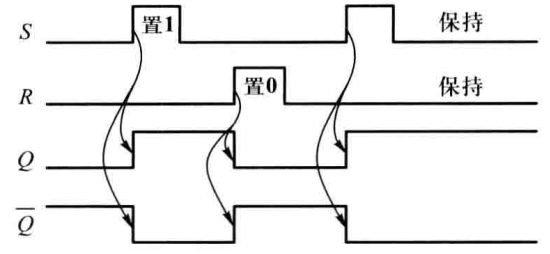

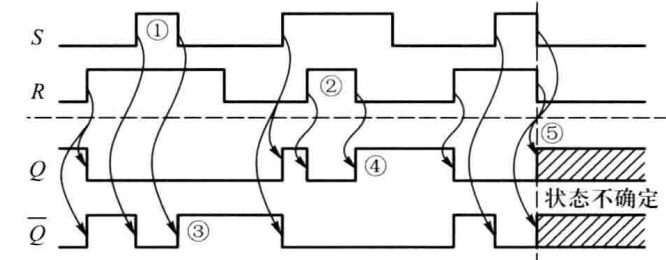

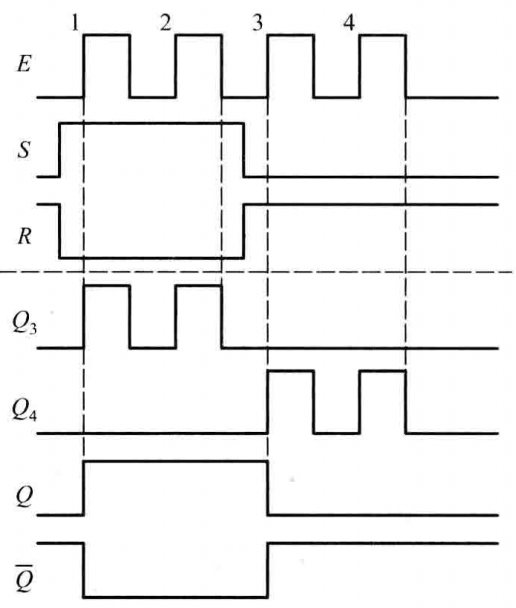

工作波形图如下所示:

题型之一,便是仿照上图,给出SR波形及初始条件,画出Q波形。例题如下,上半部分是题目:

基本SR的动态特性

此前的讨论仅考虑了电路的逻辑关系,没有涉及门电路输出信号对输人信号的时间延迟,即电路的动态特性。这种延迟有时会影响到被其驱动的后续电路的动作,可能造成错误的逻辑输出或出现工作不稳定的情况。此外,为保证锁存器状态可靠转换,对输人信号也需要有一定的时间要求。

定时图是表达时序电路动态特性的工具之一,它表达了电路动作过程中,输出对输人信号响应的延迟时间,以及对各输人信号的时间要求。下图为基本SR 锁存器的定时图。

图中,脉冲信号的上升沿和下降沿均用斜线表达,表示存在一定的上升时问和下降时间,脉冲沿的基准时间定位在上升沿和下降沿的 50%处。

- 传输延迟时间

可以从上图看。一个指高电平到低电平延迟时间,一个指低电平到高电平延迟时间。对于具体电路,一般来说两者是不等的。 - 脉冲宽度

上图中,

用与非门构成的基本SR锁存器

电路图如下:

真值表如下:

为了区别,这种锁存器有时也称之为基本

基本SR锁存器的应用

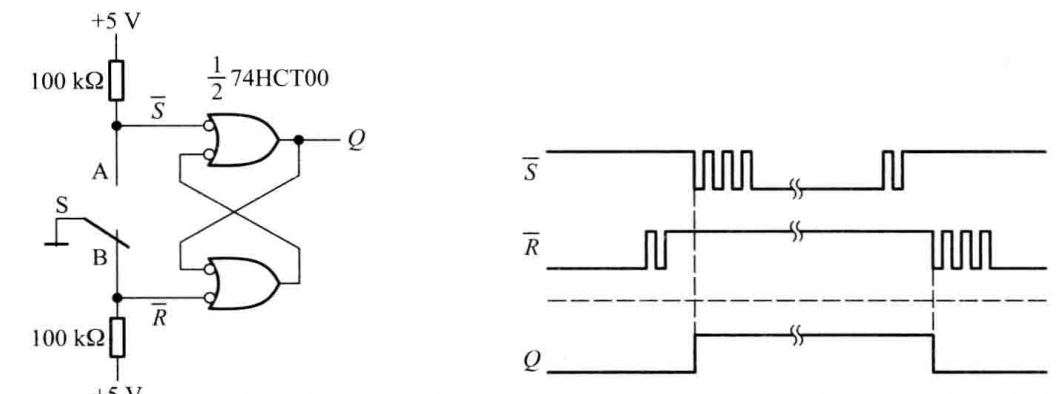

可以应用于数字系统中某些特定标志的设置。可以消除机械开关触电抖动引起的脉冲输出。

机械开关(例如按键、拨动开关、继电器等)常常用作数字系统的逻辑电平输人装置。由

于机械开关接通或断开瞬间的弹性振颤,触点会在短时间内多次接通和断开,使得逻辑电平多次在0和1之间跳变,导致错误逻辑输人数字系统。我们可采取如下所示的方法解决:

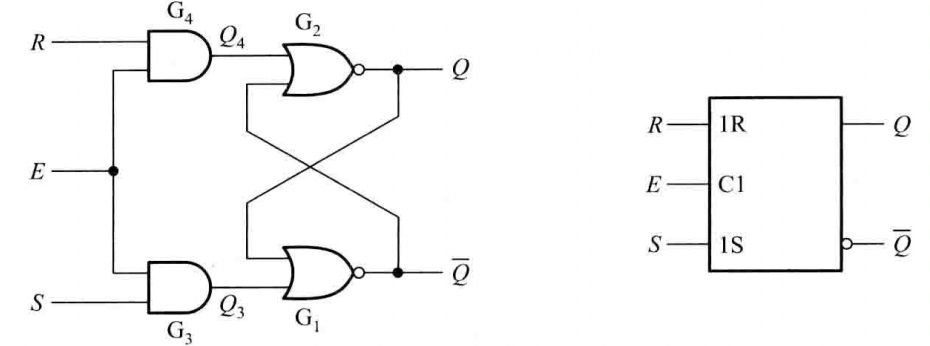

门控SR锁存器

前面所讨论的基本 SR 锁存器的输出状态是由输人信号S或R直接控制的,而下图所示电路在基本 SR 锁存器输人端增加了一对逻辑门

当

给出这种锁存器的E、S、R波形图,如何得到Q?首先我们得知道,

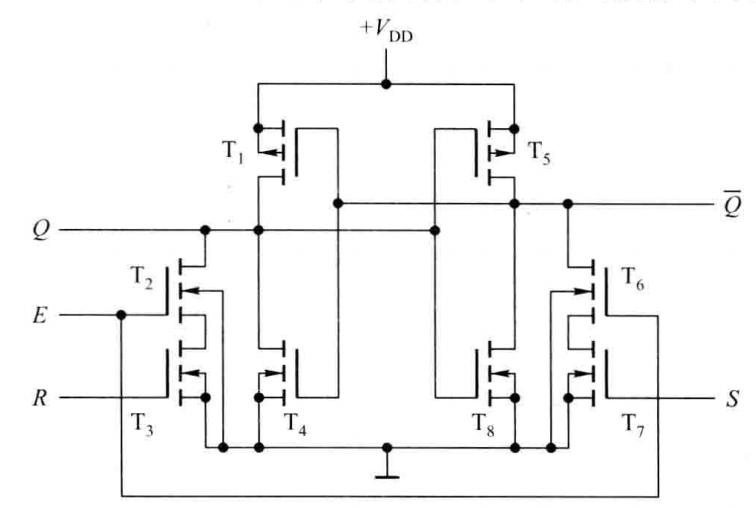

CMOS集成电路中的门控SR锁存器

电路图如下:

必须严格遵守SR=0的约束条件,否之除了T4全导通,电路功耗会很大。

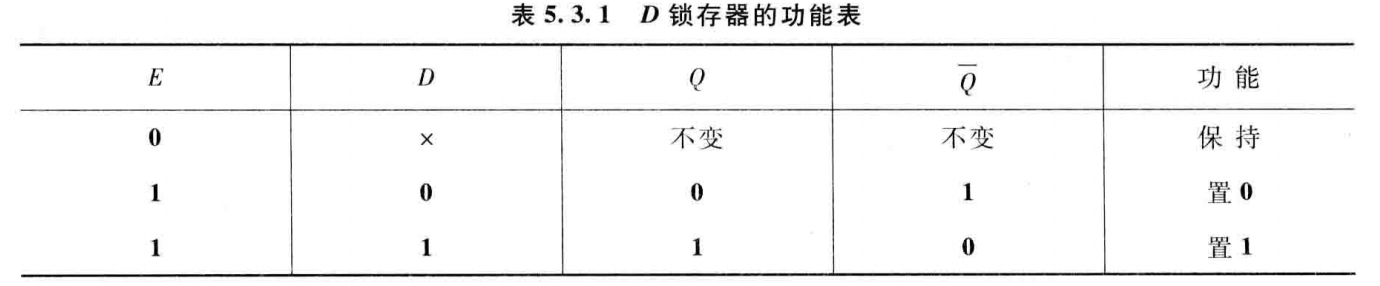

D锁存器

与 SR锁存器不同,D锁存器在工作中不存在非定义状态,因而得到广泛应用。目前,CMOS集成电路主要采用传输门控口锁存器和逻辑门控口锁存器两种电路结构形式,特别是前者电路结构简单、在芯片中占用面积小而更受青睐。

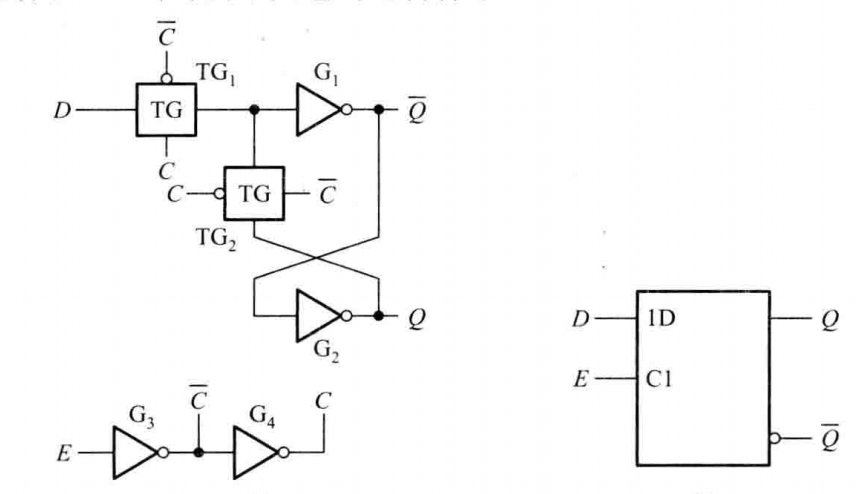

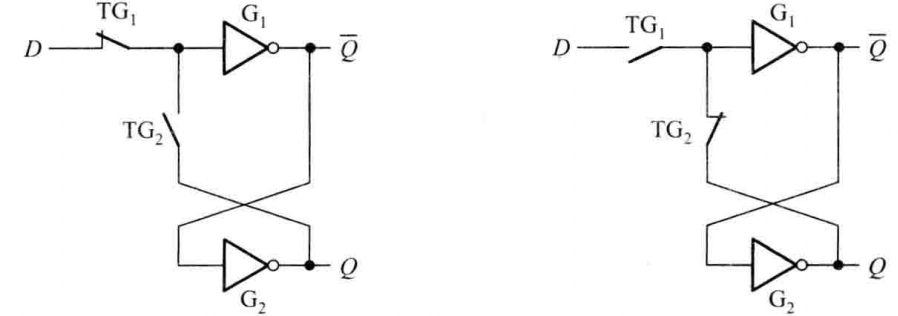

- 传输门控D锁存器

电路图如下:

注意传输门的使用,该电路会有如下两种情况:

下图为其真值表:

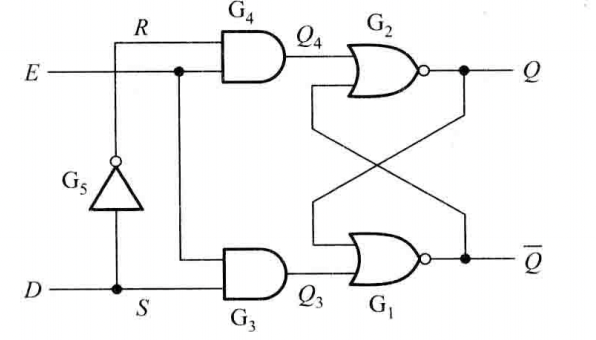

这种锁存器E=1时Q随着D变,故又称为透明锁存器。 - 逻辑门控D锁存器

电路图如下:

它在门控 SR 锁存器的S和R输人端之间连接了一个非门

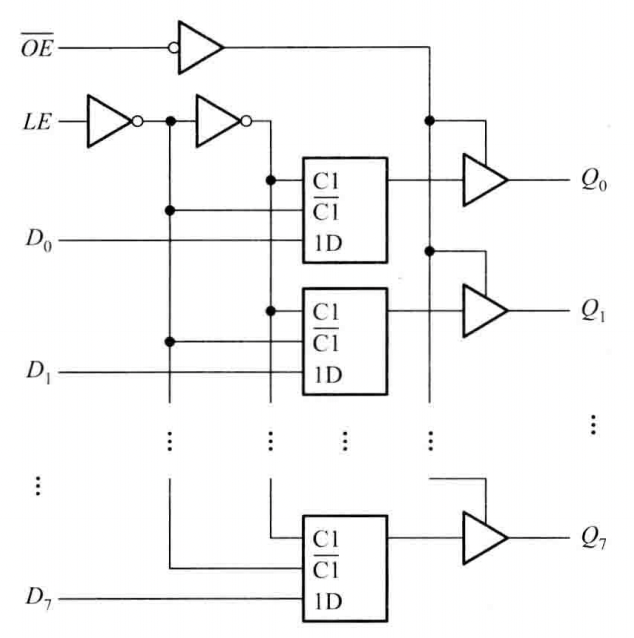

典型D锁存器集成电路

- 74HC373、74HCT373

电路图如下:

功能表如下:

OE=0才能输出。LE为高电平时允许D锁存器输出跟随输入信号变化,LE为低电平则保持不变。 - 74LVC32373A

下图所示为“宽总线”锁存器 74LVC32373A 的内部简化逻辑图,芯片中集成了 32个三态输出的口锁存器,它们分为4组,每一组的逻辑功能都相当于一个74HC373,各组间既可同步工作,又可独立运行,异步工作。这种结构给芯片的总线应用带来很大的灵活性。

- 74LVC1G373

其逻辑功能只相当于74HC373中的一路。

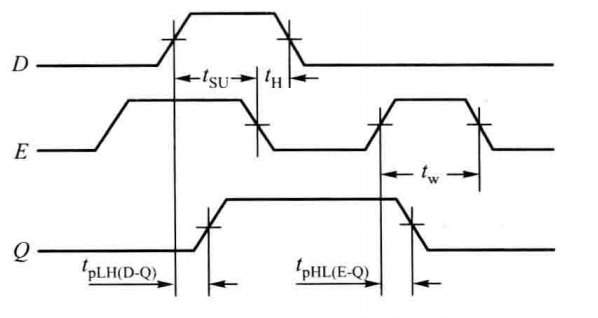

D锁存器的动态特性

- 传输延迟时间

对于CMOS集成电路来说,(D-Q)与(E-Q)是一样的,故统一用 - 建立时间

信号D的逻辑电平必须在使能信号上下降沿到来之前建立起来,,才能保证正确地锁存。 - 保持时间

在£电平下降后,D信号不允许立即撤除,否则不能确保数据的锁存。 - 脉冲宽度

脉冲宽度前面已经有介绍。这是为了确保D信号有效。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 25岁的心里话

· 闲置电脑爆改个人服务器(超详细) #公网映射 #Vmware虚拟网络编辑器

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· 零经验选手,Compose 一天开发一款小游戏!

· 一起来玩mcp_server_sqlite,让AI帮你做增删改查!!