数字电路学习笔记

逻辑门电路

CMOS逻辑门电路的不同输出结构及参数

CMOS漏极开路门和三态输出门电路

漏极开路门

工程时,我们有时需要将两个门的输出端并联实现与逻辑(此功能成为线与)。但我们不能直接将输出端连在一起,因为这样可能造成电流过大,而且可能两个低电平组合成高电平造成无法区分高低电平。 这一问题我们使用OD门来解决。 漏极开路门与非路电路如下:

使用漏极开路与非门实现线与,电路图如下:

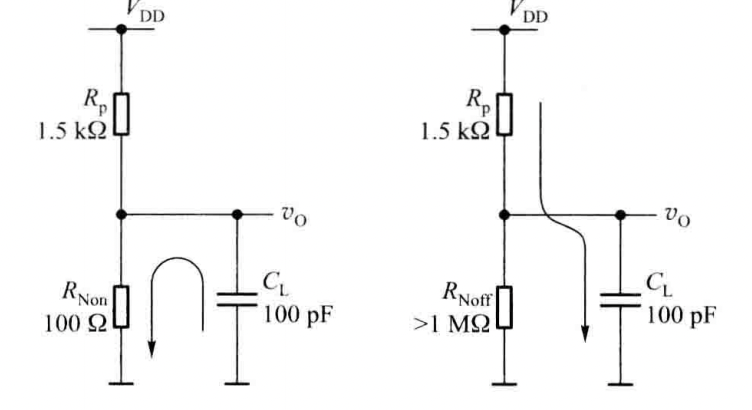

可以看到,电路中加了一个上拉电阻 \(R_p\)。上拉电阻会影响OD门的开关速度。\(R_p\)小则负载电容充电时间小,开关更快。但其不能太小,它起码(因为这里并不是其真实最小值)必须保证OD门输出端的电流不能超过允许的最大值\(I_{OL(max)}\),用\(V_{DD}/I_{OL(max)}\)即可知道。与普通CMOS电路比,这个导通电阻明显大了些,因此OD门高低电平转换速度比普通CMOS门慢。 除此之外还有个问题就是门驱动电容性负载充电时间问题。

左图为OD门输出由高变低时的等效电路情况,充电时间为\(\tau = 100pF \times 100\Omega=10ns\);右图为OD门输出由低变高时的等效电路情况,充电时间同理可得。

接下来计算\(R_p\)。

- 输出为低电平时,只有一个OD门导通时(没OD门导通最小值就是上面那个“起码”中计算出的结果),电路图中易知其最小值为:$$R_p = \frac{V_{DD}-V_{OL(max)}}{I_{OL(max)}-I_{IL(total)}}$$。OL 用 "Output Low"就会好记得多,同理OH是"Output High"。

- 若所有OD门输出为高电平时,输出为高电平。经过上拉电阻的电流一部分分给漏极电流,一部分输出,故:$$R_p =\frac{V_{DD}-V_{IH(min)}}{I_{OZ(total)}-I_{IH(total)}}$$

三态输出门

用上拉电阻来解决线与的功能,会影响速度。符号如下:

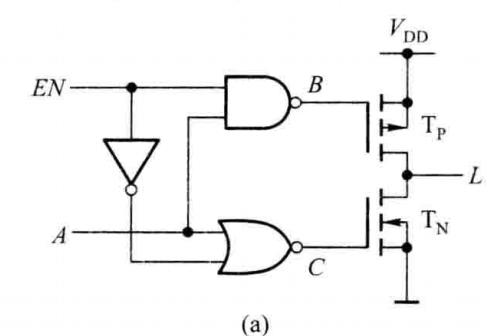

电路图如下:

其功能如下:

EN=1时,如果A=0,则B=1,C=1,这样输出L=0;EN=1时,L=1;EN=0时,Tp、Tn都截止,是开路。真值表如下:

CMOS重要参数

- 输入输出高低电平

- 噪声容限

示意图:

![image]()

\(V_{NH}\)为输入高电平的噪声容限;

\(V_{NL}\)为输入低电平的噪声容限。

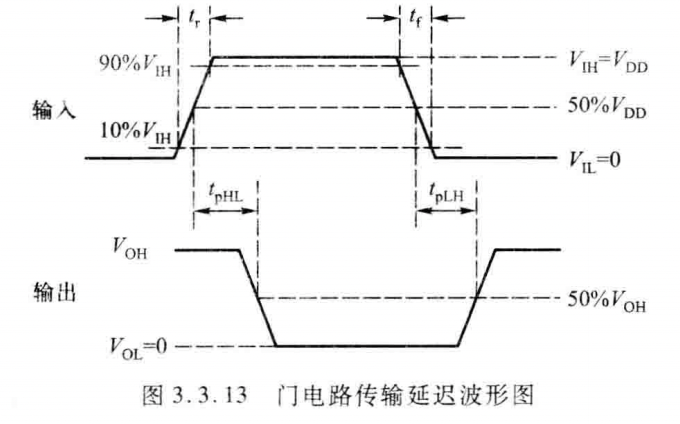

噪声容限越大,抗干扰能力越强。 - 传输延迟时间

图如下:![image]()

由于对称性,\(t_{pHL}=t_{pLH}\)。有时人们用平均传输延迟时间。 - 功耗

CMOS静态电流很小,静态功耗低,所以常用于各种便携设备。

动态消耗:即输出状态发生转换时的功耗称之为动态功耗。一部分是电流流入地,一部分是因为充放电(CMOS负载的电容性)造成的损耗。他们的总功耗为:$$P_D = V_{DD}^2(C_{PD}+C_{L})f$$ - 延时-功耗积

\(t_{pd}\)为之前说到的平均传输延迟。DP越小越好。

- 扇入/扇出系数

扇入数取决于输入端个数。

扇出数:\(N_{OH}=\frac{I_{OH}(驱动门)}{I_{IH}(负载门)}\)(或者OH换做OL)。

![image]()

类NMOS和BiCMOS逻辑门电路

类NMOS逻辑门电路

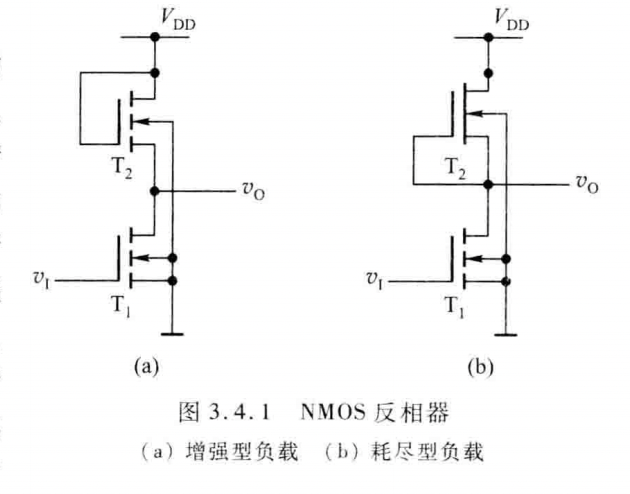

MOS从PMOS到NMOS到CMOS。PMOS以空穴为导电载流子,NMOS以电子为导电载流子。后者速度更快。NMOS是全部由n沟道MOS管构成。其工作管为增强型,而负载管都可以。现在一般用耗尽型因为速度更快。两种NMOS管电路图如下:

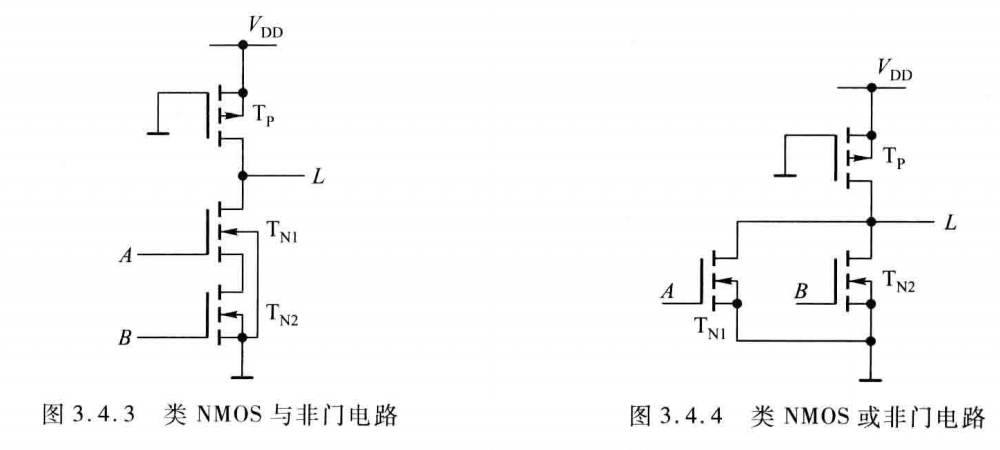

类NMOS管采用PMOS增强型负载管。相比耗尽型NMOS管,其噪声容限变大,与CMOS匹配。其反相器、与非门、或非门电路图如下:

与CMOS相比,类NMOS电路PMOS管减少了,且输入端数目越多,减少的PMOS管越多。

类NMOS反相器多用于输出高电平的电路;类NMOS电路多以或非门为基础,因为并联时增加NMOS管不会影响低电平输出电压的稳定;而增加与非门输入端数目时,串联管子变多,输入全高电平时导致低电平输出电压升高破坏逻辑功能。

BiCMOS逻辑门电路

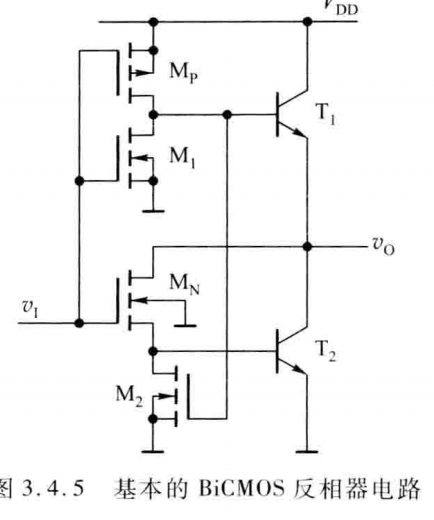

BiCMOS门的特点在于采用了双极型BJT管作为CMOS电路的输出极。这种电路具有高集成度、低功耗、速度快、驱动力强的特点。电路图如下:

此部分学习总结

搞清楚NMOS和PMOS管(消耗性增强型)的原理、电路及作用。可以通过CMOS各种门类比到类NMOS门的情况,然后就是知道CMOS的各种参数及组成的电路需要满足的条件。

TTL逻辑门电路

BJT开关

BJT开关(也即三极管)电路图如图所示:

BJT为NPN型硅管。输入低电平则输出高电平,输入高电平则输出低电平。BJT的开关过程伴随着内部电荷的建立和消散,故需要一定的时间。

TTL反相器

由于BJT反相器动态性能并不理想,实际中还增加了若干器件构成TTL反相器。

输人级的作用是用来提高工作速度。当电路的输人电压由高到低变化时,T1由倒置的放大状态转换为放大状态,使T2的基极电流增加,加快抽走多余的存储电荷而达到截止。T2的迅速截止,一方面使T4的导通加快,另一方面使T4的截止加快,从而加快了状态转换。

采用推拉式输出级以提高开关速度和带负载能力。输出级的两个管子总是一个导通而另一个截止,因此降低了静态功耗。当输出端接有电容性负载时,T3或T4饱和导通电阻很低,对电容充、放电时间常数很小,使输出电压波形的上升沿和下降沿都很好。

抗饱和TTL门电路

TTL门电路参数

TTL逻辑门部分总结

清楚三极管原理及使用方法。

浙公网安备 33010602011771号

浙公网安备 33010602011771号