[学习/自用]计算机组成原理 期末考试复习笔记

计算机组成原理 期末复习笔记

第一章 计算机组成原理绪论

-

计算机硬件系统的五大组成部分

- 存储器

- 运算器

- 控制器

- 输入设备

- 输出设备

-

存储程序的工作方式

程序执行前,需要将程序所含的指令和数据送入主存。程序自动逐条取指令并执行,直至程序结束

-

冯诺依曼思想

- 采用“存储程序”的工作方式

- 计算机硬件系统由五大部件构成

- 指令和数据按照同等地位存储,形式上无区别

- 指令和数据均使用二进制表示,指令由操作码和地址码构成

-

计算机软硬件在功能上逻辑等价

对于某一功能,既可以由硬件实现,又可以由软件实现。

-

计算机性能评价指标

-

CPU性能指标计算公式(部分)

-

主频:CPU主频=外频×倍频系数,指的是CPU的时钟频率

-

\(CPI = m_c/n_i\),其中\(m_c\)代表程序的时钟周期总数,\(n_i\)代表程序的指令总数

-

-

数据通路宽度、数据传输率

- 数据传输率\(DTR=\frac{D}{T} = Wf\),其中D代表数据传输量(信道总负载而不是有效数据),T为传输时间,W为数据通路宽度,f为工作频率

-

第二章 机内数据表示法

-

数制转换:除k取余、乘基取整、按权展开

-

特附:小数转为二进制的方法:循环乘二,与一判断,自上而下。

以0.1为例:

-

循环乘二,与一判断

0.1 * 2 = 0.2 <1 --- 0 0.2 * 2 = 0.4 <1 --- 0 0.4 * 2 = 0.8 <1 --- 0 0.8 * 2 = 1.6 >1 --- 1 1.6-1*2 = 1.2 >1 --- 1 1.2-1*2 = 0.4 <1 --- 0 -

自上而下,得出结果:\([0.1]_{DEC} = [0.00011001100...]_{BIN}\)

-

-

-

原码、补码、反码、移码

- 原码:最高位为符号,其余各位表示数的绝对值

- 原码的零有正负两种形式

- 补码:负数用基数减去真值(类比于17的补码1000-17=983):\([x]_补=2^{n+1} -|x|\),或者各位取反,末位+1

- 零唯一

- 反码:负数各位取反

- 零不唯一

- 移码:在真值上加一个偏置值(通常为\(2^{n=1} -1\) ),或者补码符号位取反

- 零唯一

- 原码:最高位为符号,其余各位表示数的绝对值

-

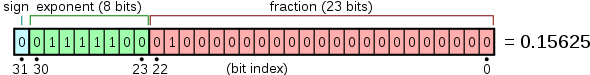

定点数编码规则(略)、浮点数编码规则

-

分为数符、阶码、尾数

-

表示范围:由\(N=(-1)^{数符}\times尾数\times基数^{阶数}\)反推,其中基数默认为\(2\)

-

-

浮点数

- 表示方法:阶码(内含阶符)+尾数(内含数符)

- 规格化

- 左规:运算结果尾数最高位不为0,尾数向左算术移位,阶数对应下降

- 右归:与左归相对应,一般只进行一次

原码表示的浮点数规格化之后最高位为1

-

溢出判断

\(V=A_SB_S\overline {S_S} + \overline {A_S}\ \overline{B_S}S_S\)

\(V = C_S \oplus C_1\),\(C_S\)指符号位进位,\(C_1\)指最高位进位

\(V = S_1 \oplus S_2\),\(S_n\)指第\(n\)个符号位

-

移位操作、舍入处理、数位的拓展与压缩

- 移位操作:符号位不变

- 正数都添0(原码、补码、反码)

- 负数

- 原码:添0

- 补码:左移添0,右移添1

- 反码:添1

- 双符号位:第一符号位不动,第二符号位参与移位

- 舍入处理:”0舍1入“、恒置1、截断法

- 数位的拓展与压缩

- 移位操作:符号位不变

-

原码一位乘法、补码一位乘法(比较法/Booth)、原码不恢复余数除法、补码不恢复余数除法

- 原码一位乘法

- 符号位:\(S_S = x_S\oplus y_S\)

- ACC存乘积高位(执行之前清零),MQ存乘数(的绝对值原码)、乘积低位,X存被乘数

- 运算规则:若当前最低位\(y_n\)为1,则部分积加上\(|x|\),否则加\(0\)。右移一位,执行\(n次\)

- 注意使用双符号位

- 补码一位乘法(Booth)

- 符号位参与运算,运算数用补码表示

- 被乘数、部分积取双符号位,乘数取单符号位

- 乘数末位附加\(y_{n+1}\),初始设为0

- 运算规则:\(y_n \oplus y_{n+1} =0\)则右移一位,否则若\(y_ny_{n+1}=01\),部分积加\([X]_补\),否则加[\(-X]_补\),然后右移一位

- 执行\(n+1\)步累加和\(n\)步右移(第\(n+1\)步不移位)

- 除法略

- 原码一位乘法

-

浮点数四则运算(以IEEE 754为准)

- 阶码和尾数同为0,浮点数为0

- 对阶:让尾数权值相同,便于直接加减

- 计算

- 规格化

-

数据校验

-

奇偶校验:校验位插入0或1,来保证数据中1的个数是奇数个或者偶数个

-

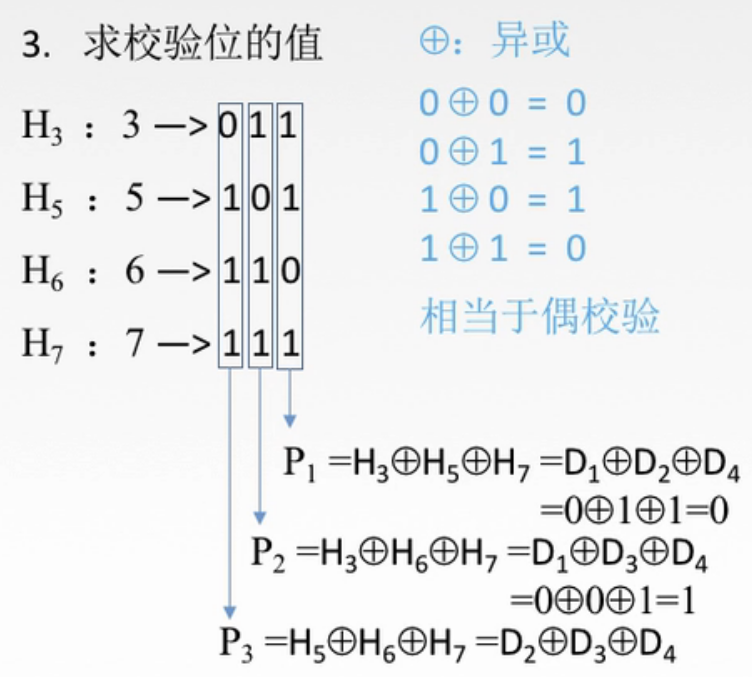

海明校验(王道考研方法改)

-

校验位数量不等式\(2^k\ge n+k+1\),\(n\)为信息位数,\(k\)为校验码数

-

校验位放在\(2^n=1,2,4,8,...\)位置(即\(P_i\)放在\(2^{i-1}\)位置)

-

将剩余的其他位的位置写成二进制形式,出现1的位置将对应的值累计异或

-

如果是奇海明校验,则需要将步骤3中求出的值按位取反,再插入原始数据

-

校验方程:(以上图为例)\(S_1 = P_1\oplus D_1\oplus D_2\oplus D_4\),\(S_2,S_3\)也同理。生成\(S_1S_2S_2\)为二进制数,其值即为错误位置

-

-

循环冗余校验

-

构成:K位信息位和R位校验位,N=K+R,K=信息位长度,R=生成多项式最高次幂

-

生成多项式(以\(x^3+x+1\)为例),写为\(1x^3+0x^2+1x+1\),提取系数\(1011_{bin}\)

-

操作步骤

-

信息位左移R位,低位补0

-

移位后的信息码与生成多项式系数执行模二除法,产生余数R

模二除法简要规则:

- 根据最高位是1还是0确定当前商位是1还是0(对应)

- 商完之后异或

-

-

校验:接收方使用生成多项式系数执行模二除法,余数即为错误位置

-

-

第三章 CPU

-

CPU功能:指令处理、操作执行、时间控制、数据处理

-

时序系统:工作周期、时钟周期、工作脉冲

-

指令的地址结构(只记零地址双操作数指令:存取栈顶和次栈顶的数据)

-

拓展操作码:一种指令优化技术,操作码的长度和地址长度动态变化

-

寻址方式

- 立即寻址:指令中包含操作数I

- 主存直接寻址,记作\((A)\):指令中包含主存地址A,主存地址A中包含操作数I

- 寄存器直接寻址,记作\(R_n\):指令中包含寄存器号R,寄存器R中包含操作数I

- 主存间接寻址,记作\(@ A\),指令中包含主存地址A,主存地址A中包含主存地址B,主存地址B中包含操作数I

- 寄存器间接寻址,记作\((R_n)\),指令中包含寄存器号R,寄存器R中包含主存地址A,主存地址A中包含操作数I

- 自增型寄存器间址,记作\((R_n)+\),取出之后寄存器自减一

- 自减型,记作\(-(R_n)\),先自减一再去取出主存地址A

- 变址寻址,记作\(X(R_0)\),指令中包含寄存器号R和形式地址D,从寄存器R中取出偏移量N和D相加得到N+D=A,从主存地址A中获取操作数I

- 基址寻址,原理同变址寻址

- 基址加变址寻址,指令中包含基准地址寄存器号\(R_B\),变址寄存器号\(R_X\),形式地址\(D\),从寄存器中依次取出数据\(B,X\),求与\(D\)的和A=B+X+D,从主存地址A中获取操作数I

- PC相对寻址,记作\(X(PC)\),指令中包含形式偏移地址X,以当前指令的下一条指令的地址作为基准地址N与X相加得到N+X=A,从主存地址A中获取操作数I

- 页面寻址,指令中包含有效地址的低位\(LOW[A]\),寄存器PC高位作为有效地址的高位\(HIGH[A]\),联合二地址求取A,从主存地址A中获取操作数I

- 堆栈寻址:从堆栈栈顶SP获取主存地址A,主存地址A中包含操作数I,SP自动递增。

-

微指令(μIR)

-

多条微指令构成一段微程序,微程序对应一条机器指令

-

微指令存放在(只读的)控制存储器(CM)中

-

微指令存储模式

- 设计思想:按照功能聚类成区,寻址方便

- 微指令后继微地址形成方式

- 增量方式(思想:顺序执行)

- 断定方式

- 面向绝对地址的转移

- 微指令编码规则

- 直接编码法

- 分段直接编码:以功能聚合度(控制同一个功能部件)为依据,将同类操作中互斥的微命令分为一组

- 分段间接编码

- 其他编码方式

-

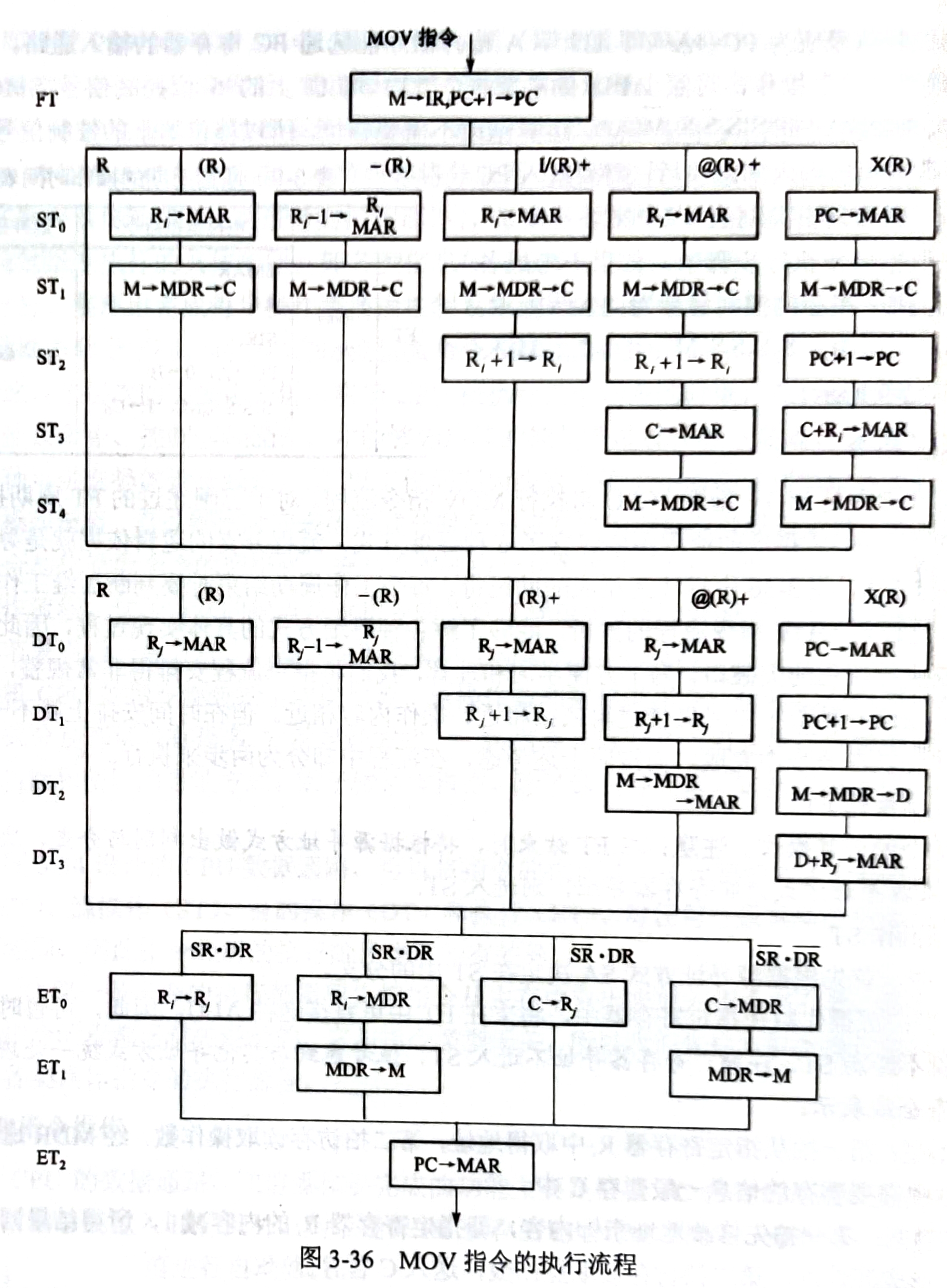

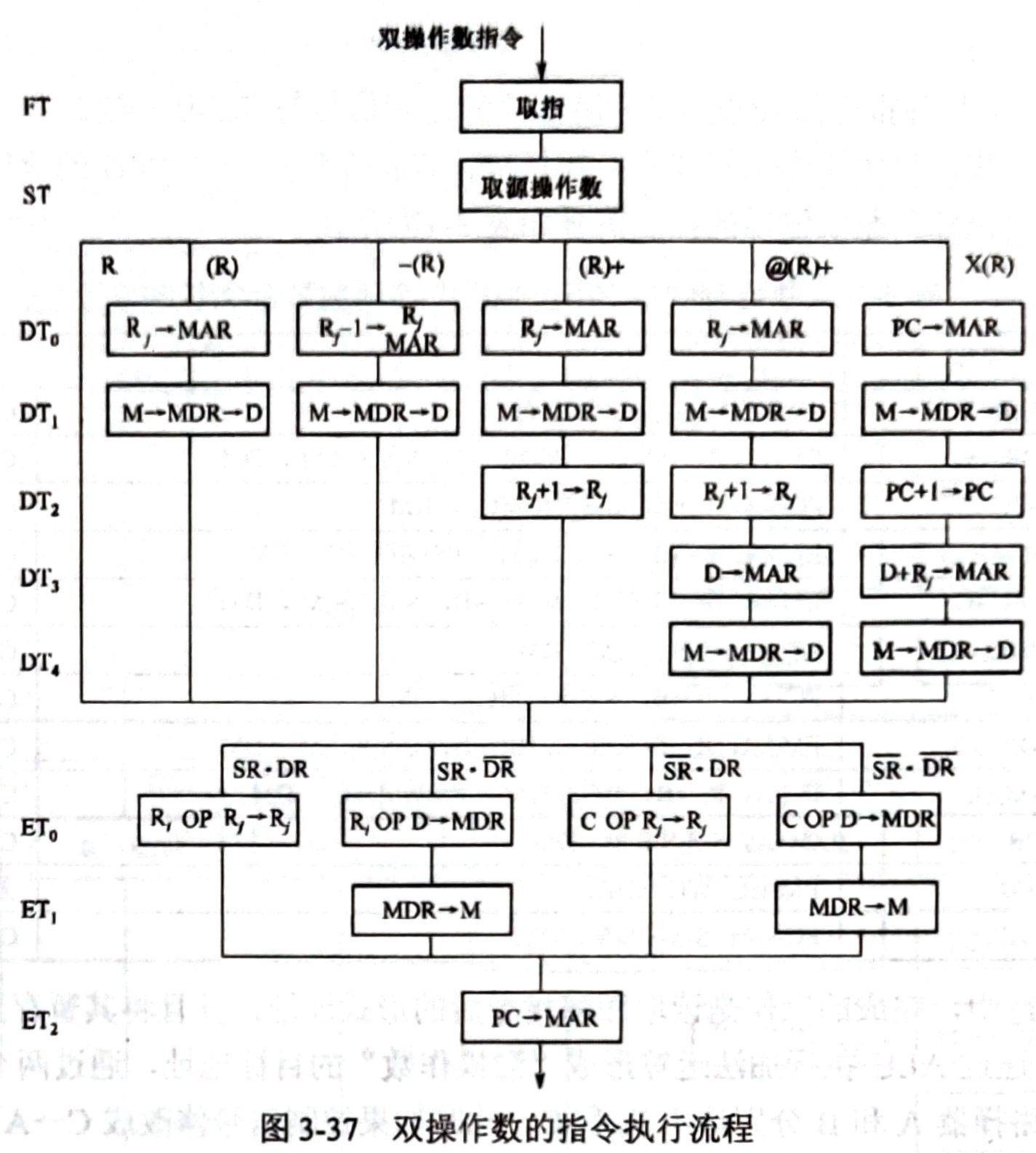

MOV和ADD的微指令流程(请参考教材140和142页)

-

第四章 存储设备

- 存储器的分类

- 主存:由CPU直接编程访问,速度快

- 外存:大容量存储器

- 高速缓冲存储器:Cache,为了解决速度匹配问题

- 虚拟存储器:扩展主存

- 按照存储机制分:

- 半导体存储器

- 静态:使用稳态电路,通电数据保存,断电数据消失。易失性

- 动态:使用电容,需要动态刷新。

- 磁表面存储器(略)

- 半导体存储器

- 联想存储器:只需要内容,不需要地址

- DRAM的刷新

- 集中刷新:在最大间隔刷新时间内集中安排刷新周期,称为死区(无法读写)

- 分散刷新:存取周期内含有刷新周期,速度慢,无死区

- 异步刷新:在刷新时间对刷新周期的商(\(T_{MAX}/m\))的时间内至少安排1次刷新操作。有上述两个刷新方式的优点

- 存储器逻辑设计(见后文)

第五章 总线和IO设备

- 总线分类:按照结构层次分:系统总线、外部总线、局部总线、片内总线

- 总线的控制方式:同步、异步(包括不互锁、半互锁、全互锁)

- 总线仲裁方式:集中式、分布式

- 总线操作的四个步骤:①主设备申请总线控制权②主设备掌握总线控制权③从设备响应④主设备释放控制权

- IO设备控制方式

- 直接程序传送模式:CPU循环等待IO设备就绪

- 中断处理模式

- 磁盘接口使用DMA执行数据传输,但是使用中断进行寻道和结束处理。

- 中断处理模式

- 产生中断的条件:①外部设备具有中断请求②CPU没有屏蔽中断源

- 中断优先级裁决:故障引发的中断→DMA请求→外部设备中断请求

- CPU响应中断请求之后,在收到更高优先级的中断请求时,可能会转去相应更高优先级的中断请求

- 中断服务程序入口地址的获取

- 向量中断:(只记软中断)向量地址=中断号n乘以4

- 非向量中断(略)

- 响应中断的条件

- 有中断信号

- 中断信号未屏蔽

- CPU处于开中断

- 无更高优先级的中断在处理

- CPU未执行停机指令

- 当前指令执行结束

- 中断相应流程

- 关中断

- 保存断点

- 获取入口地址

- 转向程序运行

- DMA:主存和IO直接存在直接的设备传输通路,数据传输不需要CPU干预

解答题

IEEE 754规格化

以20.59375为例

- 进制转换 将数字转换为二进制形式:写成20=16+4,\([20]_{DEC} = [16+4]_{DEC} = [10100]_{BIN}\),小数写成二的分式累加和\([0.59375]_{DEC} = [\frac{19}{32}]_{DEC} = [\frac{16+2+1}{32}]_{DEC} = [0.10011]_{BIN}\),得到10100.10011

- 求阶码真值 将数字左移到整数部分只有1位,得到\(1.01001011\times 2^4\),得到阶码真值为4

- 求移码 阶码使用移码表示,偏移量为127(与浮点数长度相匹配),得到\([4]_{DEC} = [100]_{BIN} \Rightarrow [4+127]_{DEC} = [10000011]_{BIN}\)

- 确定符号 确定尾数符号,即0

- 原码尾数 将尾数写作原码的形式,即010010011

- 得出结果 0100 0001 1010 0100 1100 0000 0000 0000

循环冗余校验

以有效信息1100,生成多项式1011(\(G(x) = x^3+x+1\))为例

- 左移R位 R为生成多项式的最高幂次,此处为3,因此左移三位\([110000]_{BIN}\)

- 模二除法 使用新生成的数据和生成多项式做异或除法,商的确定看余数的位数。如果余数位数为4则商1,否则商0。得到商111-,余数010

- 确定结果 余数即为CRC校验

Cache数据交互

直接映射方式

主存地址分为主存组号(7位),组内块序号(4位),块内字节序号(9位),主存组号和Cache标记匹配时命中。

冲突高,命中低,速度快

全相连映射方式

分为主存块号(11位),块内字节序号(9位)。主存块号和Cache标记匹配时命中

组相联映射方式

主存、Cache均分组,n路代表每组Cache内含n块,分成K组,则主存每K块一组。

地址分为主存组号(8位)、组内块序号(3位)、块内字节序号(9位)

寻址方式

- 立即寻址:指令中包含操作数I

- 主存直接寻址,记作\((A)\):指令中包含主存地址A,主存地址A中包含操作数I

- 寄存器直接寻址,记作\(R_n\):指令中包含寄存器号R,寄存器R中包含操作数I

- 主存间接寻址,记作\(@ A\),指令中包含主存地址A,主存地址A中包含主存地址B,主存地址B中包含操作数I

- 寄存器间接寻址,记作\((R_n)\),指令中包含寄存器号R,寄存器R中包含主存地址A,主存地址A中包含操作数I

- 自增型寄存器间址,记作\((R_n)+\),取出之后寄存器自减一

- 自减型,记作\(-(R_n)\),先自减一再去取出主存地址A

- 变址寻址,记作\(X(R_0)\),指令中包含寄存器号R和形式地址D,从寄存器R中取出偏移量N和D相加得到N+D=A,从主存地址A中获取操作数I

- 基址寻址,原理同变址寻址

- 基址加变址寻址,指令中包含基准地址寄存器号\(R_B\),变址寄存器号\(R_X\),形式地址\(D\),从寄存器中依次取出数据\(B,X\),求与\(D\)的和A=B+X+D,从主存地址A中获取操作数I

- PC相对寻址,记作\(X(PC)\),指令中包含形式偏移地址X,以当前指令的下一条指令的地址作为基准地址N与X相加得到N+X=A,从主存地址A中获取操作数I

- 页面寻址,指令中包含有效地址的低位\(LOW[A]\),寄存器PC高位作为有效地址的高位\(HIGH[A]\),联合二地址求取A,从主存地址A中获取操作数I

- 堆栈寻址

定点小数乘法

- 原码一位乘法

- 符号位:\(S_S = x_S\oplus y_S\)

- A写00.000...,注意使用双符号位,B存乘数X(的绝对值原码),C存被乘数Y

- 判断C的最低位,为1则A=A+B,为0则A右移一位

- 右移产生的溢出溢出到C中

- 循环至C的小数点在最后一位

- 将C拼接到A上得到结果

- 补码一位乘法(Booth)

- 符号位参与运算,运算数用补码表示

- A中写00.000...,C置为Y。C的双符号位删除第一位,然后末位补0

- 先求出\(B=[X]_补\)和\(-B=[-X]_补\)备用

- 判断C的最后两位

- 如果为00或者11,则A右移一位溢出到C

- 如果为01,则A=A+B,右移并溢出到C

- 如果为10,则A=A+-B,右移并溢出到C

- 循环至C的小数点进入后两位之间,执行最后一次判断之后计算,但是不右移

- 删除C的后面两位(即小数点左右的两位),然后拼到A上得到结果

指令流程

(见正文第三章)

存储芯片设计

例:某半导体存储器容量4K×8b,固化区容量2KB,拟选用2K×8b ROM芯片;工作区2KB,拟选用1K×4b RAM芯片。地址总线A15 ~ A10,双向数据总线D7 ~ D0,读写信号控制线\(R/\overline W\)

-

确定芯片数量

- 数据总线数确定存储器拼接:同时选择一个ROM芯片或者2个RAM芯片(每两个RAM芯片拼接为1组,视作1K×8b)

- 优先满足可以确定的容量大小:固化区2KB×8,因此选择ROM芯片一个

- 其次满足总容量:工作区2KB×8,因此选择四个RAM芯片

-

分配地址

- 首先确定地址线条数:存储器容量4K,因此需要\(\log_2{(1024\times4)}=12\)根地址线,多余的地址线恒为零(即A15~A12恒为零)

- 其次确定各芯片的地址线需求,即确定片内地址:以2K ROM芯片为例,需要\(\log_2{(1024\times 2)}=11\)根地址线,因此ROM芯片的片内地址为A10~A0,余类推

-

按照序号分配片选信号(依次确定\(\overline{CS_n}\)或者\(CS_n\)即可)

-

确定片选逻辑

-

思想:当片选逻辑和片选信号匹配的时候选中当前芯片

-

片选逻辑用于区别读取的存储单元,因此由地址线中不包含片内地址线的部分构成

-

ROM片内地址为10位,余出一位\(A_{11}\),此位为低位时选中ROM

-

RAM片内地址为9位,余出两位\(A_{11},A_{10}\),此时组合为10时选中其中一块组合RAM,组合为11时选中另一块。请注意,此处的A11不能选中为0,以免和ROM冲突

-

组合为0时,片选逻辑要加上横线

-

片选逻辑要带上整个横线

-

-

绘制逻辑结构图

-

绘制芯片:以矩形表示芯片,在其中注明型号(例如2422)或者存储属性(例如RAM 2K × 8)

-

绘制数据线(在芯片上方,下同):根据芯片位数匹配绘制对应的双向箭头线(例如8位数据线,但是只有4位芯片,则要绘制两条数据线)

在数据线的一段绘制一条短斜线,标识线数,后同

从芯片绘制出一根箭头指向数据线

- 只读芯片只绘制到数据线的箭头

- 可写芯片绘制成双向箭头

-

绘制R/W信号线,并连接到各芯片,接驳处打点。对于只读芯片不需要连接

-

绘制地址线(在芯片下方),从地址线引出(即接驳)单向箭头线指向芯片,在其上用短斜线标识地址范围

-

绘制片选信号

先在各芯片的最下方绘制片选逻辑线,标明非条件(例如\(A_{11}\)和\(\overline {A_{12}}\))

逻辑线汇总到and逻辑门,绘制为矩形。

如果片选逻辑整体带有非符号(即上方的横杠),则在逻辑门上方绘制圆形标识非

从逻辑门引出一根线连接到芯片,在旁边标识片选信号

-

作者发布、转载的任何文章中所涉及的技术、思路、工具仅供以安全目的的学习交流,并严格遵守《中华人民共和国网络安全法》、《中华人民共和国数据安全法》等网络安全法律法规。

任何人不得将技术用于非法用途、盈利用途。否则作者不对未许可的用途承担任何后果。

本文遵守CC BY-NC-SA 3.0协议,您可以在任何媒介以任何形式复制、发行本作品,或者修改、转换或以本作品为基础进行创作

您必须给出适当的署名,提供指向本文的链接,同时标明是否(对原文)作了修改。您可以用任何合理的方式来署名,但是不得以任何方式暗示作者为您或您的使用背书。

同时,本文不得用于商业目的。混合、转换、基于本作品进行创作,必须基于同一协议(CC BY-NC-SA 3.0)分发。

如有问题, 可发送邮件咨询.

浙公网安备 33010602011771号

浙公网安备 33010602011771号