cadence学习一------>介绍

Allegro常用组件:

1.orcad capture cis------>>原理图

2.PCB editor----->>PCB

3.PAD designer------->>PAD

orcad capture cis------>>原理图

建立文件

工具栏

其中:

off-page connector 端口连接符号 在同一层次电路原理图中,同一页面或不同页面中,名称相同的端口连接符号在电气连接上是相连的。

net alias 网络标号,在原理图中此名称相同,并且此符号是在同一页面中,在电气连接上才是相连的。

绘制总线时格式:

DATA[0..3] DATA[0-3] DATA[0:3]表示一样的总线

注意:总线名称的最后一个字符不要采用数字,防止在生成网络表时产生问题

常用操作:

place bus----place 页面连接符-----place bus entry------place net alias

place part中添加元件库 libraries下虚线框按钮

自带常用库介绍:

| AMPLIFIER.OLB | 共182个零件,存放模拟放大器IC,如CA3280,TL027C,EL4093 |

| ARITHMETIC.OLB | 逻辑运算IC,如TC4032B,74LS85等。 |

| ATOD.OLB | A/D转换IC,如ADC0804,TC7109等 |

| BUS DRIVERTRANSCEIVER.OLB | 驱动IC,如74LS244,74LS373等数字IC。 |

| CAPSYM.OLB | 电源,地,输入输出口,标题栏等。 |

| CONNECTOR.OLB | 连接器,排针,如4 HEADER,CON AT62,RCA JACK等。 |

| COUNTER.OLB | 计数器IC,如74LS90,CD4040B。 |

| DISCRETE.OLB | 分立式元件,如电阻,电容,电感,开关,变压器等常用零件。 |

| DRAM.OLB | 动态存储器 |

| ELECTRO MECHANICAL.OLB | 马达,断路器等电机类元件。 |

| FIFO.OLB | fifo |

| FILTRE.OLB | 滤波器 |

| FPGA.OLB | fpga |

| GATE.OLB | 门 |

| LATCH.OLB | 锁存器 |

| LINE DRIVER RECEIVER.OLB | 线性驱动接收器 |

| MECHANICAL.OLB | 存放机构图件 |

| MICROCONTROLLER.OLB | 微控制器 |

| MICRO PROCESSOR.OLB | 微处理器 |

| MISC.OLB | 存放杂项图件,如电表(METER MA) |

| MISC2.OLB | 存放杂项图件 |

| MISCLINEAR.OLB | 存放线性杂项图件 |

| MISCMEMORY.OLB | memory |

| MISCPOWER.OLB | power |

| MUXDECODER.OLB | 解码器 |

| OPAMP.OLB | 运放 |

| PASSIVEFILTER.OLB | 被动式滤波器 |

| PLD.OLB | 可编程逻辑器件 |

| PROM.OLB | PROM |

| REGULATOR.OLB | 稳压芯片 |

| SHIFTREGISTER.OLB | 移位寄存器 |

| SRAM.OLB | SRAM |

| TRANSISTOR.OLB | 晶体管 |

原理图基本操作:

1、 Place Part(P):放置元件

2、 Place wire(W):连接相连的pin脚

3、 Place Auto wire:自动连线

4、 Place bus(B):总线连接

5、 Place junction(J):交叉点连接,两条wire相交有两种连接关系:连或不连,加J为连

6、 Place bus entry(E):可以理解为总线入口,有bus必有entry

7、 Place net alias(N):相当于wire,用于连接距离远的Pin脚,仅限于同一page电气连接

8、 Place power(F):放置电源

9、 Place ground(G):放置地

10、 Place off-page connector:类似alias,但alias仅用于同一页面,而off-page用于不同页面之间的电气连接

11、 Place no connect(X):用于无电气连接的pin脚,不放会报错

12、 Place text(T):放置文本

常用操作:

1、按住Ctrl滚动鼠标滚轮放大缩小原理图(以鼠标指针为中心);直接滚动鼠标滚轮上下移动;按住Shift滚动左右移动

2、改变原理图尺寸大小:options->Schematic Page Properties->Page Size

3、旋转器件:放置器件前直接按R可旋转,放置后选中按R旋转

4、选中单个或者多个器件,按住Ctrl+鼠标左键,拖动鼠标,可复制所选器件

5、 连线时改变连线角度需先按shift键

6、元件镜像:选定后V键(垂直)和H键(水平)

7、鼠标右键选End mode结束当前操作

8、连线时,终点如不是管脚,双击结束

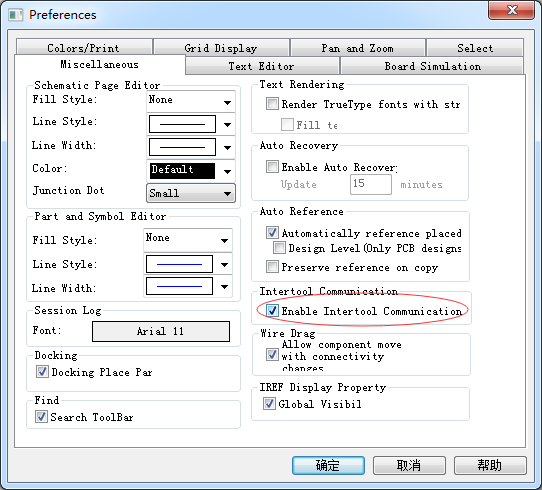

9、管脚之间不要直接相连,通过线连接以防出错(软件设置管脚之间不允许连接的方法:

Options/Preferences->Miscellaneous->Wire Drag打钩去掉)

后期处理:、

1、 浏览原理图:选中 .dsn , edit->browse 可以浏览parts、nets等,主要检查是否有漏掉的信息,双击可以打开原理图并高亮显示所选内容

2、 元件替换和更新:右键需要修改的元件,选择Replace cache或Update Cache

Replace cache:用于替换

Update Cache:用于更新

3、 Cleanup Cache:右键Design Cache选择Cleanup Cache用于检测Design Cache与原理图是否一致,并删除多余的内容

4、 移动:默认连线与移动元件一同移动,按住Alt 移动仅元件移动

5、 自动编号:右键.dsn 选Annotate 。首先选择Reset part references to ?进行复位,然后选择Unconditional reference update进行编号。

6、 添加footprint(保证与器件封装名称一致):

a、双击元件,找到PCB footprint,右键选择Edit,添加封装名称即可(右键选择Pivot可以切换显示方式)

b、按住Ctrl选择多个元件,右键选择Edit Properties进行添加

c、常用元件可通过元件库添加PCB封装

d、批量添加:右键Page 选择edit Object Properties

7、点击Pivot可以改变视图模式,可多选统一编辑

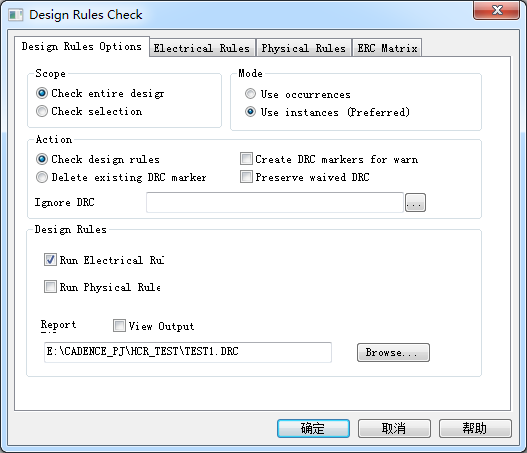

8、DRC检查:Tools->Design Rules Check

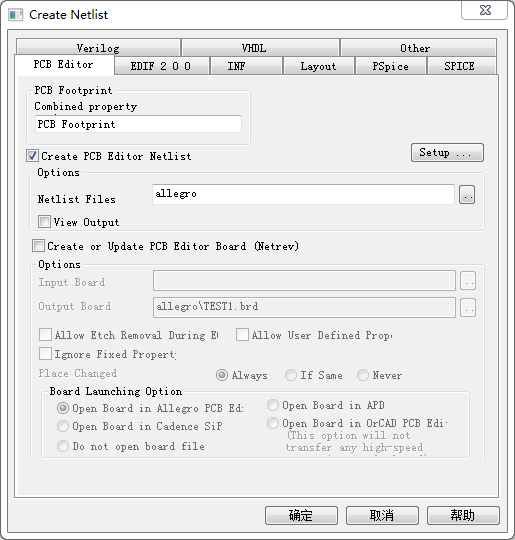

9、生成netlist:Tools->Create Nelist ,选择PCB Editor确认

10、生成BOM:Reports->CIS Bill of Materials

具体细节:

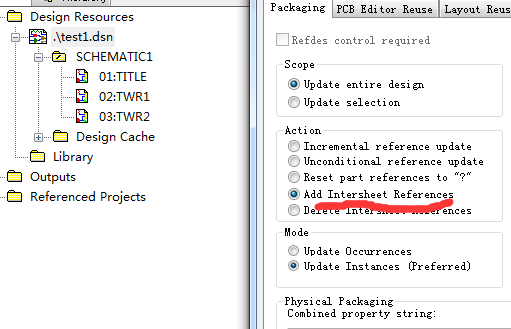

1.当有多个页面时,intersheet references的使用?

添加Intersheet references在页面连接符off page connector 后加上图纸页码编号,方便查找相关对象

offset relative to port 页面编号相对端口放置

offset relative to port name 页面编号相对端口名放置

reset positions 此处设置相对放置的位置

设置好后。页面连接符后会加上图纸页码编号

2.DRC检查

dsn----->>toors------>design rules check------->

3.生成网络表

网络表是原理图和PCB之间的桥梁

dsn------>tools------->create netlist

若网络表无错误,默认在dsn文件夹中将生成3个文件,pstxnet pstxprt pstchip

生成网表,常见错误:

1.封装属性(PCB Footprint)没有填写

2.PCB Footprint中包含不规范字符

3.原理图符号中引脚名重复

4.器件符号重复

5.原理图页码重复

可以通过菜单 Windows-Session Log窗口提示信息修改

4。交互设置

在Capture中,通过菜单Options-Preferences选择Miscellaneous选项卡

勾选标记处enable Intertool Communication即可