故障模型和故障建模

1 什么是故障模型

芯片在制造时难免出现各种问题,芯片制造的缺陷可能导致芯片出现非预期的行为。故障模型 Fault Model 是在开发、制造或者使用芯片时,描述芯片某处错误行为的抽象表示。通过故障模型,设计者或用户能够有效地得知发生错误的信息。

图1:芯片中的制造缺陷

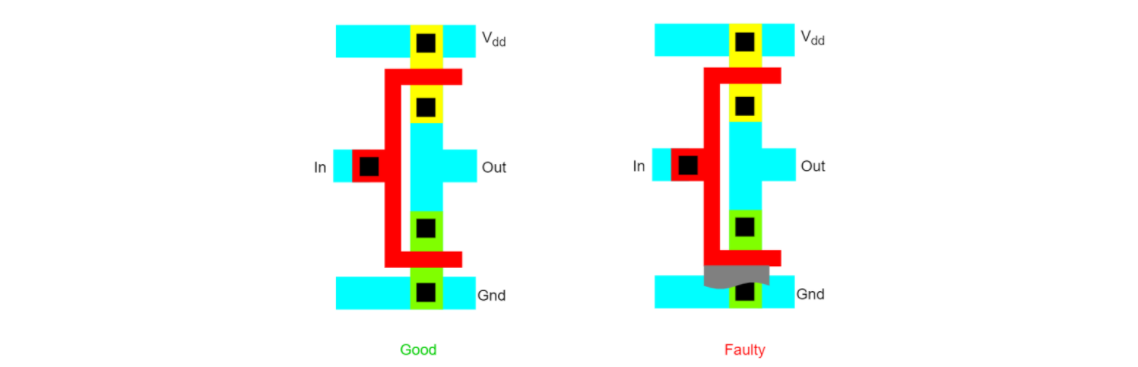

下面用一个例子来解释制造时的缺陷是如何导致电路中的故障:

上图是一个 Physical Level 的 CMOS 反相器。在制造时,由于腐刻的缺陷 defect,正常电路(红色)被多延长了一块(灰色),导致输入端与 GND 短路,值永远为0。这个缺陷可以用(门级)故障模型 Fault Modeling表示,此处为一个Stuck-at-0 Fault。因此,这个反相器的输出会保持为1,即输出端出现了Stuck-at-1 Fault。这部分电路出现了Failure。

注意,故障模型不是给故障归类,而是给故障导致的行为归类。因为故障可以层出不穷,但是故障导致的行为就那么些。对行为进行归类是故障模型的精髓。

2 使用故障模型的好处

如上文所述,IC生产过程中存在各种各样的缺陷,会导致各种各样的错误。对每一种故障归类是非常困难的,但是将晶体管/电路的故障抽象为电路输入输出的逻辑错误,会带来若干好处:

- 减少需要考虑的情况

- 便于针对性地生成测试用例和故障模拟

- 便于评估错误覆盖率,比较 ATPG 生成的测试集效果

3 抽象等级

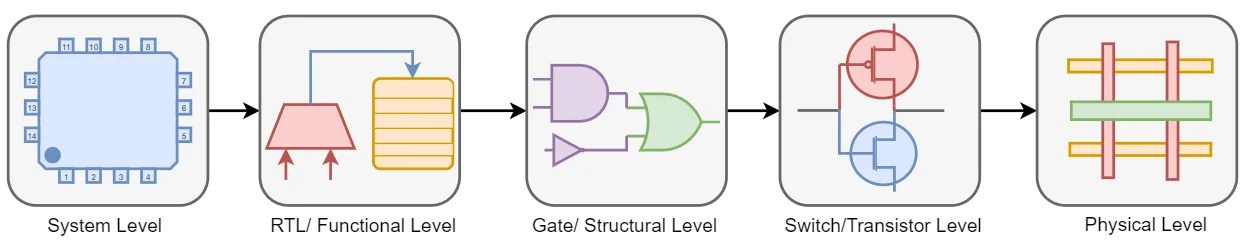

VLSI芯片有多种抽象级别:

译者注:作为软件专业的学生,“抽象”这个词可以说是令人感到振奋。抽象是一个伟大的思想,理解抽象可以帮助你理解工程领域的各种奇妙构思,甚至了解人类社会运行的一些规律。。。

3.1 Physical Level

如上图所示,抽象等级越低(向右),参与故障建模的单元越多,故障模型会变得更加具体,错误建模更加困难。例如,晶体管(in Transistor Level)的数量要大于功能模块(in Functional Level)的数量,出错时分析起来也就更麻烦。此外,高等级的故障在 Physical Level 变得局部化,并且可以相互等价,即一个低级故障可能映射为多种高级故障,这也增加了在 Physical Level 抽象的难度。

Physical Level 的故障跟制造工艺紧密贴合,并不具有普适性(比如CMOS的模型无法与TTL模型通用)。

3.2 System Level

我们再来看最高等级的抽象,System Level 抽象。这一级的故障模型非常容易理解,因为我们不需要考虑很多细节,但难以对出现的问题进行准确定位。假某块8k内存中出现了一个错误,在 Physical Level,我们要明确错误的类型,并在8192个可能出错的位置进行寻找。但是在 System Level,我们可以直接说这个芯片就是坏掉了。由于这种模型过于简单,不利于生产的质量改进,因此工业界很少直接使用这一级别的故障模型。

综上,我们看到了抽象等级高低的两种极端抽象,这两种模型在实践中均有自己的不足。因此,常用的故障模型集中在 Gate Level, Switch Level, 和 Functional Level 这些抽象等级上。

3.3 Functional Level

如之前所提到的,高级抽象的故障可能无法直接与 Physical Level 的故障相对应,一个高级别的故障可能由多种低级的故障导致,这使得我们难以更进一步地定位问题的所在。然鹅,在 Functional Level, Memory Fault Mode 体现了本级抽象的优越性。

-

Memory Fault Model

存储器是数字系统设计的基本组成部分。每个存储位置上的存储单元都非常相似。因此专门为存储器设计了一类特殊的故障模型。这类模型就叫做 Memory Fault Model,可分为如下几种类型:

- Memory Stuck-at Faults

- Memory Transition Faults

- Memory Coupling Faults

- Address Decoder Faults

3.4 Structural/Gate Level Fault Model

在 Structural Level 抽象上,电路被转化为门和FF表示的网表结构。我们在本层的分析有这样的假设:网表中的门不会出现故障,仅有互连线会出现故障。(门当然会出错,但是在 Structural Level 抽象中,门的故障被视为互连线的故障。所以我们看到测试相关的 paper 中,对 fault 的描述都是“某条 line 上的 fault”)

门级故障模型的目标是,确保互连线能够正确传输门发出的0/1激励。常见的门级故障模型有:

-

Stuck-at Faults

Stuck-at 故障是最常用的故障模型。我们假设某些互连线出现了问题,导致线上的电平永远固定在0或者1(s-a-0, Stuck-at 0 和 s-a-1, Stuck-at 1)。Stuck-at故障可进一步分为:

-

Single Stuck-at faults

在任何时候,电路中只会有一跟导线出现故障。如果电路中有n条互连线,那么我们的 fault list(fault 的集合)的容量为 2n。Single Stuck-at fault model 也是工业界中最常用的故障模型。

-

Multiple Stuck-at faults

在任何时候,电路中任意导线都可能存在故障。如果电路中有n条互连线,那么我们的 fault list 的容量为 3^n -1。

在实践中,只考虑 Single Stuck-at faults 可以极大地简化测试向量,并可以达到非常好的测试准确性。根据一项研究(Schertz, D. (1969). ON THE REPRESENTATION OF DIGITAL FAULTS.),能够完全检出 Single Stuck-at faults 的测试向量可以同时检出超过95%的 Multiple Stuck-at faults。这种故障模型的优势在于能够屏蔽芯片制造技术这样的细节,抽象出的电路信息足够用于生成测试向量。

-

-

Bridging Faults

当电路中的两条或更多条互联线意外连接在一起时,就会发生 Bridging Fault。

-

Delay Faults

门的引脚对特定刺激集以及特定转换的转换响应太慢。可进一步细分为 Path delay fault 和 Transition delay fault。

3.5 Switch Level Fault Model

Switch Level 抽象在晶体管的层面分析电路,例如 CMOS 门的网表。在该模型中,MOS晶体管被认为是一种理想的开关。根据晶体管导通与否的情况,有两种常见的故障模型:

- Stuck-Short Fault Model

- Stuck-Open Fault Model

4 小结

本文中,我们讨论了VLSI电路中的物理缺陷是如何被各级故障模型表示的。在芯片生产中,对所有晶体管进行检测是不现实的,但通过故障模型设计EDA和检测工具,我们可以高效地找到出错的芯片,定位问题,而不用去纠结硬件的实现细节,从而快速开发芯片。