DFT 综述

1 什么是DFT?为什么需要DFT?

1.1 IC制造的挑战

随着集成电路制程的发展,7nm、5nm甚至3nm的芯片开始出现。加工精度的提升放大了制造出错的可能性,给制造商和消费者带来了更大的挑战:

-

密度问题 Density Issue:制造精度的提升使得我们可以制造更小、更细的晶体管和导线,增加元件排布的密度。这种现象可能导致导线之间发生接触,甚至直接断掉,从而发生故障 (fault);

-

软件问题 Software Issue:EDA的compiler工具可能会出错;

-

特殊应用领域要求 Application Issue: 某些领域(如:航空,医疗)可能会在极端的温度、压力等条件下工作,并要求万无一失。对与这些领域的芯片,要提出非常application-specific的测试内容来避免出错;

-

可维护性 Maintenance Issue:在芯片发生故障时,我们如何在精细且规模庞大的芯片上,定位到错误的发生点,从而修正错误;

-

商业损失 Business Issue:芯片出错可能会给使用芯片的公司带来生命财产损失;

因此,芯片测试是当今芯片制造中至关重要的部分。

1.2 应对挑战的方法 -- DFT

对于如今的芯片规模,想要通过穷举的方法进行测试在时间上和成本上都是不可接受的。一个广泛采用的测试方法是:在芯片中添加一些新的特性便于测试,这种方法叫做DFT,全称Design for Test (Testability)。

DFT会在芯片中额外添加一些电路,这些电路可以让我们单独对某个或某些模块进行操作和观察,从而便于我们定位问题,测试芯片的正确性。

1.3 DFT的作用

1.3.1 测试时序逻辑

总所周知,组合逻辑的输出仅取决于输入。而时序逻辑是一个由触发器决定的有限状态机,我们无法仅凭输入来确定输出。因此,想要测试时序逻辑,我们必须先设定这个有限状态机的初始状态(通过DFT),才可以仅通过输入值测试芯片。

1.3.2 提升芯片制造水平

-

提前发现有缺陷的模块

-

监视、改进生产流程

1.4 DFT可以彻底消灭故障吗

想啥呢。。不存在的。

即使是交付到用户手里的芯片都无法做到fault free。包括你现在用的CPU都有可能出错。不信的话可以给你的CPU极限超频试试。

为了尽可能地减少故障,提供更好质量的芯片,在芯片制造流程中还有一道工序:验证 Verification

2 验证和测试 Testing 的区别

| Verification | Testing |

|---|---|

| Verifies correctness of the design. | Verifies correctness of the manufactured hardware. |

| Performed by simulation, hardware emulation, or formal methods. | Two-part process: Test generation: software process executed once during design. Performed only once. Test application: electrical tests applied to hardware. Performed multiple times. |

| Performed once prior to manufacturing. | Test application is performed on every manufactured device. |

| Responsible for the quality of design. | Responsible for the quality of devices. |

3 术语

| Terminologies | 参考翻译 | 解释 |

|---|---|---|

| Testing | 测试 | 对系统(模块)进行试验,来分析和验证其行为的正确性 |

| Diagnosis | 诊断 | 定位电路错误的过程 |

| Defect | 缺陷 | 特指硬件/电器系统的缺陷 |

| Fault (model) | 故障(模型) | 缺陷的抽象级表示,用与描述缺陷 |

| Error | 错误 | 由于缺陷导致电路/门输出了错误的值 |

| Failure | 失败 | 由于缺陷导致系统的无法恢复或逆转的故障 |

| Fault Coverage | 故障覆盖率 | 能测试出的fault占总fault的比例 |

| Defect Level | 缺陷等级 | 出现fault的芯片占比 |

4 测试的层次

-

芯片级 Chip-level 当芯片被生产出来时的测试

-

板卡级 Board-level 当芯片被集成在板卡上时的测试

-

系统级 System-level 当多个办卡集合为完整系统时的测试

测试的级别提升,会导致诊断复杂度的增加和数十倍的检测成本提升。

5 IC制造中故障的来源及分类

故障可能源自于以下几个方面:

-

生产流程 like missing contact windows, parasitic transistors, etc.

-

材料 like cracks or imperfections in the substrate, surface impurities, etc.

-

老化 caused by Dielectric breakdown, electron migration, etc.

-

包装 like Contact degradation, disconnection, etc.

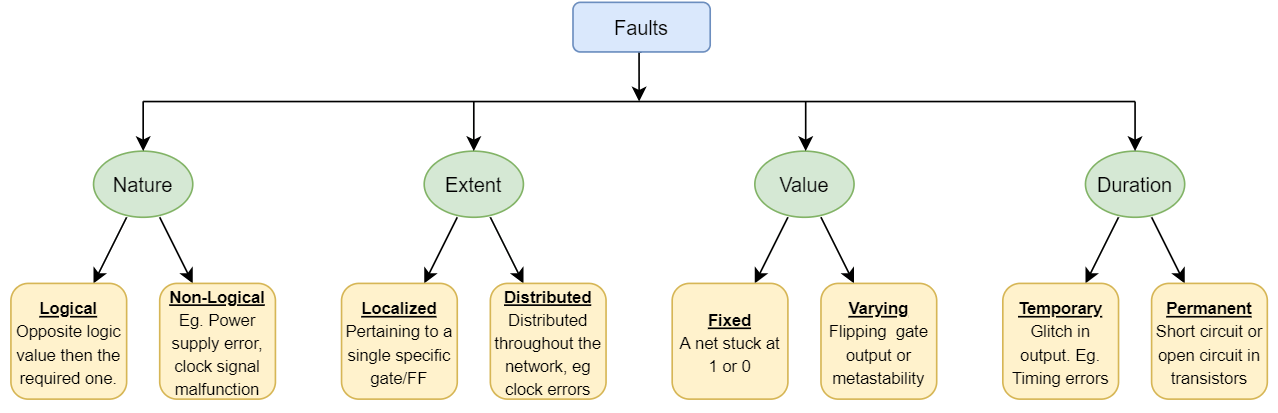

故障可大致被分为以下几类

6 DFT技术

DFT主要分为以下两类

-

Ad-hoc techniques

-

Structured techniques

7 小结

本文简单介绍了DFT (Design for Test) 的概念,对一些术语进行了明确。重点是,在IC设计中的很多环节多可能出错,而芯片出错的后果往往会很严重。为了减少这些错误的发生,我们引入了DFT来更好地完成芯片测试的工作。