【原创】systemverilog完整环境搭建流程之一rtl源代码

我是一个验证,不是设计,设计的代码我处理方式是不求甚解,知道是要干什么就行,对我的要求别太高。。。

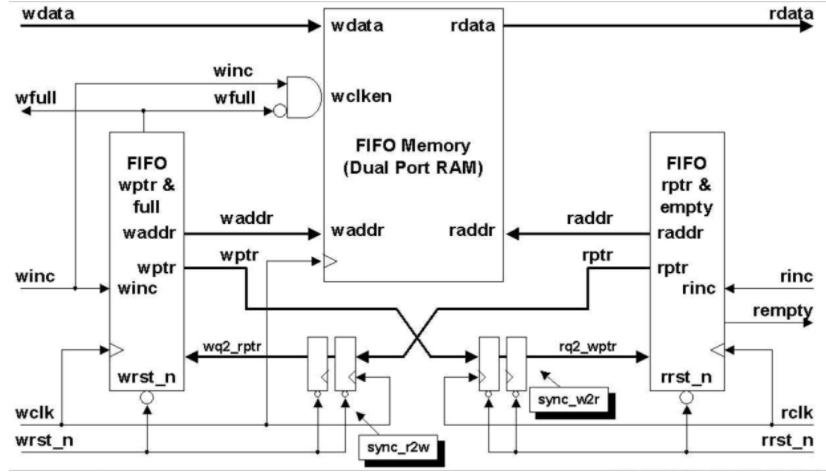

以下RTL代码是基于FIFO的,所以我们要先明白FIFO的原理:

FIFO是异步数据传输时经常使用的存储器。该存储器的特点是数据先进先出。多位宽数据的异步传输问题,基本都可以使用FIFO处理。

工作流程:

复位之后,再写时钟和状态信号控制下,数据写入FIFO中。RAM的写地址从0开始,每写一次数据写地址指针加一,指向下一个存储单元。

当FIFO写满后,数据不能写入,否则数据被cover and lost.

当FIFO为非空,或满状态,在读写时钟和状态信号的控制下,可以将数据从FIFO中读出。每读一次数据读地址加一,指向下一个存储单元。当FIFO读空后,就不能再读数据。

FIFO数据为非空、或满状态时,在读时钟和状态信号的控制下,可以将数据从FIFO中读出。RAM的读地址从0开始,每读一次数据读地址指针加一,指向下一个存储单元。当FIFO读空后,就不能再读数据,否则读出的数据将是错误的。

读写时刻,

只要FIFO中数据为非满状态,就可以进行写操作;如果FIFO为满状态,则禁止再写数据。

关于读时刻,只要 FIFO 中数据为非空状态,就可以进行读操作;如果 FIFO 为空状态,则禁止再读数据。

不管怎样,一段正常读写 FIFO 的时间段,如果读写同时进行,则要求写 FIFO 速率不能大于读速率。

在fifo module下,

输入:

read : read_in read_clock read_rst ;

write : write_in write_clock write_rst;

输出:

read : read_data;read_empty;

write : write_full;

根据变量名,相信都能看懂代表什么意思。

声明地址变量:write_addr;read_addr;

声明指针变量:write_ptr;read_ptr;

wq2_rptr和rq2_wptr 寄存器连接输出

封装了同步模块sync_r2w和sync_rq2 module;(只有上层变量与下层变量连接,没有流向与SIZE)

封装了fifo_memory;

封装了读、写指针的状态触发标志。

- 在我的理解中,做验证的,看懂了top层接口,接下来该看一下代码的逻辑部分

memory层:

例化vendor_ram;描述读指针,写指针和地址及数据的过程,逻辑上来说24行wclk来,判断25行,写指针改写。

声明一个5位reg类型rbin; 状态暂存

声明一个5位wire类型,rgraymext,binnext; 值传递

13-15行,读指针,使用二进制访问地址内存,16行,empty触发盘

两个always:读指针和地址传值与状态的处理。

-

sync_r2w和sync_w2r的存在只是为了消除亚稳态,代码简单,就不放出来了

-

写指针,使用二进制访问地址内存,16行,full触发盘

两个always:写指针和地址传值与状态的处理。

--------------------------------------------分割线-------------------------------------

确定verification Objective

分功能类,接口类,场景类、性能类和异常类这几个方面确定验证点

根据时钟,复位,power,寄存器访问,功能port。

再搭建验证换环境。

下一P:systemverilog完整环境搭建流程之————基本验证环境搭建