ESP32学习day2

以太网通信常用的方式:

(1)使用转换协议模块,将以太网转为uart,spi等方式通信

(2)使用直连模块,直接使用RMII协议链接以太网,这个模块一般就是一个PHY芯片,加一个输入网络接口和一排输出排针组成。

PHY我昨天已经了解了,端口物理层,PHY连接一个数据链路层的设备(MAC)到一个物理媒介,如光纤。(既:单片机设备或电脑设备-PHY-网线);PHY可以发送和接收以太网的数据帧(frame)。它通常缺乏NIC(网络接口控制器)。

还有一个半双工或全双工工作模式:

这是什么意思呢?

- 全双工(full-duplex)的系统允许两台设备间同时进行双向数据传输。

- 半双工(half-duplex)的系统允许两台设备之间的双向数据传输,但不能同时进行。同一时间只允许一设备传送资料,若另一设备要传送资料,需等原来传送资料的设备传送完成后再处理。

另外,我阅读了esp-idf官方文档的英文版,(CSMA/CD)协议/接口。目的MAC地址(DA),源MAC地址(SA)、类型/长度字段、数据有效载荷、可选填充字段和循环冗余检查(CRC)。

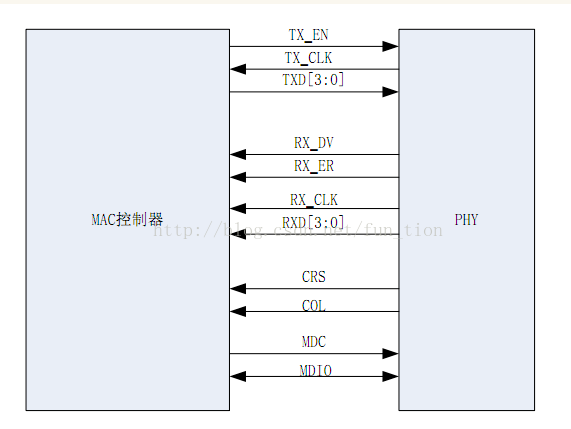

在此之前,我需要自己先理解一下MII,RMII接口 MII,独立于介质的接口(MII)用于MAC与外界的PHY互联。

MII的信号线:

MII_TX_CLK:发送数据使用的时钟信号,对于10M位/s的数据传输,此时钟为2.5MHz,对于100M位/s的数据传输,此时钟为25MHz。

MII_RX_CLK:接收数据使用的时钟信号,对于10M位/s的数据传输,此时钟为2.5MHz,对于100M位/s的数据传输,此时钟为25MHz。

MII_TX_EN:传输使能信号,此信号必需与数据前导符的起始位同步出现,并在传输完毕前一直保持。

MII_TXD[3:0]:发送数据线,每次传输4位数据,数据在MII_TX_EN信号有效时有效。MII_TXD[0]是数据的最低位,MII_TXD[3]是最高位。当MII_TX_EN信号无效时,PHY忽略传输的数据。

MII_CRS:载波侦听信号,仅工作在半双工模式下,由PHY控制,当发送或接收的介质非空闲时,使能此信号。 PHY必需保证MII_CRS信号在发生冲突的整个时间段内都保持有效,不需要此信号与发送/接收的时钟同步。

MII_COL:冲突检测信号,仅工作在半双工模式下,由PHY控制,当检测到介质发生冲突时,使能此信号,并且在整个冲突的持续时间内,保持此信号有效。此信号不需要和发送/接收的时钟同步。

MII_RXD[3:0]:接收数据线,每次接收4位数据,数据在MII_RX_DV信号有效时有效。MII_RXD[0]是数据的最低位,MII_RXD[3]是最高位。当 MII_RX_EN无效,而MII_RX_ER有效时,MII_RXD[3:0]数据值代表特定的信息(请参考表194)。

MII_RX_DV:接收数据使能信号,由PHY控制,当PHY准备好数据供MAC接收时,使能该信号。此信号必需和帧数据的首位同步出现,并保持有效直到数据传输完成。在传送最后4位数据后的第一个时钟之前,此信号必需变为无效状态。为了正确的接收一个帧,有效电平不能滞后于数据线上的SFD位出现。

MII_RX_ER:接收出错信号,保持一个或多个时钟周期(MII_RX_CLK)的有效状态,表明MAC在接收过程中检测到错误。具体错误原因需配合MII_RX_DV的状态及MII_RXD[3:0]的数据值。

MII需要16个数据和控制信号引脚

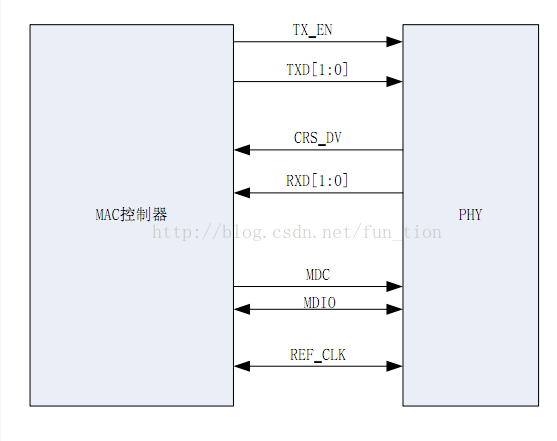

RMII信号线:

时钟信号需要提高到50MHz。

MAC和外部以太网PHY需要使用同样的时钟源

使用2位宽数据收发。

RMII时钟源:

通过将相同的时钟源接到MAC和以太网PHY的REF_CLK引脚保证两者时钟源的同步。可以通过外部的50MHZ信号或者GD32F107xx微控制器的MCO引脚提供这一时钟。当时钟来源MCO引脚时需配置合适的PLL,保证MCO引脚输出的时钟为50MHZ.

我的板子上的8720A没有外部晶振,需要从ESP32产生晶振发送给8720A. 另外,总结一下,我采用RMII接口,PHY的时钟频率要求50M,要与MAC层时钟保持一致,通常从MAC层获取该时钟源。

现在我去了解8720A,这个芯片仅支持RMII模式,需要50MHz的外部时钟源,输入到REF_clk.

我板子上没有这个输入引脚,时钟信号是从ESP过来的,可以设置IO17或IO0为clkin输入引脚,对应ESP需要配置这两个引脚。

硬件默认设置8720A为1

我板子上的MODE2接的是RMII_CRS_DV,MODE1接的是RMII_RXD0,MODE0接的是RMII_RXD1

SMI(MDC/MDIO)

MSDIO是一个PHY的管理接口,用来读写PHYregister,

MII用于链接MAC和PHY,包含两种信号接口:

1: 一个数据接口用于MAC和PHY之间接收和发送以太网帧数据。

2: 一个PHY管理接口,即MDIO,用于读写每个PHY的控制寄存器和状态寄存器,以达到控制PHY行为和监控PHY状态的目的。

8720A的寄存器,

| 0 | Basic Control Register | Basic |

|---|---|---|

| 1 | Basic Status Register | Basic |

| 2 | PHY Identifier 1 | Extended |

| 3 | PHY Identifier 2 | Extended |

| 4 | Auto-Negotiation Advertisement Register | Extended |

| 5 | Auto-Negotiation Link Partner Ability Register | Extended |

| 6 | Auto-Negotiation Expansion Register | Extended |

| 17 | Mode Control/Status Register | Vendor-specific |

| 18 | Special Modes | Vendor-specific |

| 26 | Symbol Error Counter Register | Vendor-specific |

| 27 | Control / Status Indication Register | Vendor-specific |

| 29 | Interrupt Source Register | Vendor-specific |

| 30 | Interrupt Mask Register | Vendor-specific |

| 31 | PHY Special Control/Status Register | Vendor-specific |

| Basic 是 IEEE802.3 要求的,R0 是基本控制寄存器,其位 15为 Soft Reset 位,向该位写 1启动LAN8720A 软件复位,还包括速度、自适应、低功耗等等功能设置。R1 是基本状态寄存器。 |

ESP32(GPIO17)提供时钟给LAN8720,最合适用于LAN8720

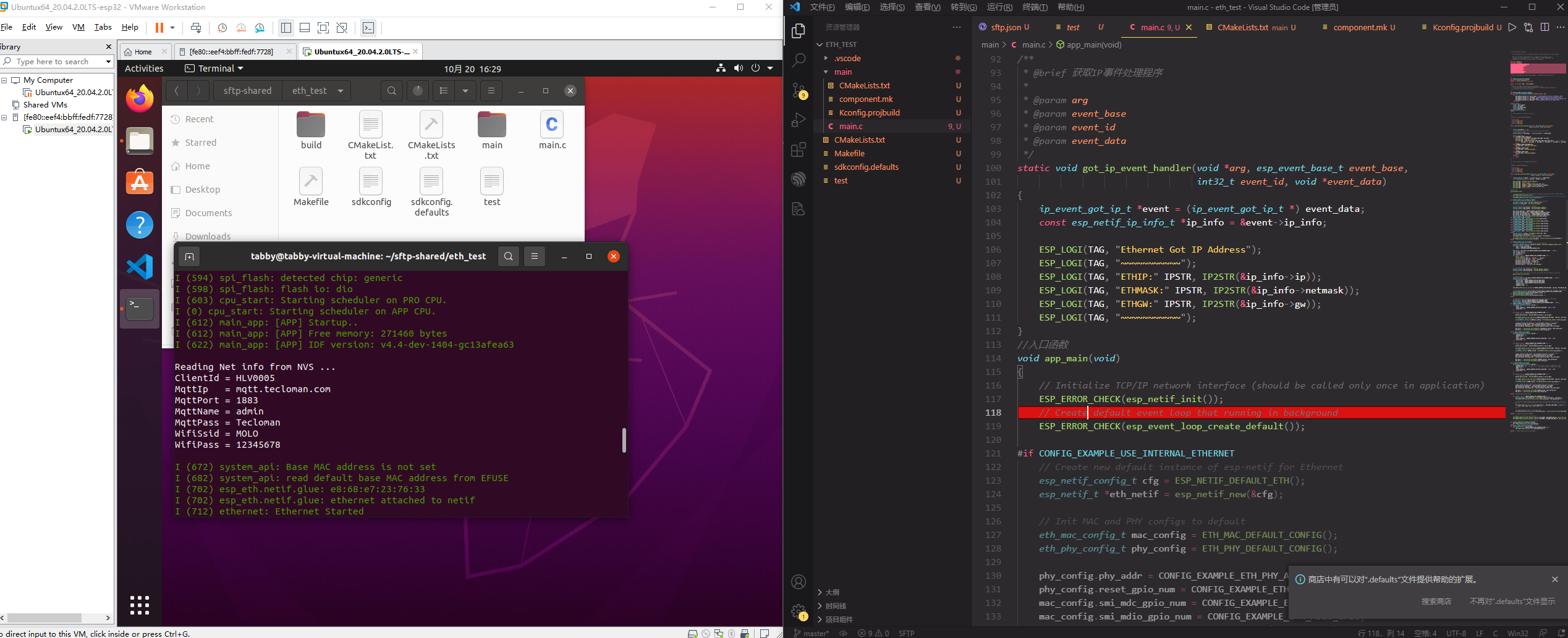

现在预备知识基本已经看完了,接下来要做的就是先把例程在idf中跑起来

idf已经把esp basic ethemet例程跑起来了,现在的问题是输出我看不懂,我应该如何改代码?换句话说明天的任务还是看懂代码?但这个工程量巨大,我怕我领导等不了我。

还有就是espidf menuconfig 的 配置问题,我的问题是不知道如何设置,更具体一点就是不知道如何把IO设置成想要的功能,还是说这是在代码里写?不过我很块否认了,我看了之前我抄的RFID串口通信协议,里面没有IO配置的语句。所以应该还是在idf.py menuconfig中设置。

明天我要做的就是在menuconfig中搞好配置,以及看懂交互的例程代码。

浙公网安备 33010602011771号

浙公网安备 33010602011771号