Cortex-M3学习笔记

一,cortexM3权威指南:

二,

三,寄存器:

1.影子寄存器的引入是ARM的一个特点(X86,PowerPC都没有)。我们知道,ARM有16个通用寄存器,这16个通用寄存器在指令中使用4个bit来标识,但是在不同的模式下,同样的4个bit 指向不同的物理寄存器,这些不同的物理寄存器就被称之为影子寄存器。不同的通用寄存器的影子寄存器个数也不相同,有的没有,有的只有1个,有的多达5个。要记住一点:所有的影子寄存器都是一个实际存在的物理寄存器。

RM核是一个非常紧凑的设计,影子寄存器的引入就是这种设计的表现。通过引入影子寄存器,指令可以重 复使用相同的寄存器编码,但是在不同模式下,这些编码对应不同的物理寄存器。比如Abort模式下的R13就同用户模式下的R13不同,虽然它们编码一 样,但是实际上对应的是不同的物理寄存器(可以将CPSR的模式域当作片选)。

2.我们可以计算一下ARM的通用寄存器数目 1个状态寄存器CPSR,5个异常模式下的状态寄存器的影子寄存器,16个通用寄存器R0 ~ R15,10个异常模式下的R13和R14的影子寄存器,5个FIQ模式下的R8 ~ R12的影子寄存器,总共是37个寄存器,这个数目同X86相比要多很多。

3.由于影子寄存器的编码同其所Banked的寄存器的编码是一样的,因此象“MOV R0, R13”这样的指令,在不同的模式下,访问的是不同的物理寄存器R13,这意味我们在异常模式下是不能访问正常意义上的R13的,这对一般的寄存器可能关系不大。但是,对状态寄存器CPSR而言,这是很恼人的,因为要切换CPU的状态,只能通过修改状态寄存器CPSR来进行,对CPSR的影子寄存器的修改并不 能影响CPSR本身,这也就是为什么会有MOV和MOVS,SUB和SUBS的原因。但是,像TEQ,BEQ等这样的比较指令修改的是CPSR的内容,而不是该模式下CPSR影子寄存器的内容。这也是CPSR同一般Rx不一样的地方:CPSR对所有异常模式都是可见的,只不过这种可见性并不表示指令可以直 接读取或修改CPSR的内容,更准确的说,这种可见性是对指令系统(如TEQ, BEQ等条件判断指令)而言的,只能通过特殊的指令来影响CPSR中的相关域,而不能直接读取或修改CPSR,因此CPSR对程序员的是不可见的。

4.引入影子寄存器的另外一个目的是当中断或异常产生时,CPU会将当前“CPU的状态”保存在影子寄存器中。从CPU角度看,它的“状态”包括: PC(也就是R15)值 、PSR的值。您也许认为R0等通用寄存器也是状态,从某种意义上说您是对的。但是那些不是“CPU的状态”,它们是“应用的状态”。当中断或异常产生后,CPU并不关心它们,CPU只是:(1)PC值被保存在当前模式下的R14中 (2) CPSR值被保存在当前模式下的影子寄存器中。

5.保存CPU的状态是一种廉价的操作,但是要保存应用的状态可就很昂贵了,因为至少有13个寄存器(R0 ~ R12)需要保存,为了加快这种操作,ARM的内存访问指令可以将一组寄存器的内容保存到内存中,反之亦然。

6.

7.寄存器的一些细节。

(1) 主堆栈指针MSP和进程堆栈指针PSP在某一时刻只存在一个;

(2) MSP主要用于操作系统

(3) 五个特殊功能寄存器:

[1]xPSR 记录ALU(运算单元)标志(0标志,进位标志,负数标志,溢出标志),执行状态,以及当前正服务的中断号

[2]PRIMASK 除能所有的中断--不可屏蔽中断(NMI)除外

[3]FAULTMA 除能所有的fault--NMI除外,且被除能的faults会向上访问

[4]BASEPRI 除能所有优先级不高于某个具体数值的中断

[5]CONTROL 定义特权状态,并且决定使用哪一个堆栈指针

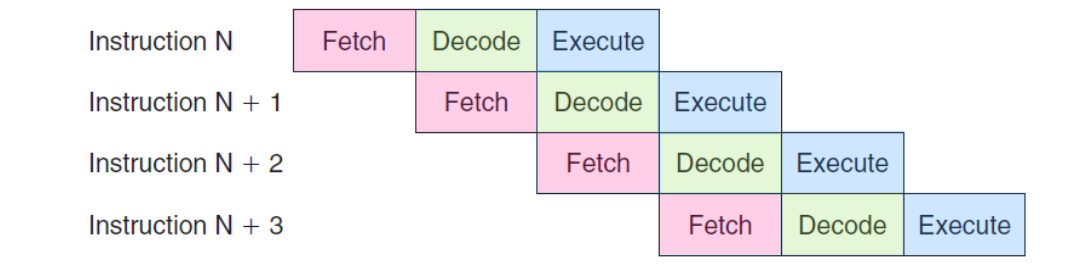

四.三级流水线!

(1)执行一条分支指令或直接修改PC而发生跳转时,ARM内核有可能会清空流水线,需要重新读取指令。

(2)即使产生了一个中断,一条处于“执行”阶段的指令也将会完成。流水线里其他指令将会被放弃,而处理器将从向量表的适当入口开始填充流水线。

(3)不论是执行16位指令还是32位指令,读取PC(程序计数器)时,会返回当前指令地址+4的值。

五.

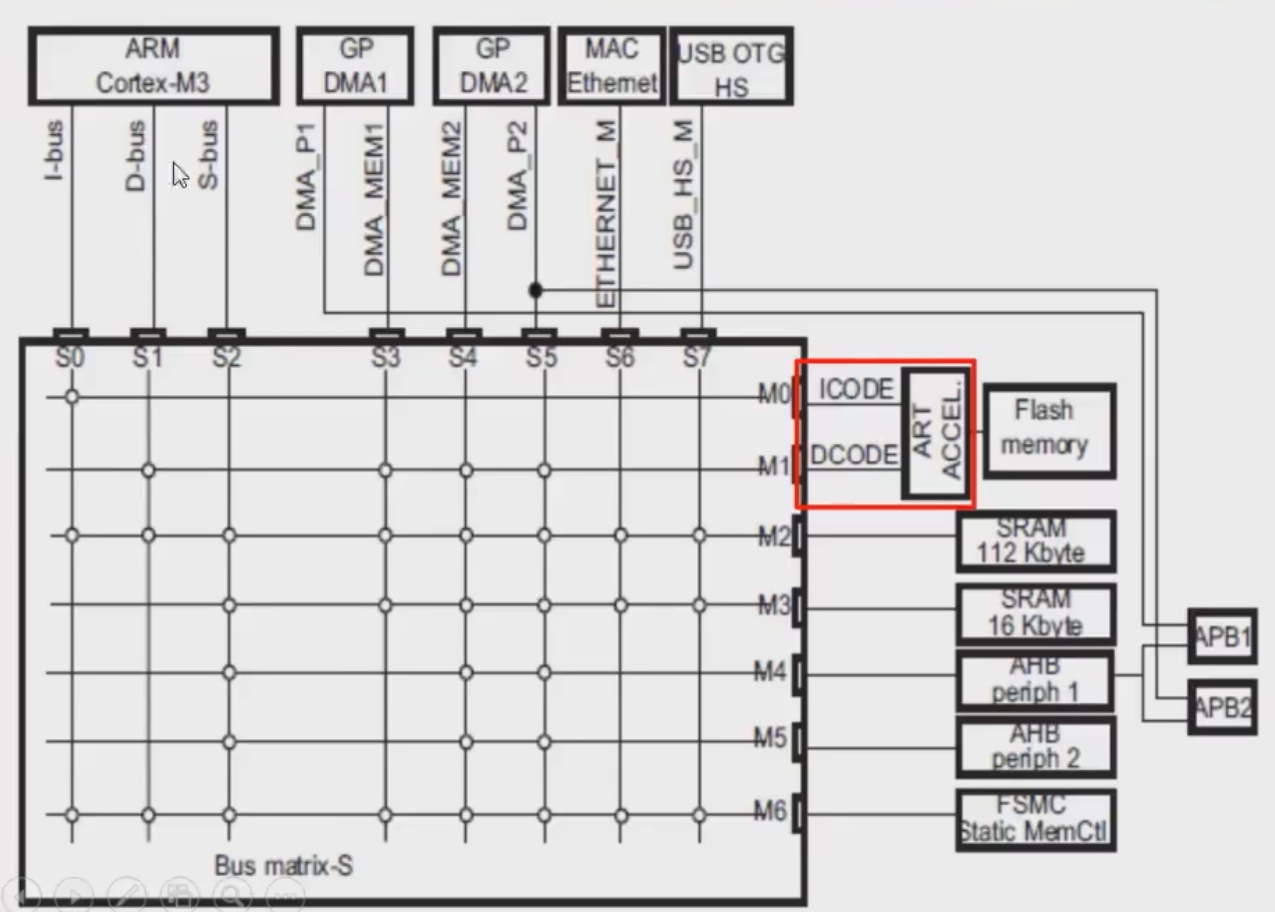

(1)程序位于Flash接口存储器中,通过ICode指令总线访问cortex-M3内核

(2)数据总线DCode用于常量和调试访问

(3)总线矩阵协调CPU和DMA对SRAM、闪存和外设的访问

(4)DMA总线执行内存和外设之间的数据传输

六.总线矩阵

8个AHB主设备

7个AHB从设备