AMD MPSoC R5 AES加密示例

AMD MPSoC R5 AES 示例

测试环境

测试单板

ZCU06

测试工具

- Vitis 2021.2

R5 AES 测试流程

创建Platform

在Vitis的 “File - New ” 中,选择“Platform Project”, 指定名称如“zcu106_r5”, 再选择对应的XSA文件和 Processor 如 “psu_cortexr5_0”。

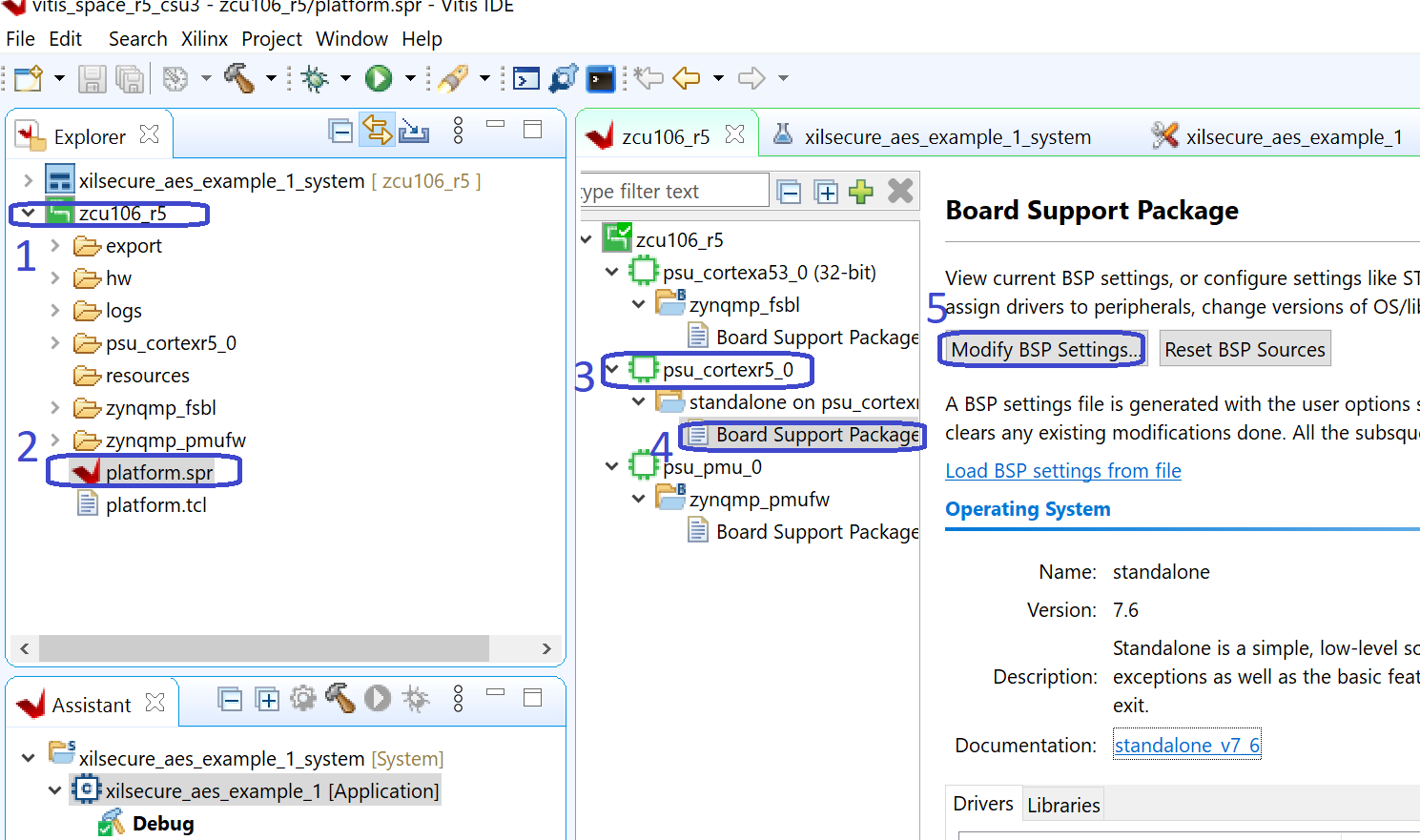

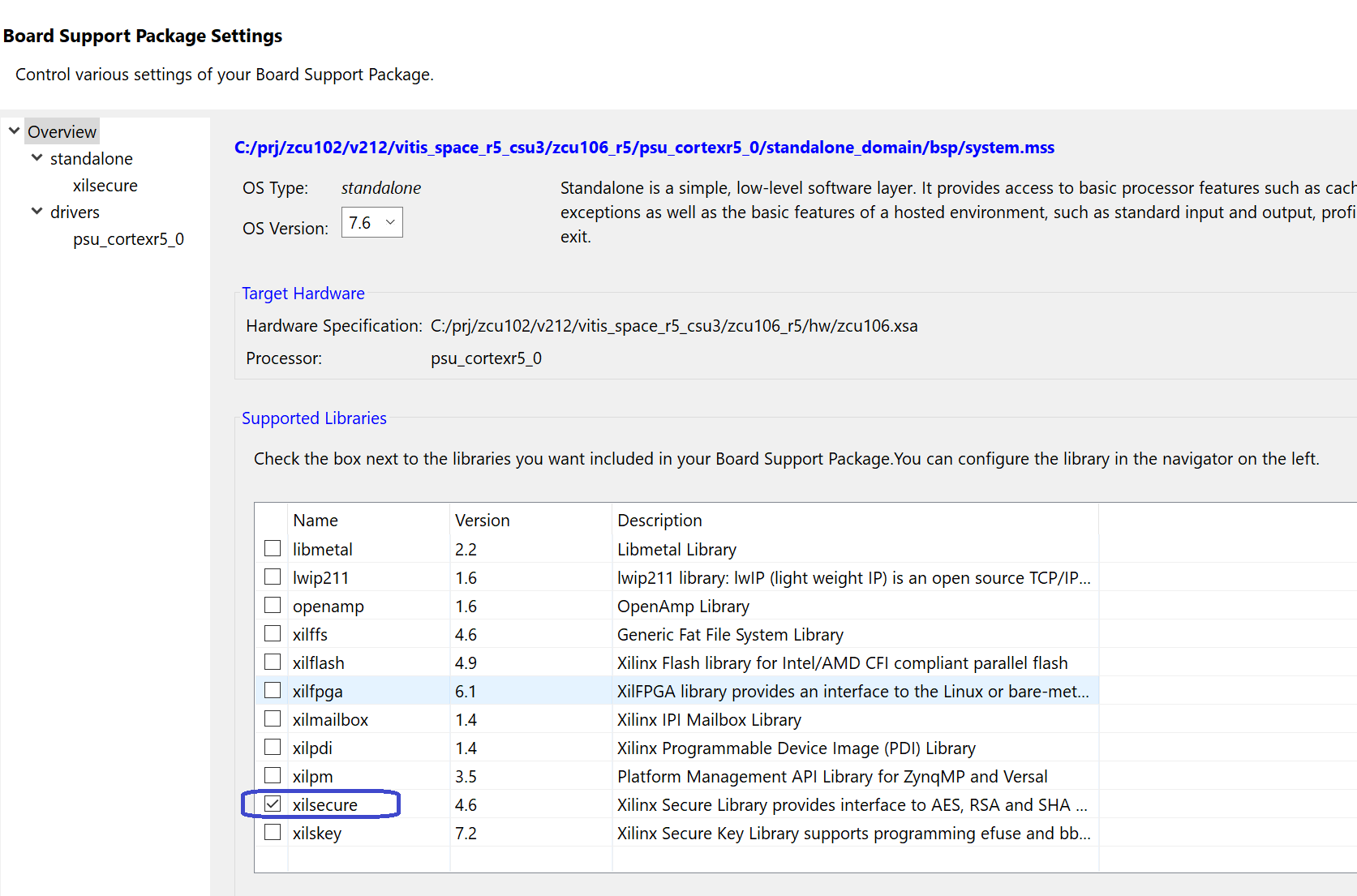

使能AES库

-

打开hw_platform工程。

-

双击“platform.spr”文件。

-

双击“psu_cortexr5_0”的 “board support package”。

-

点击 “Modif BSP Settings”。

-

在“Supported Libraries”中选择xilsecure。

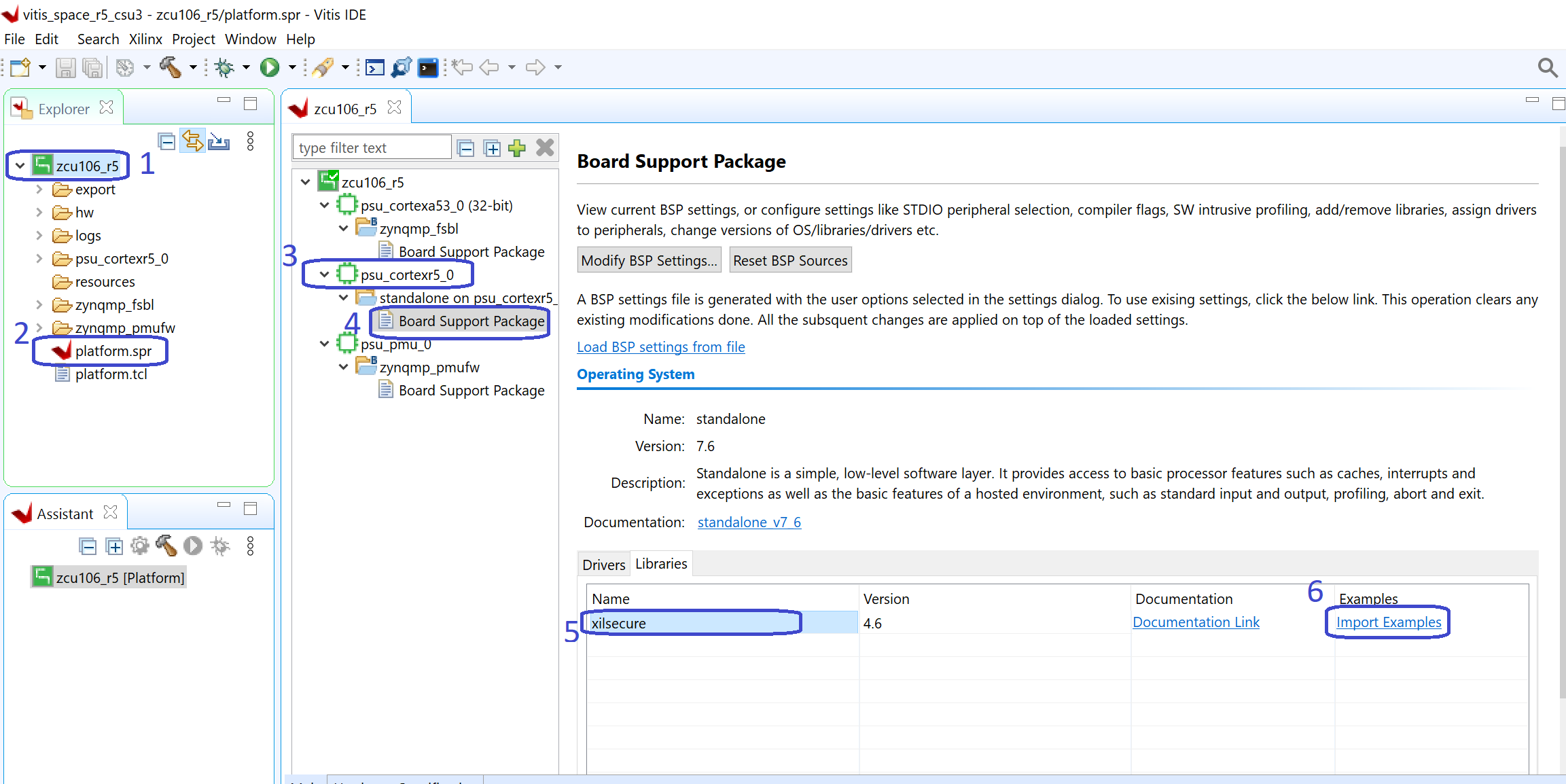

导入AES示例

-

打开hw_platform工程。

-

双击“platform.spr”文件。

-

双击“psu_cortexr5_0”的 “board support package”。

-

等待Libraries窗口显示

-

点击xilsecure行右边的import examples

-

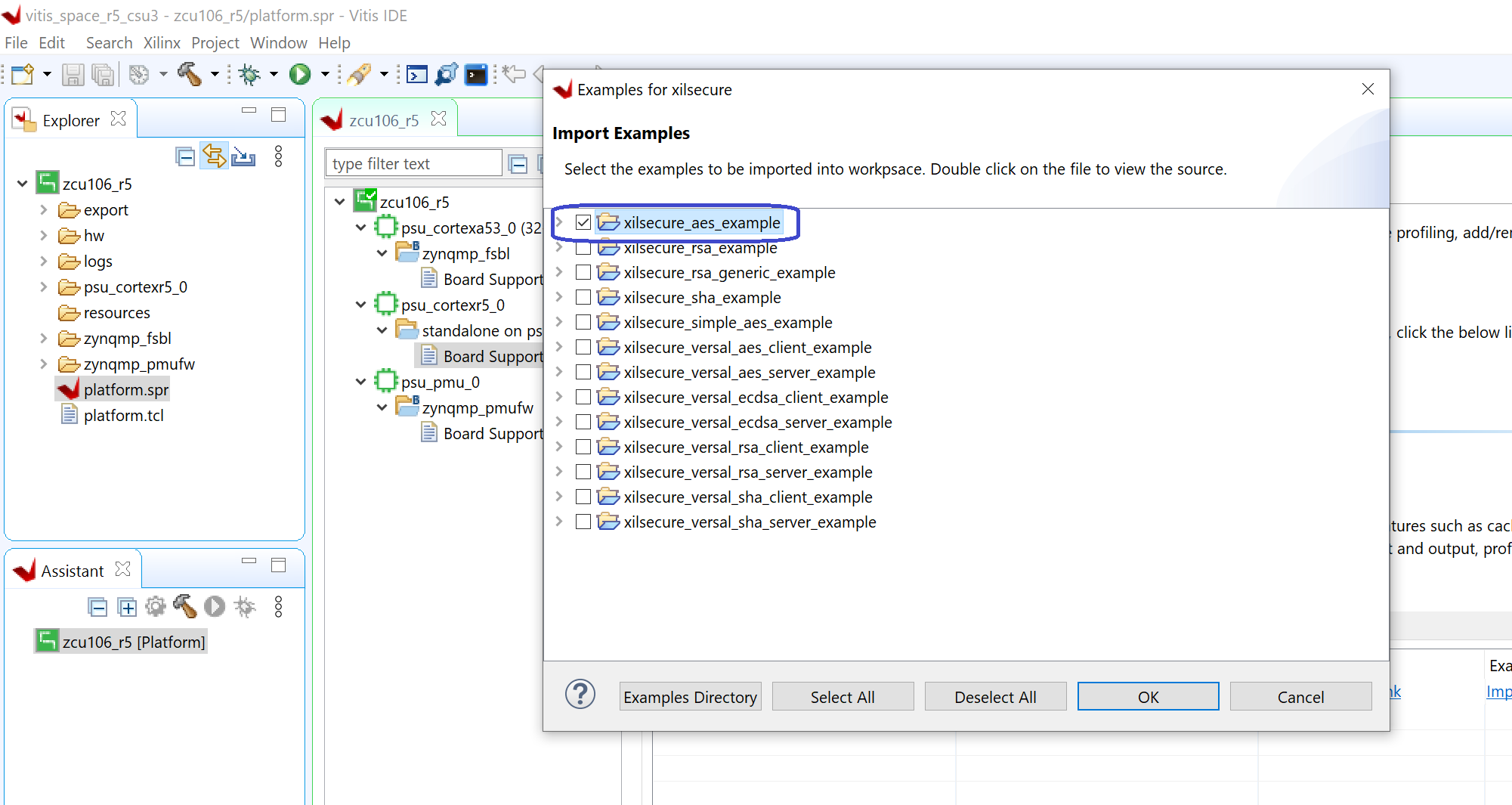

选择"xilsecure_aes_example"

定制

导入example, 创建的工程里有文件xilsecure_aes_example.c。 打开文件,确认AES 密钥和数据地址。

AES密钥

AES密钥如下:

/*

* The hard coded aes key for decryption, in case user given key is being used

* it will be loaded in KUP before decryption

*/

static const u8 CsuKey[] = {

0xf8, 0x78, 0xb8, 0x38, 0xd8, 0x58, 0x98, 0x18,

0xe8, 0x68, 0xa8, 0x28, 0xc8, 0x48, 0x88, 0x08,

0xf0, 0x70, 0xb0, 0x30, 0xd0, 0x50, 0x90, 0x10,

0xe0, 0x60, 0xa0, 0x20, 0xc0, 0x40, 0x80, 0x00

};

/*

* The hard coded iv used for decryption secure header and block 0

*/

u8 CsuIv[] = {

0xD2, 0x45, 0x0E, 0x07, 0xEA, 0x5D, 0xE0, 0x42, 0x6C, 0x0F, 0xA1, 0x33,

0x00, 0x00, 0x00, 0x00

};

内存地址

默认保存密文和明文的内存地址都是0x04000000,需要和代码中的地址对应,可以根据自己需要更改。

static u32 ImageOffset = 0x04000000;

static u32 DestinationAddr = 0x04000000;

创建密文

AMD提供工具bootgen,加密数据,创建密文。

bootgen的配置文件user_data_example.bif如下:

the_ROM_image:

{

[keysrc_encryption]kup_key

[encryption=aes, aeskeyfile=user_data_kup_key_example.nky, load=0x04000000]data.bin

}

上面的data.bin是明文文件; user_data_kup_key_example.nky是AES的密钥。如果不存在AES的密钥, 工具bootgen会自动生成密钥。 生成密钥后,需要更新文件xilsecure_aes_example.c。

在“Xilinx Software Command Line Tool 2021.2”中执行命令,“ bootgen -arch zynqmp -p userdata -image user_data_example.bif -o data.bin.enc -w on -log error”,可以得到密文文件data.bin.enc。

xsct% bootgen -arch zynqmp -p userdata -image user_data_example.bif -o data.bin.enc -w on -log error

WARNING: [Common 17-259] Unknown Tcl command 'bootgen -arch zynqmp -p userdata -image user_data_example.bif -o data.bin.enc -w on -log error' sending command to the OS shell for execution. It is recommended to use 'exec' to send the command to the OS shell.

****** Xilinx Bootgen v2021.2

**** Build date : Oct 19 2021-03:13:27

** Copyright 1986-2021 Xilinx, Inc. All Rights Reserved.

[INFO] : Bootimage generated successfully

运行AES

以调试模式运行工程xilsecure_aes_example_1。当Vitis SDK停在main()入口时,在xsct界面里下载密文到0x4000000。下载完成后,再继续运行xilsecure_aes_example_1。 运行完XSecure_AesDecrypt()后,暂停程序,显示存储器0x4000000的内容,可以看到它的内容和明文的16进制值一样。

AES解码成功。

xsct%

Info: Cortex-R5 #0 (target 6) Stopped at 0x0 (Suspended)

Downloading Program -- C:/prj/zcu102/v212/vitis_space_r5_csu2/xilsecure_aes_example_1/Debug/xilsecure_aes_example_1.elf

section, .vectors: 0x00000000 - 0x00000467

.................

section, .stack: 0x001044f0 - 0x00107cef

0% 0MB 0.0MB/s ??:?? ETA

100% 0MB 0.5MB/s 00:00

Setting PC to Program Start Address 0x000001d0

Successfully downloaded C:/prj/zcu102/v212/vitis_space_r5_csu2/xilsecure_aes_example_1/Debug/xilsecure_aes_example_1.elf

Info: Cortex-R5 #0 (target 6) Running

Info: Cortex-R5 #0 (target 6) Stopped at 0x1001b8 (Breakpoint)

main() at ../src/xilsecure_aes_example.c: 123

123: Status = SecureAesExample();

xsct% dow -data data.bin.enc 0x04000000

0% 0MB 0.0MB/s ??:?? ETA

100% 0MB 0.4MB/s 00:00

Successfully downloaded C:/prj/zcu102/v212/vitis_space_r5_csu2/xilsecure_aes_example_1/data.bin.enc

xsct% Info: Cortex-R5 #0 (target 6) Running

xsct% Info: Cortex-R5 #0 (target 6) Stopped at 0x100204 (Step)

SecureAesExample() at ../src/xilsecure_aes_example.c: 153

153: u8 *Dst = (u8 *)(UINTPTR)DestinationAddr;

xsct% Info: Cortex-R5 #0 (target 6) Running

xsct% Info: Cortex-R5 #0 (target 6) Stopped at 0x100214 (Step)

....................

xsct% Info: Cortex-R5 #0 (target 6) Stopped at 0x100370 (Breakpoint)

189: Status = XSecure_AesDecrypt(&Secure_Aes, Dst,

xsct% Info: Cortex-R5 #0 (target 6) Running

xsct% Info: Cortex-R5 #0 (target 6) Stopped at 0x10038c (Step)

194: if(Status != XST_SUCCESS)

xsct% mrd 0x04000000

4000000: 6D783F3C

xsct% mrd 0x04000000 20

4000000: 6D783F3C

4000004: 6576206C

4000008: 6F697372

400000C: 31223D6E

4000010: 2022302E

4000014: 6F636E65

4000018: 676E6964

400001C: 5455223D

4000020: 22382D46

4000024: 61747320

4000028: 6C61646E

400002C: 3D656E6F

4000030: 226F6E22

4000034: 0A0D3E3F

4000038: 69663F3C

400003C: 6556656C

4000040: 6F697372

4000044: 2E34206E

4000048: 3F302E30

400004C: 70633C3E

xsct%

浙公网安备 33010602011771号

浙公网安备 33010602011771号