【分享】 MPSoC的VCU超频

1. 超频介绍

很多芯片可以暂时超频使用。 当然,出于良品率、长期可靠性考虑,厂家官方都不建议超频使用。

Xilinx的器件质也能超频。几年前,当Zynq-7000刚面世时,通过修改PLL的设置,7020的A9的频率被超频到1GHz后,也能正常运行。

最近有人问到MPSoC的VCU能不能超频。检查Vivado里的VCU设计后,确认通过简单步骤,VCU也能超频。这是黑客操作。请确保电源有足够的供电、单板有足够的散热能力。超频后,VCU已经工作在产品规格之外,工程师需要承担器件可能损坏的责任。如果在产品中使用,一定要注意在高温、低温等极端情况下,是否能正常工作。

2. VCU正常设计

2.1. VCU时钟

VCU编解码器内部使用时钟pll_ref_clk,所有外部AXI接口使用其它时钟。如果调整内部时钟pll_ref_clk,不会影响外部接口时钟,也不会引起时序问题。所以非常方便。

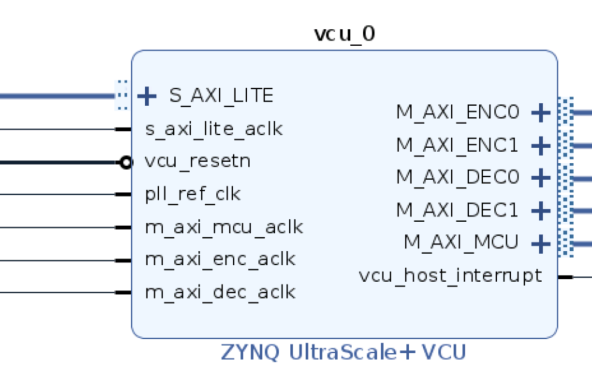

VCU的信号如下。

VCU的信号说明。

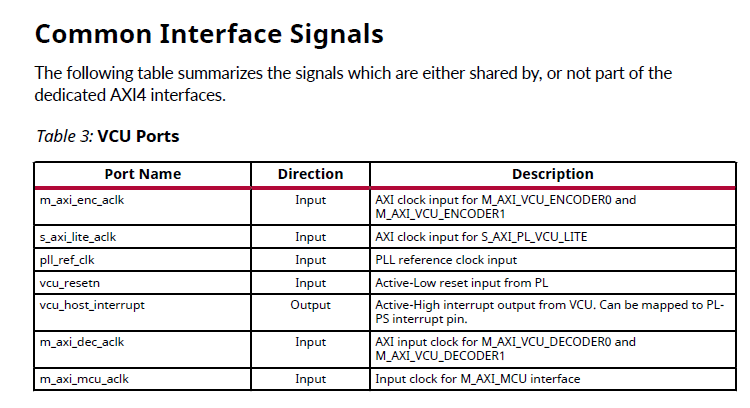

VCU的工作时钟一般是667MHz,由VCU自己内部的PLL产生。

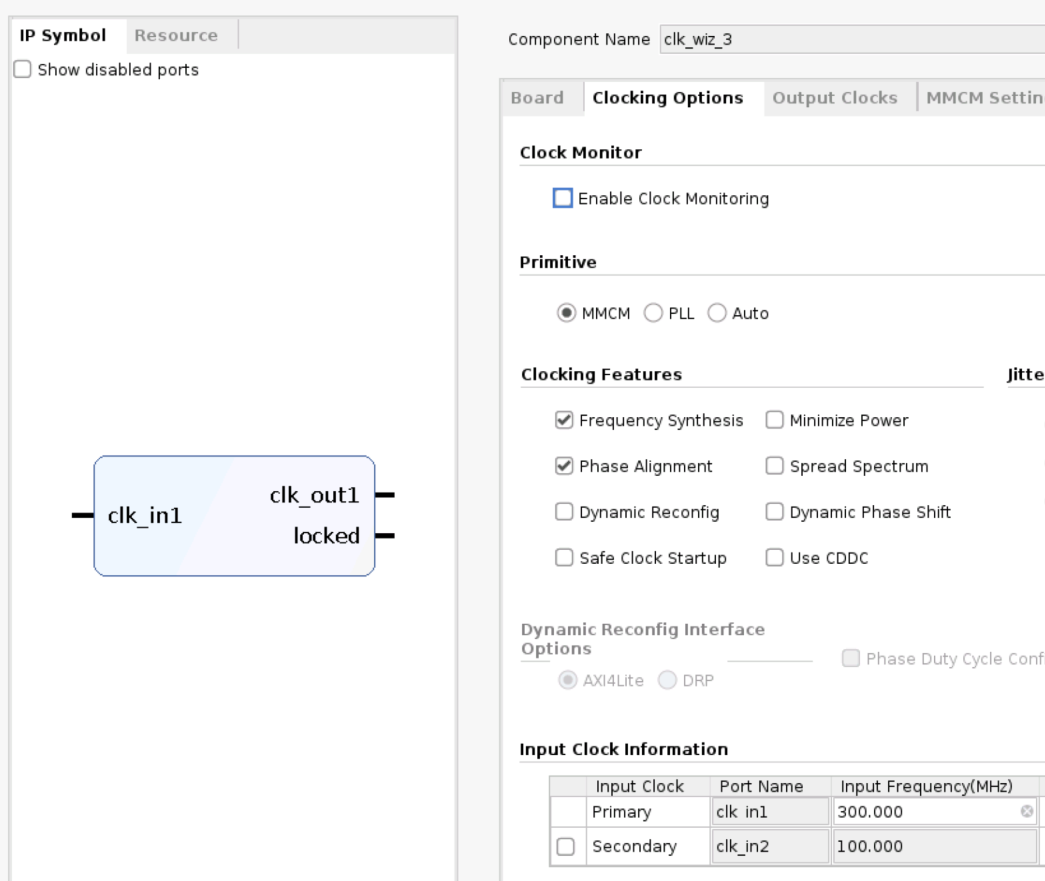

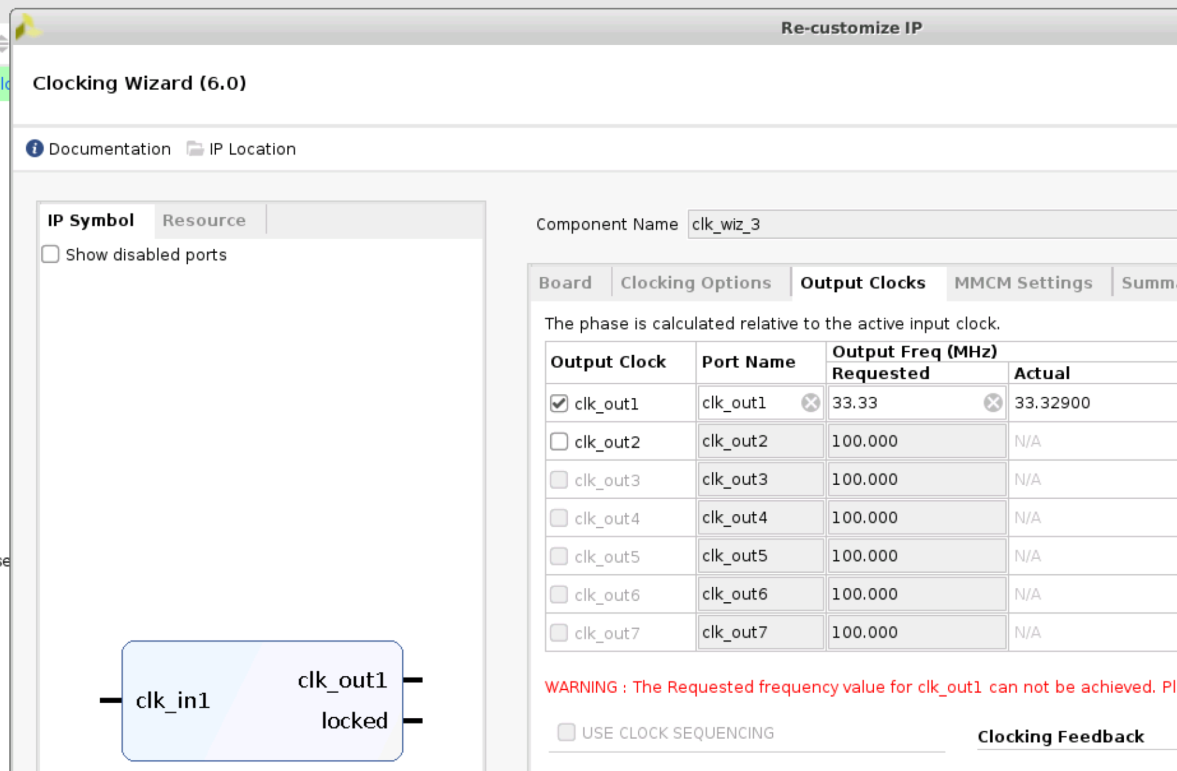

2.2. Clocking Wizard配置

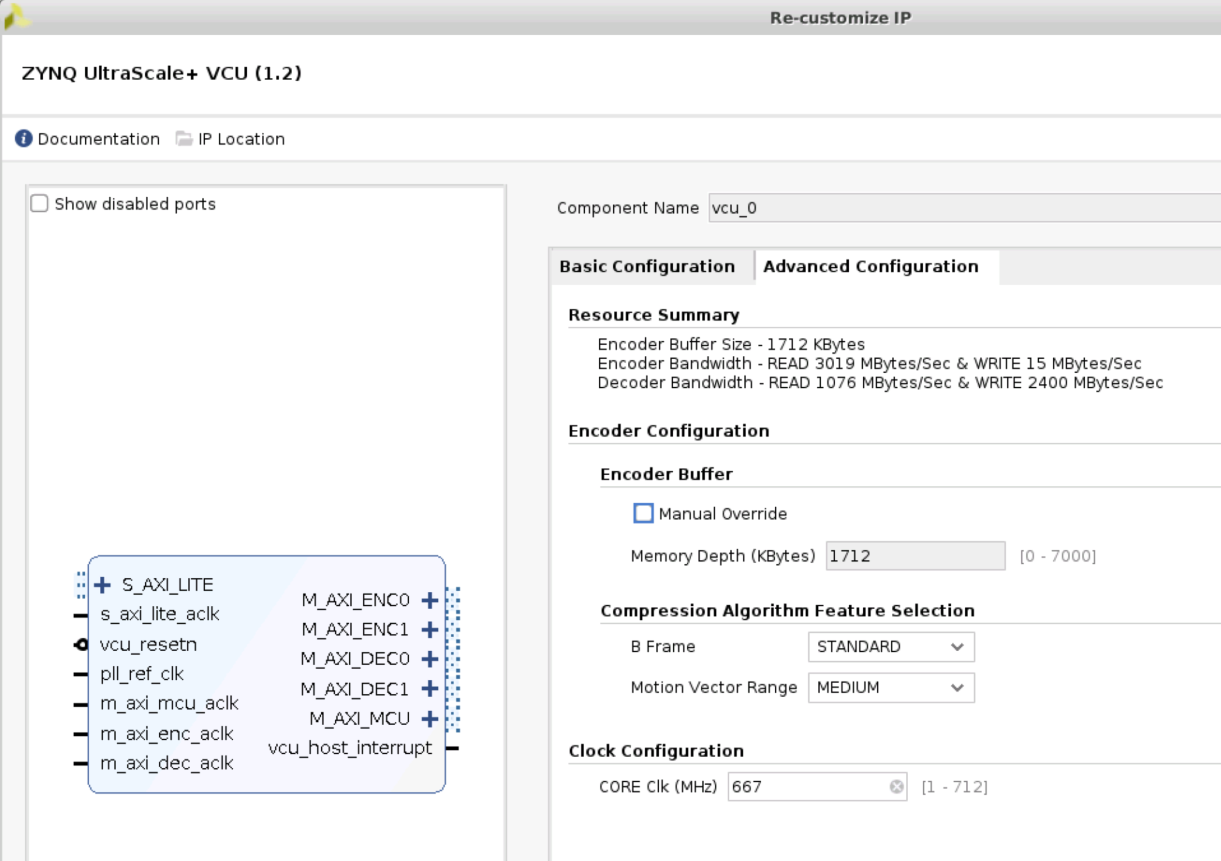

VCU内部时钟pll_ref_clk来自于外部时钟芯片si570的输出。si570的输出是300MHz的时钟,进入PL后,经过一个Clocking Wizard,产生33MHz给VCU作为pll_ref_clk。

下图展示了VCU的时钟来源,包括从si570到Clocking Wizard的设计。

Clocking Wizard的输入是300MHz。

Clocking Wizard的输出是33.33MHz。

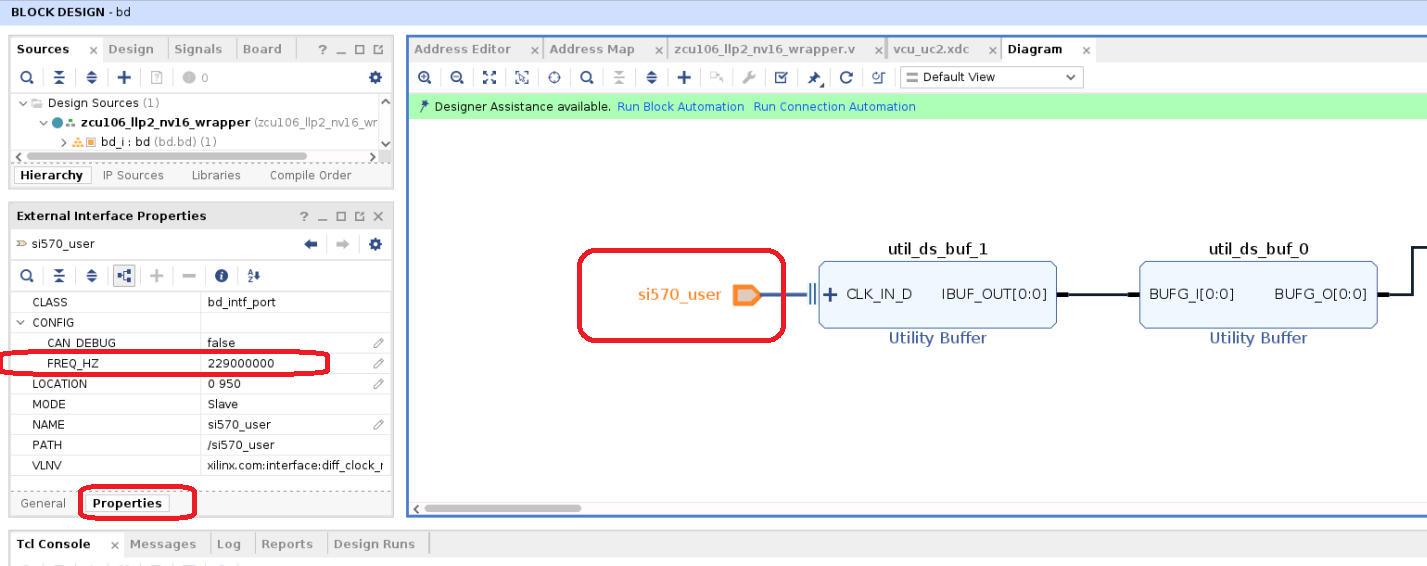

2.3. 单板时钟

2.3.1. vivado接口属性

PL设计中,来自于外部时钟芯片si570的信号是si570_user。在Vivado的属性设置里,声明了si570_user是300MHz。

2.3.2. vivado约束

vivado约束文件里,也指定了si570_user的周期是3.333ns,对应的频率是300MHz。

set_property PACKAGE_PIN AH12 [get_ports {si570_user_clk_p[0]}]

set_property IOSTANDARD LVDS [get_ports {si570_user_clk_p[0]}]

create_clock -period 3.333 [get_ports si570_user_clk_p]

3. 超频步骤

Vivado会检查VCU的时钟。如果VCU的时钟超出规格,会报错。

超频的核心诀窍是欺骗Vivado,向Vivado声明一个假的时钟频率。比如实际输入频率是300MHz,我们在设计中却告诉它是200MHz。那么在后续的倍频操作中,Vivado会以200MHz计算出产生667MHz的倍频分频系数,实际得到的频率就是667*(300/200),也就是1000MHz。

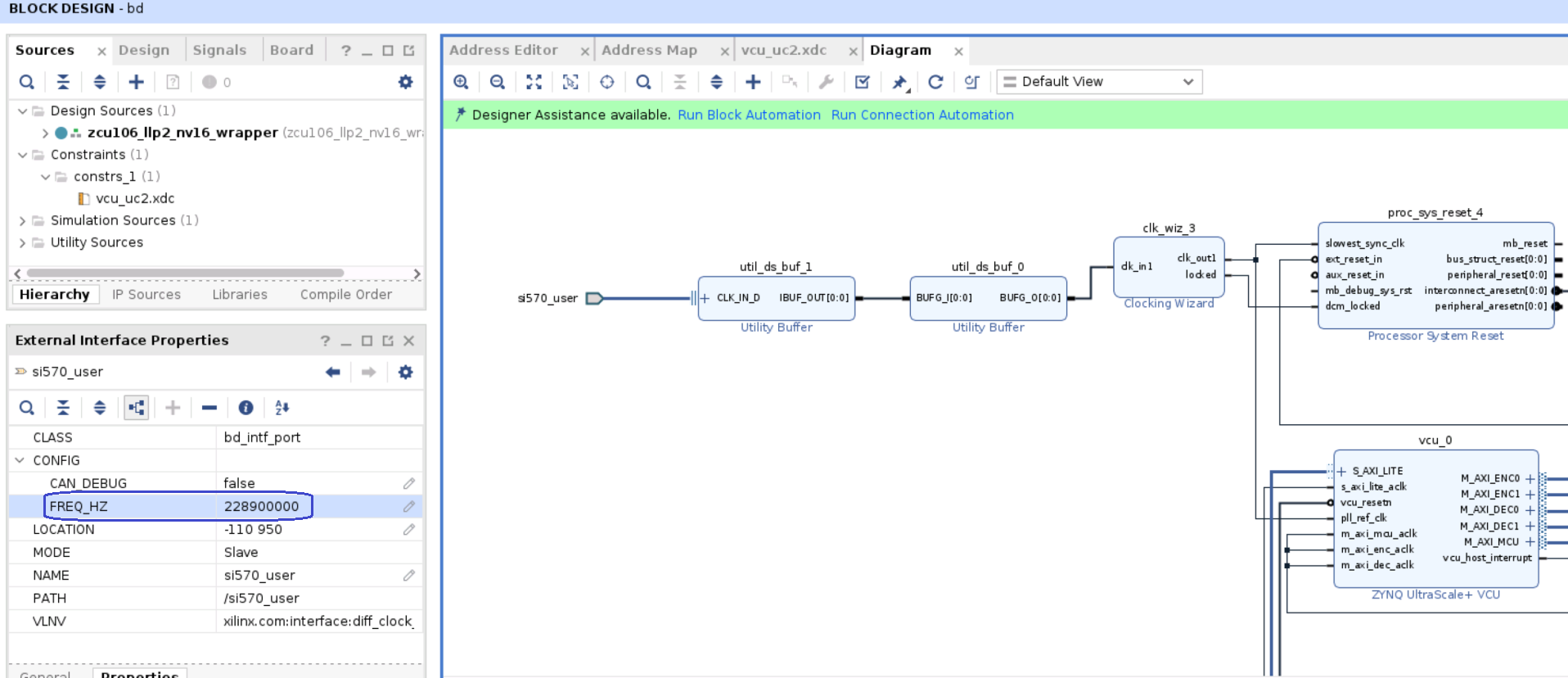

测试时,打算把VCU的频率超频到933MHz。VCU的配置里,已经把VCU的频率,改为712MHZ。因此要把输入频率,降低933/712=1.310倍,也就是改为300/1.310=228.9MHz,对应的周期4.368。

3.1. vivado接口属性

在Vivado的属性设置里,把si570_user的频率,从300MHz,改为228.9MHz。

3.2. vivado约束

vivado约束文件里,也指定了si570_user的周期是4.368ns,对应的频率是933MHz。

set_property PACKAGE_PIN AH12 [get_ports si570_user_clk_p]

set_property IOSTANDARD LVDS [get_ports si570_user_clk_p]

create_clock -period 4.368 [get_ports si570_user_clk_p]

4. 结论

编译Vivado工程,更新PetaLinux工程的HDF文件,再产生Linux文件。单板能正常启动,编码4K文件时,帧率能够显著提升。

最后,再次声明,超频后,VCU已经工作在产品规格之外,需要自己承担器件可能损坏的责任。