3.硬件断点、陷阱和JTAG

R/W 0 和LEN 0对应断点0线性地址;

DR则是调试寄存器

硬件断点:

- 基于CPU的调试寄存器

- 可以对代码、数据访问和IO访问设置断点

- 断点被触发时,CPU产生的是1号异常

- 受调试寄存器的数量限制

- WinDbg 的ba命令设置的便是硬件断点

- 在多处理器系统中,硬件断点是与CPU相关的,也就是说针对一个CPU设置的硬件断点并适用于其他CPU

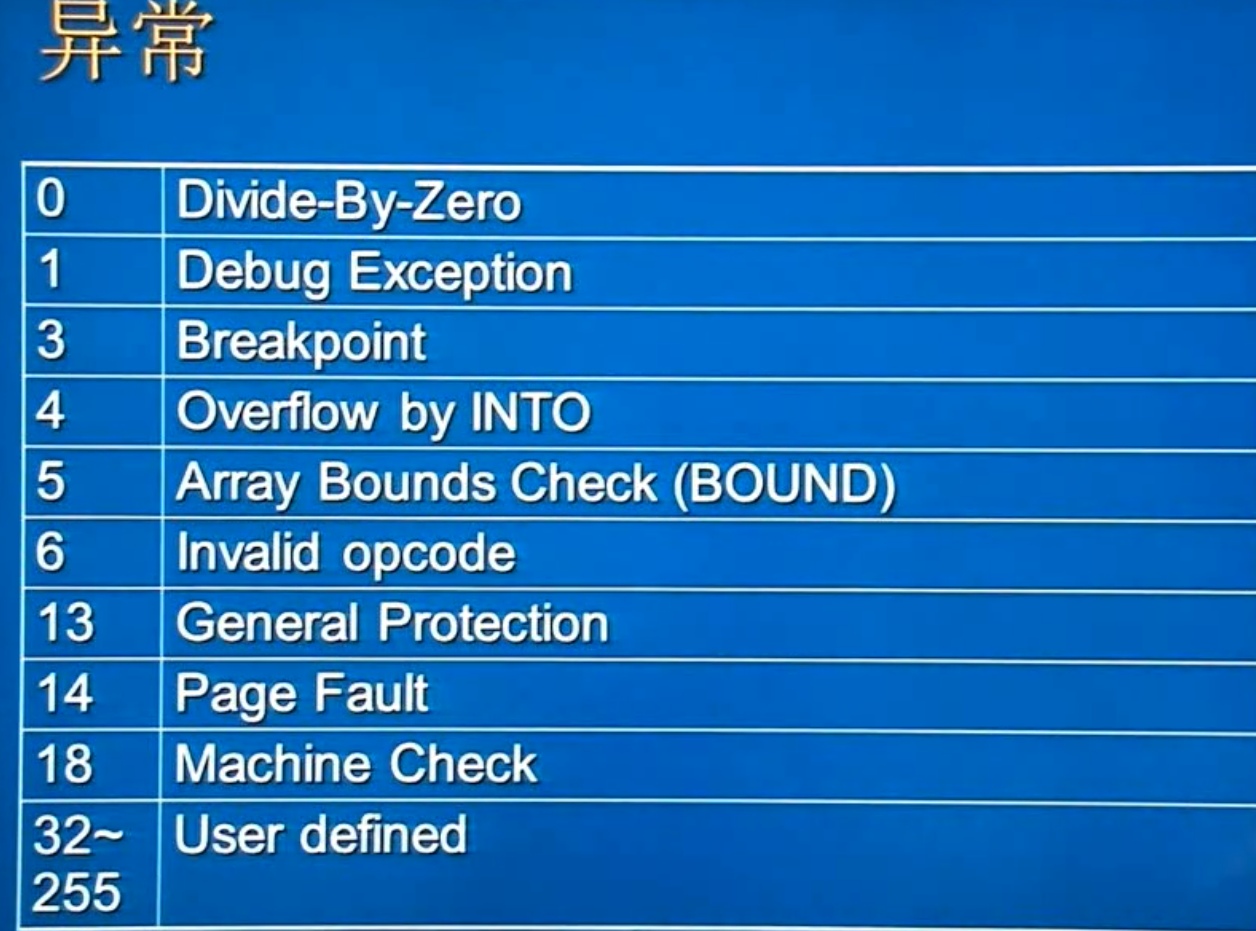

X86 经典异常

比如说INT 3 (CC)断点最终会调用 3Breakpoint

单步执行则是 1号表Debug Exception

代码除0则触发 0号表Divide-By-Zero

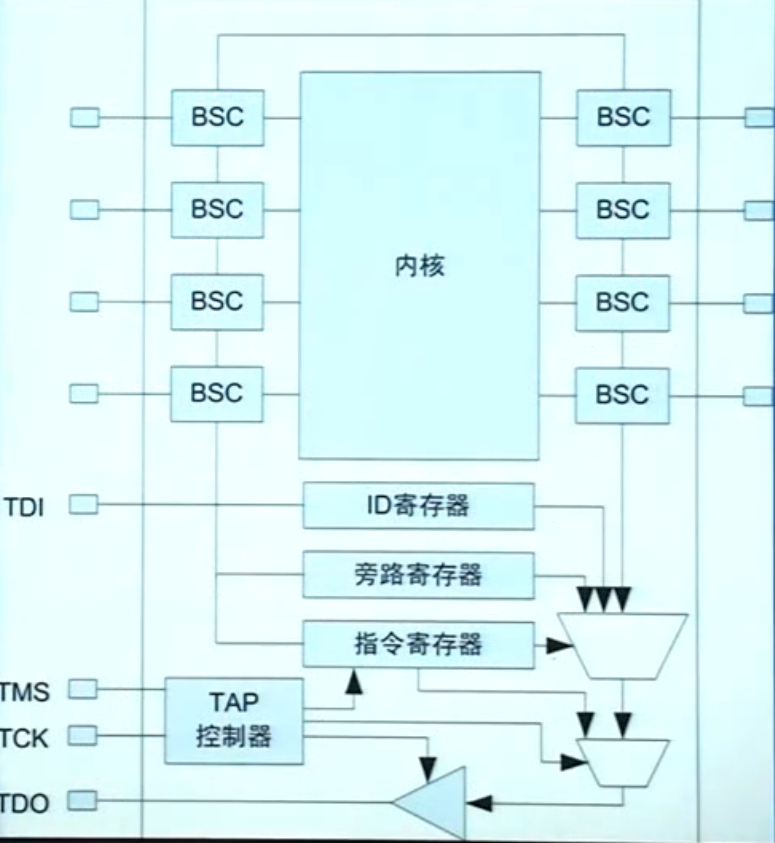

JTAG

原创学习随笔心得,请勿转载!