zynq ps pcie endpoint 调试

ps 端 ep 配置, 非 pl 端

这里说明大概流程, 细节查看文档

需要调试细节和资料可留言

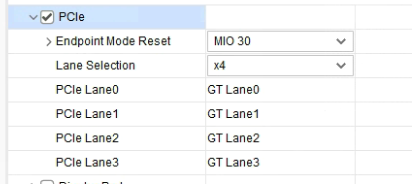

基础配置

基础配置1:

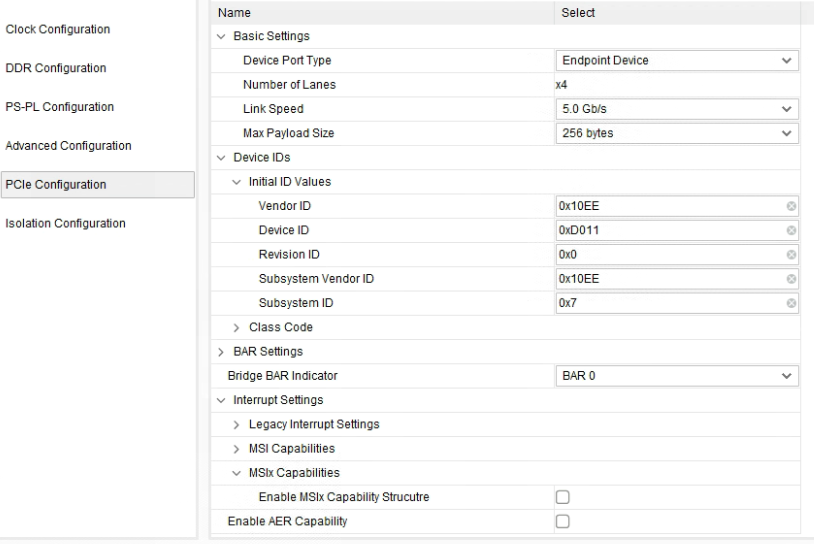

基础配置2:

endpoint 也需要配置 id, 中断类型, bar 数量等

1. linux 驱动代码说明

首先从官方示例代码 ps_pcie_dma.c 中 提供了如何通过 DMA 和 PIO 的方式对数据进行传输。

2. PIO 模式

PIO 的读写方式是直接通过 CPU 将数据拷贝至 BAR 2 空间中

static ssize_t

pio_write (struct file *file,

const char __user * buffer, size_t length, loff_t * f_offset) {

char *barMemory = NULL;

struct expresso_dma_device *xdev;

ssize_t numBytes = 0;

xdev = file->private_data;

barMemory = (char *) xdev->BARInfo[PIO_MEMORY_BAR_NUMBER].BAR_VIRT_ADDR; /** PIO_MEMORY_BAR_NUMBER 2 */

...

barMemory += *f_offset;

numBytes = copy_from_user(barMemory, buffer, length);

...

return numBytes;

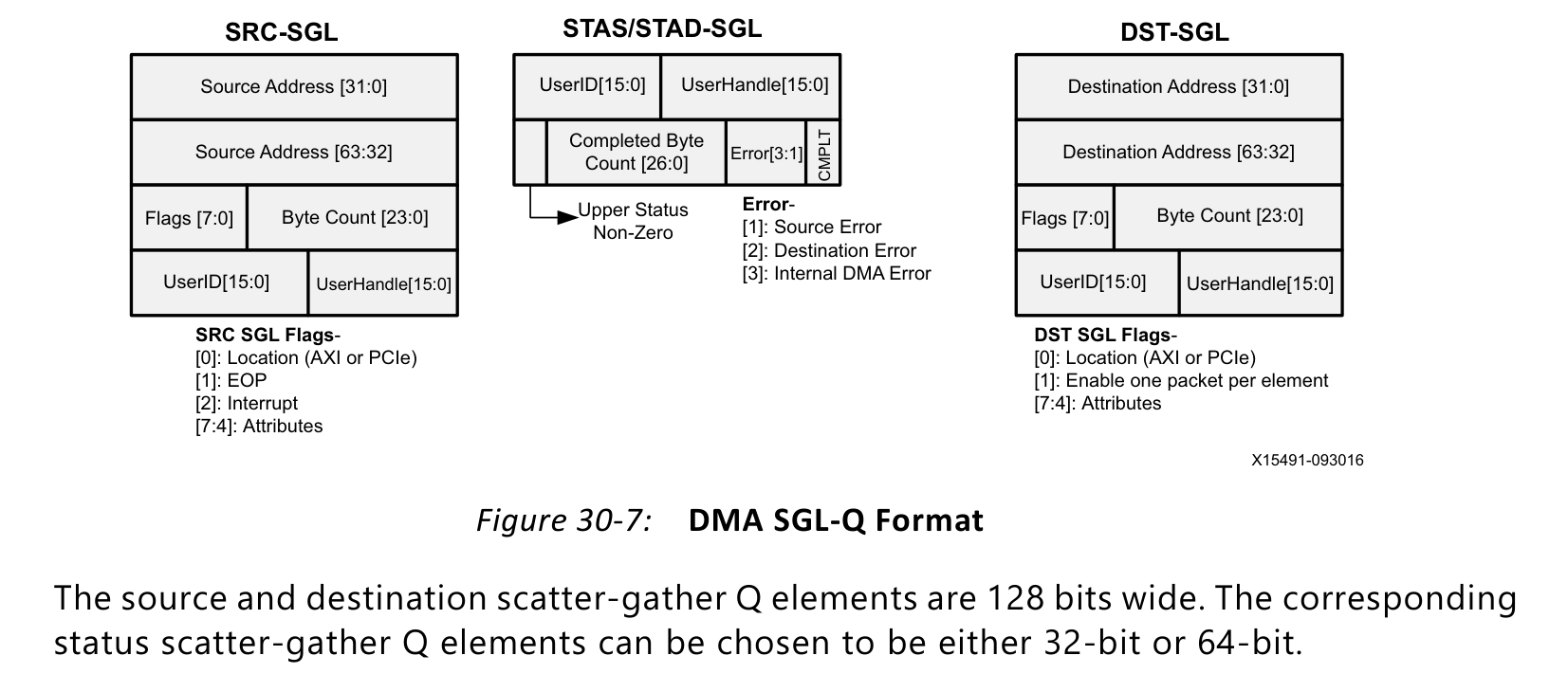

3. DMA

这里的 DMA 采用的是 SG DMA 模块, 该模块需要 对应的 EP 模块支持, 在该平台中,DMA 模块映射在 bar0 空间, 通过 host 主机驱动配置

手册中描述了 AXI-PCIE DMA 是支持 SG(scatter-gather, 既不连续内存 DMA) 模式的

sg 模块在 linux 也有对应的数据结构控制

4. 说明

手册说明了 zynq 系列 PS PCIE 相关寄存器分五个模块

- AXIPCIE_DMA, pcie DMA 操作寄存器

- AXIPCIE_EGRESS, 数据输出地址绑定寄存器

- AXIPCIE_INGRESS, 数据输入地址绑定寄存器

- AXIPCIE_MAIN , 配置总寄存器, 桥, ECAM 等

- PCIE_ATTRIB, 模块, 其中对 bar, id等配置都是在该寄存器中实现

这里应该是不需要 fpga 做额外类似 PL 端 IP 盒的配置

5. 注意事项

在 linux 上跑上述示例之前, 需要先跑对应的 EP 裸机代码

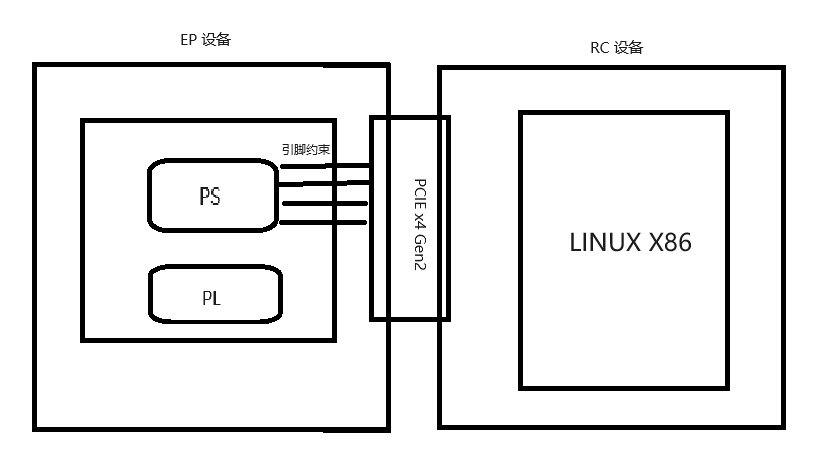

6. 结构图

本文来自博客园踩坑狭,作者:韩若明瞳,转载请注明原文链接:https://www.cnblogs.com/han-guang-xue/p/18265205