【原创】The solutional manual of the Verilog HDL: A Guide to Digital Design and Synthesis (2nd)--ch12

Chapter 12. User-Defined Primitives

12.7 Exercises

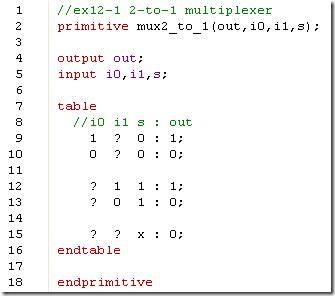

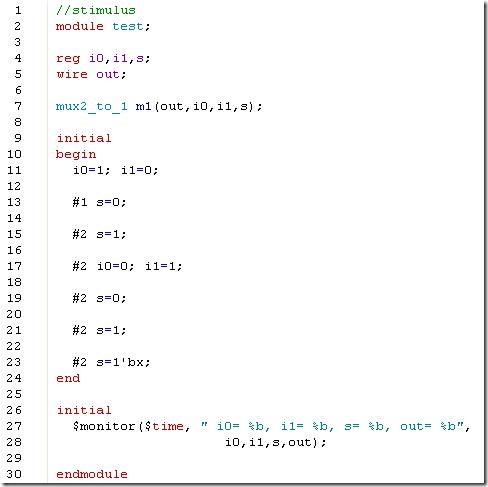

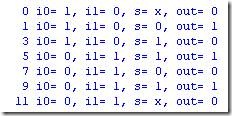

1. Design a 2-to-1 multiplexer by using UDP. The select signal is s, inputs are i0,i1, and the output is out. If the select signal s=x, the output out is always 0. If s=0, then out=i0. If s=1, then out=i1.

my answer:

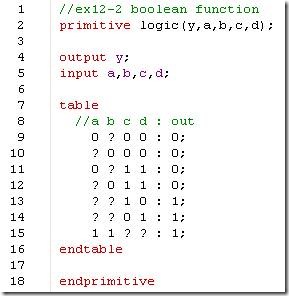

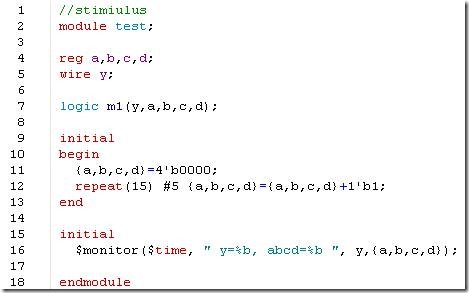

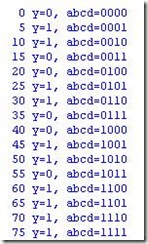

2. Write the truth table for the Boolean function Y=(A&B)|(C^D). Define a UDP that implements this Boolean function. Assume that the inputs will never take the value x.

my answer:

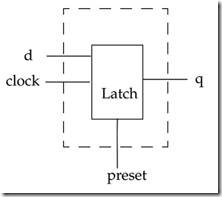

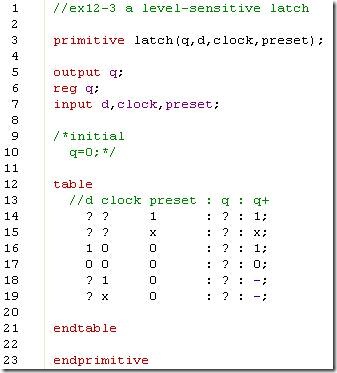

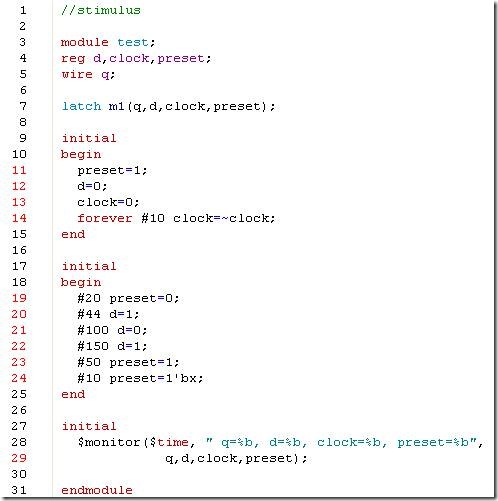

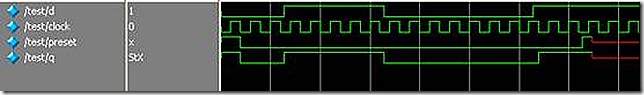

3. Define a level-sensitive latch with a preset signal. Inputs are d,clock,and preset. Ouput is q. If clock=0, then q=d. If clock=1 or x, then q is unchanged. If preset=1, then q=1. If preset=0, then q is decided by clock and d signals. If preset=x, then q=x.

my answer:

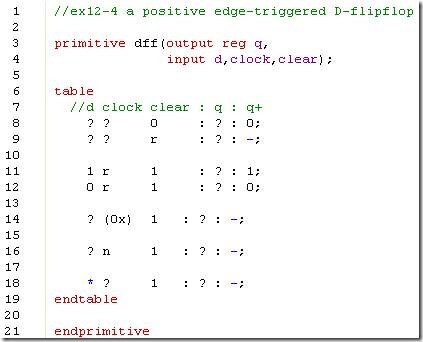

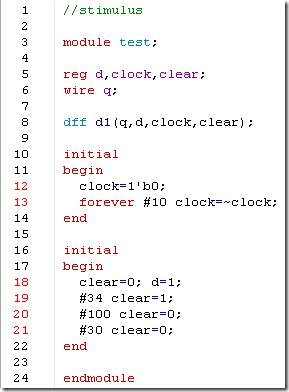

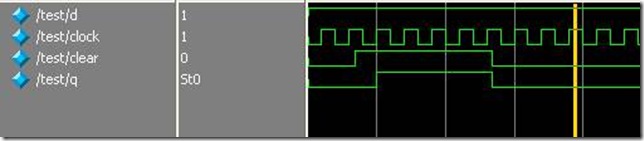

4. Define a positive edge-triggered D-flipflop with clear as a UDP. Signal clear is active low. Use example 12-9 as a guideline. Use shorthand notation wherever possible.

my answer:

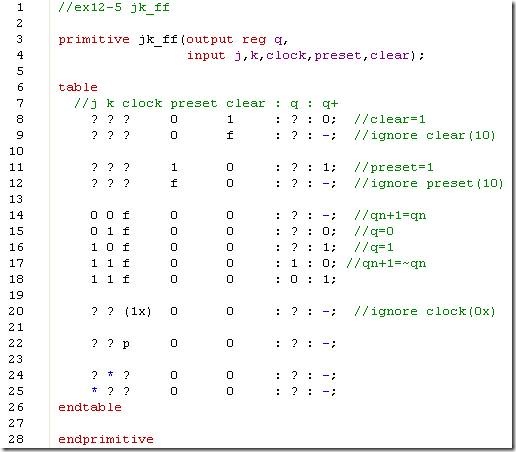

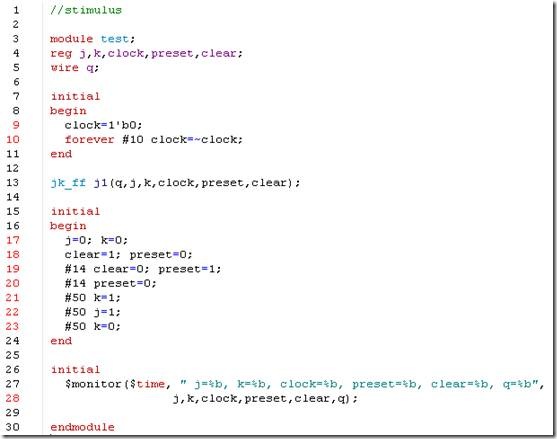

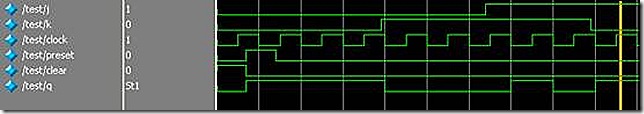

5. Define a negative edge-triggered JK flipflop, jk_ff with asynchronous preset and clear as a UDP. q=1 when preset=1 and q=0 when clear=1.

my answer:

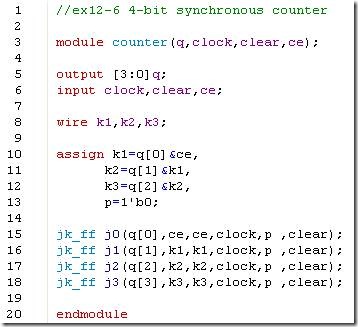

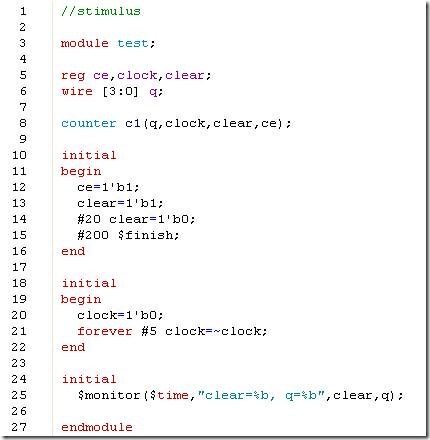

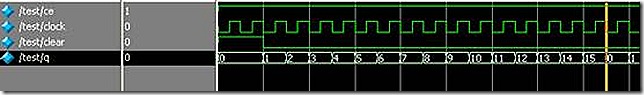

6.Design the 4-bit synchronous counter shown below. Use the UDP jk_ff that was defined above.

my answer:

Reference

Smair Palnitkar, <Verilog HDL: A Guide to Digital Design and Synthesis (2nd) >

浙公网安备 33010602011771号

浙公网安备 33010602011771号