【翻译】ModelSim指南II(ModelSim)(Verilog)(digital Logical)

4

项目

简介

本课将练习创建一个项目。

项目最少包括一个工作库和存储在.mpf文件里德状态集合。一个项目可能由以下几部分组成:

l HDL源文件或源文件索引

l 其他文件如说明或其他项目文档

l 本地库

l 全局库索引

本课用到的设计文件

本课范例是一个简单的8位二进制递增计数器和相应的测试台。其在如下位置:

Verilog – <install_dir>/examples/tutorials/verilog/projects/counter.v and tcounter.v

扩展阅读

用户手册章节:Projects。

创建一个新项目

1. 创建一个新目录并复制本课所用的设计文件。

2. 如果你刚学完上一课,ModelSim应该已经打开了,否则,启动ModelSim。

a) 选择File > Change Direcotry,将目录设为刚创建的目录。

3. 创建一个新项目。

a) 在主窗口选择File > New > Project。

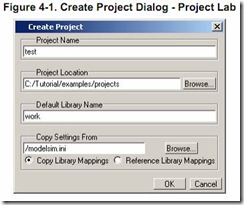

打开Create Project对话框,输入项目名,位置和缺省库名(图4-1)。也可以从选定的.ini文件参考库设置或直接复制到项目。缺省库用来保存已编译的设计单元。

b) 在Project Name区输入test。

c) 单击Browse按钮为项目指定路径。

d) 让Default Library Name设置为work。

e) 单击OK。

为项目添加对象

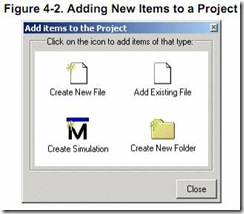

一旦完成新项目设置,就会出现一个空白的Project窗口和“Add items to the Project”对话框(图4-2)。从这个对话框可创建一个新的设计文件,添加文件,添加文件夹,或创建仿真配置(后面讨论)。

1. 添加2个文件。

a) 单击Add Existing File。

打开Add file to Project对话框(图4-3)。可在这个对话框里浏览和查找文件,指定文件类型,指定将被添加的文件的目录,和确定是否保持文件在当前位置还是拷贝到项目目录里。

b) 单击Browse按钮。打开“Select files to add to project”对话框,显示当前目录的内容。

c) Verilog:选择counter.v和tcounter.v并单击Open。

这将关闭“Select files to add to project”对话框并在“Add file to Project”对话框显示选定的文件(图4-3)。

d) 单击OK添加文件。

e) 单击Close忽略Project对话框的添加项。

现在在Project窗口应该看到两个文件。Status列的问号图标表示文件还没被编译或已编译过的源文件又修改了。其他列表示文件类型,编译次序,和修改日期。

编译设计

1. 编译文件。

a) 在Project窗口右击counter.v或tcounter.v,然后选择Compile > Compile All。

ModelSim编译所有文件并将Status列的符号改为绿色的核对标记。核对标记表示成功编译。如果编译失败,符号将是一个红色的“X”,那么就要在Transcript

窗口查看错误信息。

2. 查看设计单元。

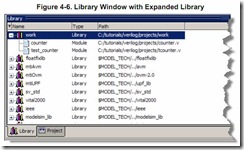

a) 单击Library标签(图4-6)。

b) 单击work库前的‘+’。

应该看到两个已编译的时间单元,它们的类型,和源文件的路径。

加载设计

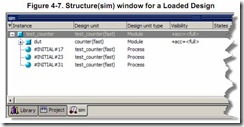

1. 加载test_counter设计单元。

a) 双击test_counter设计单元。

出现Structure (sim)窗口(图4-7)。

到这一步,通常可以像上一课一样运行仿真并分析或调试设计。目前,将继续学习项目。但是,在你加载test_counter时,先要关闭以前的仿真。

2. 结束仿真。

a) 选择Simulate > End Simulation。

b) 单击Yes。

用文件夹组织项目

如果有很多文件要添加到一个项目,可以用文件夹组织。可在添加文件之前或之后创建文件夹。如果在添加文件之前创建文件夹,在添加文件时可指定放置文件的文件夹(如图4-3)。如果是添加文件之后创建文件夹,可编辑文件,移动到那个文件夹。

添加文件夹

如前图4-2所示,在Add items to the Project对话框有添加文件夹的选项。如果关闭了这个对话框,可用菜单命令添加一个文件夹。

1. 添加一个新文件夹。

a) 在Projects Window右击并选择Add to Project > Folder。

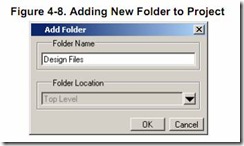

b) 在Folder Name去输入Design Files(图4-8)。

c) 单击OK。

在Project窗口显示Design Files文件夹(图4-9)。

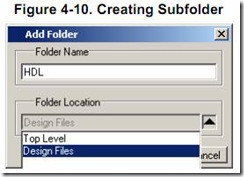

2. 添加一个子文件夹。

a) 在Project窗口任意地方右击并选择Add to Project > Folder。

b) 在Folder Name区输入HDL(图4-10)。

c) 单击Floder Location的下拉箭头并选择Design Files。

d) 单击OK。

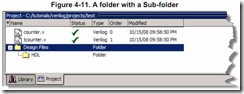

在Project窗口的Design Files文件夹前出现‘+’图标(图4-11)。

e) 单击‘+’查看HDL子文件夹。

移动文件到文件夹

如果没有把文件放在指定的文件夹,可用属性对话框移动到文件夹。

1. 移动tcounter.v和counter.v到HDL文件夹。

a) 在Project窗口选择tcounter.v和counter.v。

b) 右击并选择Properties.

打开Project Compiler Setting对话框(图4-12),有许多设置选项。

c) 单击Place in Folder的下拉箭头并选择HDL。

d) 单击OK。

选定的文件被移到HDL文件夹。单击HDL前的‘+’可以查看。

文件的Status列显示‘?’,因为移动了文件。项目不确定先前的编译是否仍有效。

仿真配置

配置相关联的设计单位和仿真选项。比如,每次加载tcounter.v都希望设置仿真器以ps和激活事件次序风险检测。通常,每次加载设计都要设置一次这些选项。有了仿真配置,可以设置并保存配置。

在Project窗口列出配置,可双击加载。

1. 创建一个新的仿真配置。

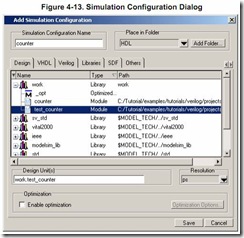

a) 右击Project窗口并选择Add to Project > Simulation Configuration。

打开Add Simulation Configuration 对话框(图4-13)。这个对话框里标签提供了几个仿真选项。查阅ModelSim手册可以了解每个选项。

b) 在Simulation Configuration Name区输入counter。

c) 从Place in Folder下拉项选择HDL。

d) 单击work库前的‘+’并选择test_counter。

e) 单击Resolution下拉项并选择ps。

f) 对于Verilog,单击Verilog标签并检查Enable hazard checking (-hazards)。

g) 单击Save。

现在,在Project窗口的HDL文件夹显示一个名为counter的仿真配置(图4-14)。

2. 加载仿真配置。

a) 在Project窗口双击counter仿真配置。

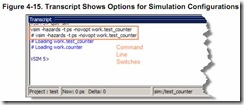

在Transcript窗口,显示等效的仿真配置的命令行(图4-15)。

本课小结

本课至此结束。继续之前,需呀结束当前仿真和关闭当前项目。

1. 选择Simulate > End Simulation。单击Yes。

2. 在Project窗口,右击并选择Close Project。

如果没关闭项目,它在下次启动ModelSim时将自动运行。

浙公网安备 33010602011771号

浙公网安备 33010602011771号