DDR3读写时序

DDR3读写时序

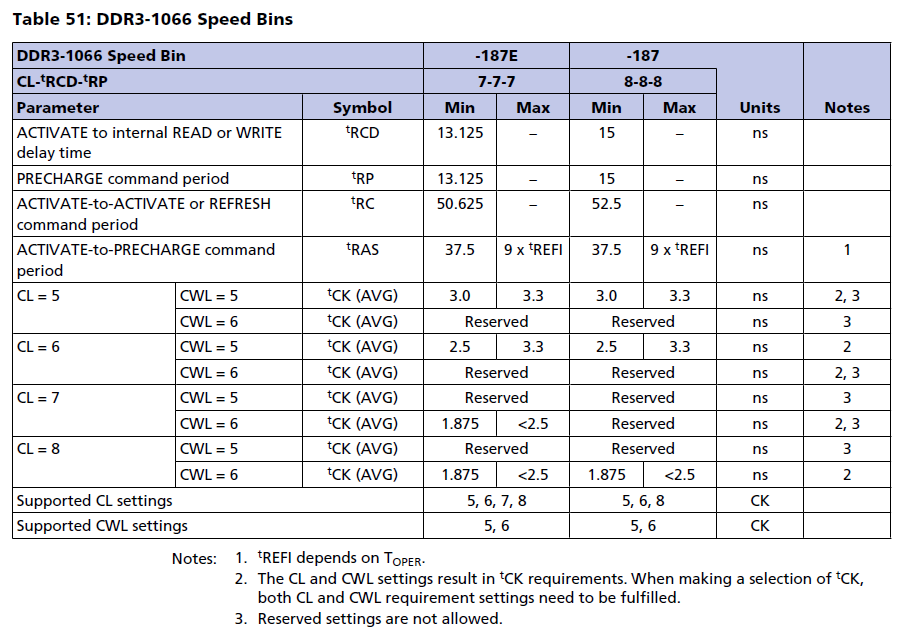

意思是说,当我们选择了187E芯片的时候,他所能支持的最大速率是1066MT/s,即DDR3的时钟频率是533MHz。此时tRCD=7 tRP=7 CL=7。

时钟周期是1.87ns因此CL=1.87*7=13.1ns。

tRCD指的是从ACTIVATE到READ或WRITE的时间

tRP指的是PRECHARGE的时间

CL指的是从读命令发出到读数据出现的时间

后文还会有CWL,这个参数是指从写命令发出到写数据出现的时间

在DDR3的Features中有上面的描述,可见CL是可以设置为5~11之间的数值的。

而CL的设置是与tCK(DDR3时钟频率)紧密相关的。从表51中就可以看出两者之间的关系

芯片是187E时,tCK周期可以在1.875ns到3.3ns之间变化,这样DDR3的时钟频率的变化范围就是533.33MHz到303.03MHz之间变化。

如果采用的是spartan6芯片,那么CWL一定是5,CL可以是5或6

2.MR寄存器设置参数

在calibration期间,MCB会向DDR3的MR0-MR3中写入一些参数,这其中就包括了CL和CWL。

3.仿真时序

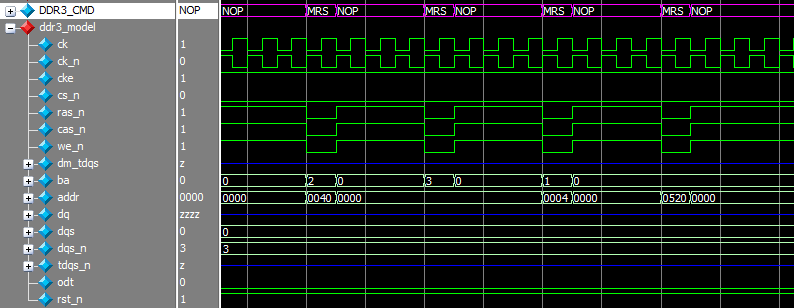

3.1 MRS时序

DDR3速度是800,时钟频率400MHz,周期2.5ns

四个寄存器的值分别是

MR0 : 13'h0520

MR1 : 13'h0004

MR2 : 13'h0040

MR3 : 13'h0000

CL设置为6,CWL设置为5

这两个值都是根据tCK的周期设定的

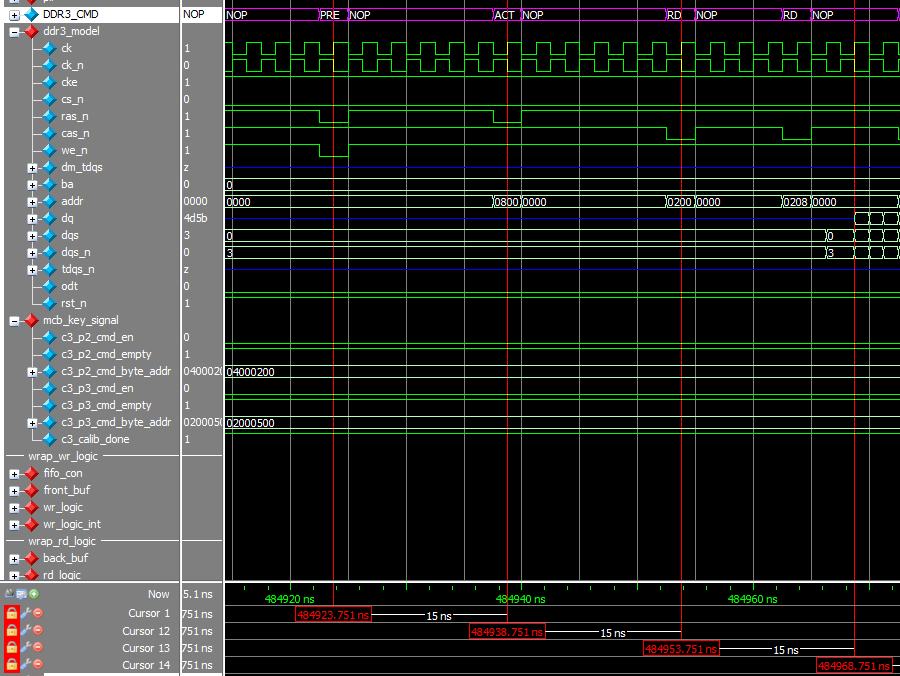

3.2 WR时序

从仿真图上可以看出

tRP=6CK

tRCD=6CK

CWL=5CK

3.3 RD时序

从仿真图上可以看出

tRP=6CK

tRCD=6CK

CL=6CK

3.3 时序分析

在仿真的时候,读写完一组之后没有auto-precharge,因此如果读写发生在不同的Row,读写穿插的时候,每次读写之前会有PRECHARGE+ACTIVATE的操作。

PRECHARGE命令先关闭先前打开的Row,ACTIVATE命令再打开需要读写的行

在表51中,tRCD和tRP只是规定了最小的时间,而没有规定最大的时间。从仿真上来看,这两个值都属于CL相同的。

4.自刷新时间

从上图可以看到,当使用1Gb容量的DDR3,温度在85°c以下时,每过7.8us都要自刷新一次,每次刷新时间在110ns到70200ns之间

上图是刷新时的仿真波形,REF命令之前现有一个PRE命令,当自刷新的时候,p3_cmd发出一个命令。REF命令110ns之后,出现ACT命令,这个是读命令之前必要的操作。因为之前所在bank中的row已经被关闭了。

5.bank row的打开与关闭时序

上图可见:

只有bank0中的row2048是打开的,读写操作连续访问这个地址。在读写交互的过程中,并没有PRECHARGE和ACTIVATE的时间,即读写可以连续进行。

上图可见:

在黄线之前,bank1中已经打开了row2048,在黄线位置,在bank0中代开了row4096。

可以在不同的bank中打开不同的行。

上图可见:

在黄线位置之前,在bank0中已经打开了row2048,在黄线的时候,打开了bank1中的row2048。在这一操作中,并没有关闭bank0中的row,可见可以在不同的bank中打开row。

而同一个row需要在不同bank中被打开。