数字逻辑课本习题三

一、单选题

(1) 1个触发器可记录1位二进制代码,它有( )个稳态。

A) 0 B) 1 C) 2 D) 3

(2) 对于 $JK$ 触发器,若 $J=K$ 则可完成( )触发器的逻辑功能。

A) D B) RS C) T D) T

注1:T触发器是只有翻转功能的触发器,即每一个时钟边沿到来时,触发器状态变化一次。

注2:由JK触发器的特性函数和T触发器的特性函数即可得。

(3) 对于 $JK$ 触发器,若 $K = \overline J $ 则可完成( )触发器的逻辑功能。

A) D B) RS C) T D) T

(4) 基本RS锁存器输入端禁止的情况为( )。

A) $R=1, S=1$ B) $\overline R = 1,{\rm{ }}\overline S {\rm{ }} = {\rm{ }}1$ C) $R=0, S=0$ D) $RS=0$

(5) 触发器的异步置位端 $Set, Clr$ 不能同时取值为( )。

A) $Set=1, Clr=1$ B) $Set=0, Clr=0$ C) $Set=1, Clr=0$ D) $Set=0, Clr=1$

(6) JK触发器在J、K端同时输入高电平时,处于( )功能。

A)置0 B)置1 C)保持 D)翻转

(7) 时序逻辑电路的特点是( )。

A)仅由门电路组成 B)无反馈通路 C)有记忆功能 D)无记忆功能

(8) 4个触发器构成的8421BCD码计数器共有( )个无效状态。

A) 6 B) 8 C) 10 D) 4

注:见书本P111

(9) 4位二进制计数器计数容量为( )。

A) 4 B) 8 C) 16 D) 10

注:$n$ 个触发器构成的计数器,计数容量为 ${2^n}$。

(10)要构成二十进制计数器,至少需要( )个触发器。

A) 2 B) 3 C) 4 D) 5

见上题

(11) $N$ 进制计数器的特点是设初态后,每( ) $Clk$,计数器又重回初态。

A) $N-1$ B) $N+1$ C) $N$ D) $2N$

(12) 将两片4位二进制同步加法计数器芯片级联,最大可构成( )进制计数器。

A) 16 B) 255 C) 256 D) 100

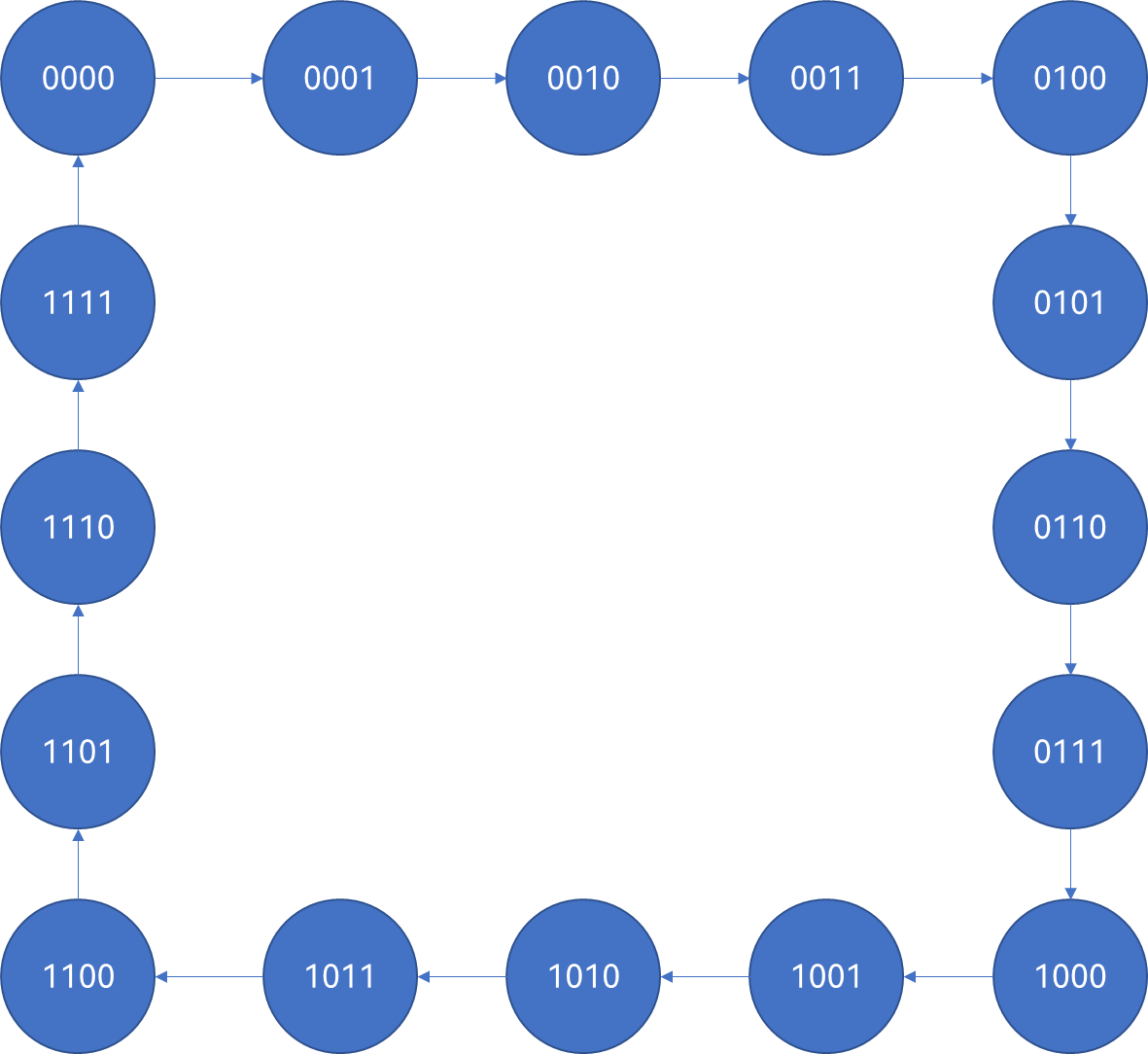

(13) 由4个触发器组成的二进制加法计数器,当初始状态为1010时,经过( )个Clk脉冲,计数器的状态会变为0101。

A) 4 B) 10 C) 11 D) 16

【解析】也就是初始状态为10,末态为5,4位二进制加法计数器一个周期为16,所以6+4=11。

(14)触发器符号中Clk输入端的小圆圈表示( )。

A)高电平有效 B)低电平有效 C)上升沿触发 D)下降沿触发

(15)对于下图所示的左移寄存器,若 ${Q_0} - {Q_3}$ 原来的状态是0111,${S_{in}}=0$,Clk上升沿之后, ${Q_0} - {Q_3}$ 的状态变成( )。

A) 0111 B) 1110 C) 0011 D) 0110

二、判断题

(1)触发器有互补的输出,通常规定 $Q=1$、$\overline Q = 0$ 时称触发器为0态。×

(2)D触发器的特性方程为 ${Q^{n + 1}} = D$,与 ${Q^{n}}$ 无关,所以它没有记忆功能。×

(3)对于边沿JK触发器,在Clk为高电平期间,当 $J=K=1$ 时,状态会翻转一次。×

(4)经过有限个Clk,可由任意一个无效状态进入有效状态的计数器是能自启动计数器。

(5)计数器在电路组成上的特点是有Clk输入,可无其他输入信号。

(6)要设计一个同步的计数容量为5的计数器,需要5个触发器。×

(7)采用异步清零方式的计数器,当清零信号到来时会立刻产生清零效果。

(8)采用同步清零方式的计数器,当清零信号到来时会立刻产生清零效果。×

(9)时序电路中如果存在无效状态,应检查是否能自启动。

(10) Moore型时序电路的输入信号会直接影响输出。×

浙公网安备 33010602011771号

浙公网安备 33010602011771号