在Quartus16.1下使用ModelSim对vhdl写的项目进行仿真

首先新建一个工程并编写VHDL文件

我编写的是decoder3_8

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.all; entity decoder3_8 is port( a,b,c,en:in std_logic; y:out std_logic_vector(7 downto 0)); end decoder3_8; architecture rtl of decoder3_8 is signal data:std_logic_vector(2 downto 0); begin data<=c&b&a; process(data,en) begin if(en='1') then case data is when "000"=>y<="11111110"; when "001"=>y<="11111101"; when "010"=>y<="11111011"; when "011"=>y<="11110111"; when "100"=>y<="11101111"; when "101"=>y<="11011111"; when "110"=>y<="10111111"; when "111"=>y<="01111111"; when others=>y<="11111111"; end case; else y<="11111111"; end if; end process; end rtl;

编写好文件之后编译通过。

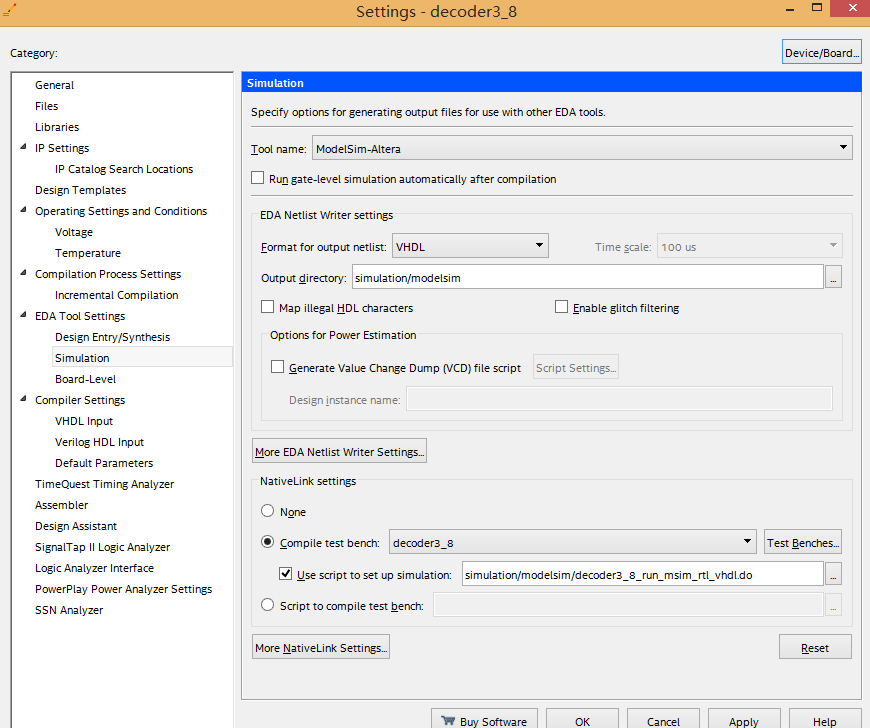

然后Assignment->Settings;选择EDA Tool Settings中的Simulation

Too lName选择ModelSim 或者ModelSim-Altera

NativeLink settings选择第二项 Compile test bench

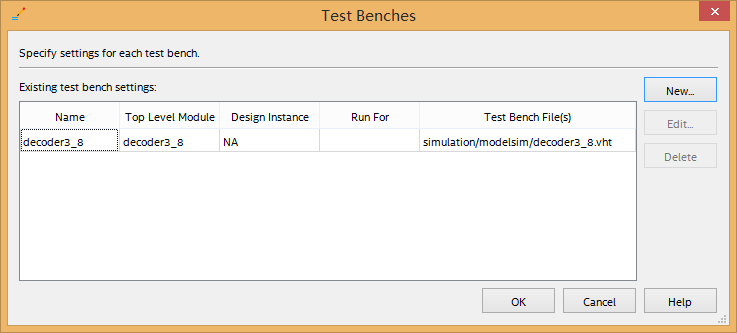

单击Test Benches

单击New

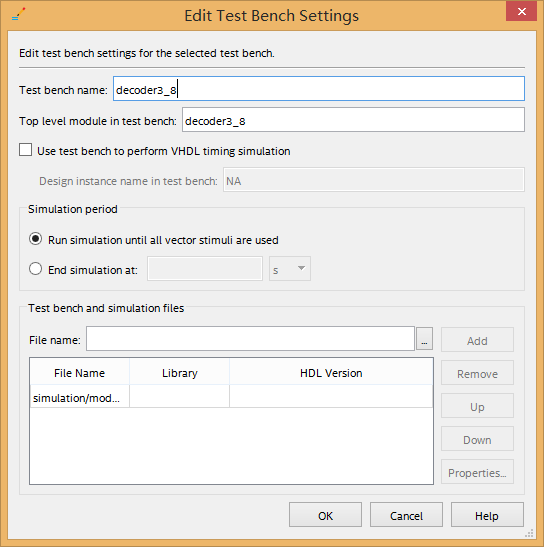

输入test bench name

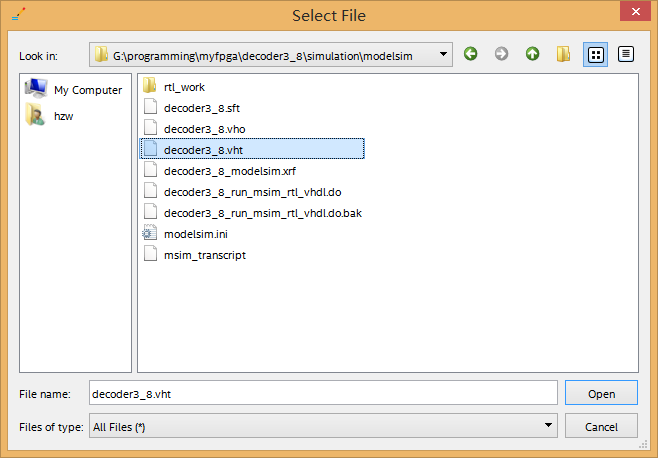

在file name中选择.vht文件

如果没有该文件,则通过

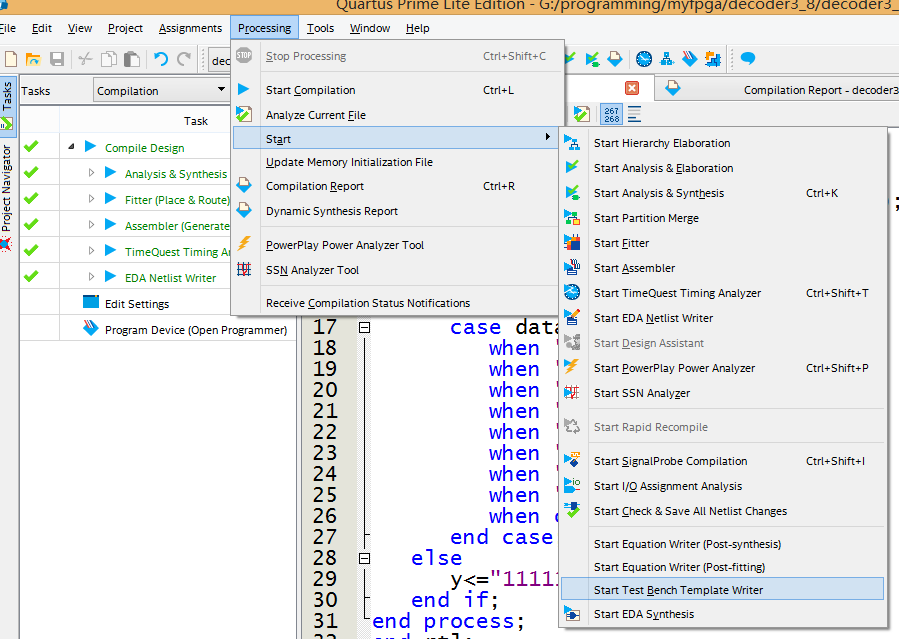

Processing->Start->Start Test Bench Template Writer进行生成

选择完成如下图

Ok之后选择Use script to set up simulation ,选择.do文件,如果没有

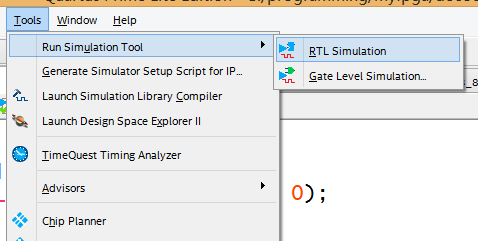

则通过Tools->Run Simulation Tools->RTL Simulation先进行仿真,然后退出重新选择.do文件即可

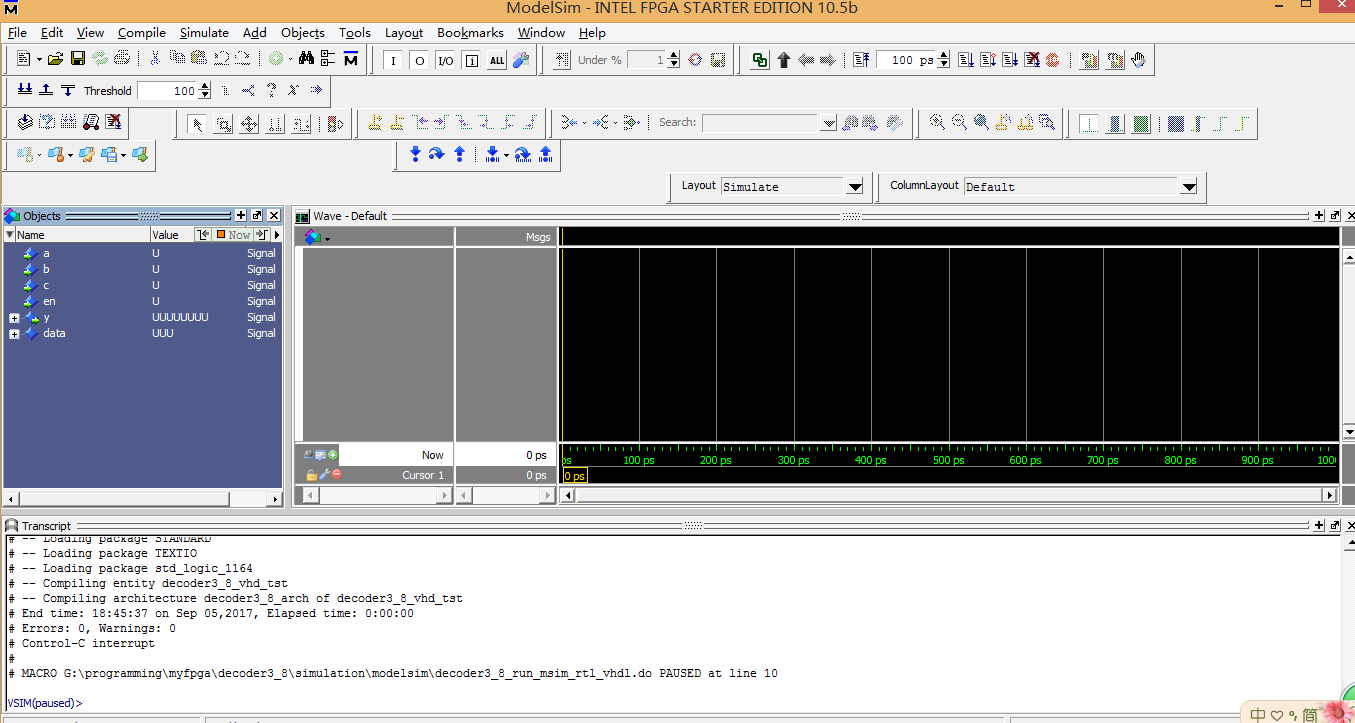

成功出现仿真图