Xilinx VIvado学习-01 数值处理之乘法(有符号)

Verilog 数值处理,在处理减法的时候,需要注意溢出问题。

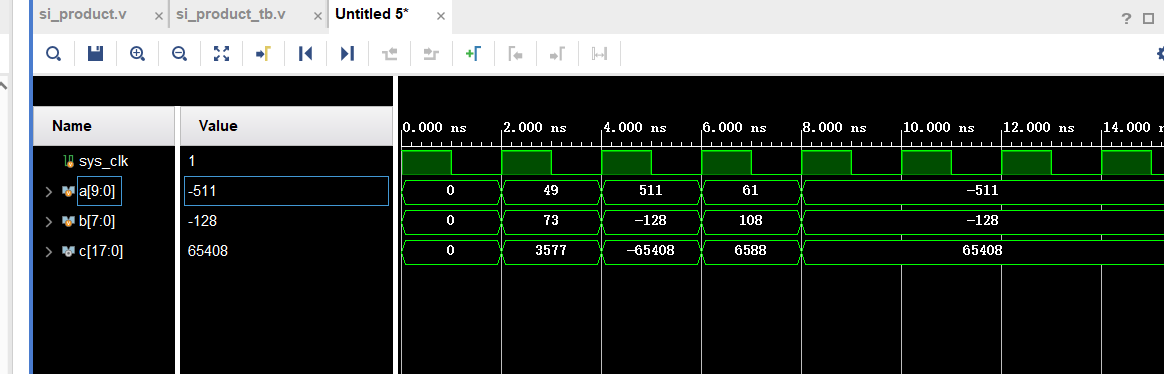

实例:a*b=c

1 module si_product( 2 input signed [9:0] a, 3 input signed [7:0] b, 4 output signed[17:0] product 5 ); 6 assign product=a*b; 7 endmodule

仿真代码:

1 module si_product_tb; 2 reg sys_clk; 3 reg signed [9:0] a; 4 reg signed [7:0] b; 5 wire signed [17:0] c; 6 7 initial sys_clk =1; 8 always #1 sys_clk = ~sys_clk; 9 //a = 8'h7f; 10 //b = 8'h2; 11 12 si_product si_product( 13 .a (a), 14 .b (b), 15 .product(c) 16 ); 17 initial begin 18 a=0;b=0; 19 #2 20 a=49;b=73; 21 22 #2 23 a=511;b=-128; 24 #2 25 a=61;b=108; 26 #2 27 a=-511;b=128; 28 end 29 endmodule

Vivado仿真结果如下:

两个N位*M位相乘 积用N+M+1位来表示。

分类:

FPGA

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 25岁的心里话

· 闲置电脑爆改个人服务器(超详细) #公网映射 #Vmware虚拟网络编辑器

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· 零经验选手,Compose 一天开发一款小游戏!

· 一起来玩mcp_server_sqlite,让AI帮你做增删改查!!