3.2 Verilog HDL描述方法与结构描述

一、描述方法

Verilog HDL是一种能够在多个级别对数字电路和数字系统进行描述的语言,可以是实际不同级别的抽象,这些抽象级别可以分为以下几个方面:

①系统级(System Level)②功能模块级(Functional Model Level)③行为级(Behavio Level)④寄存器传输级(Register Transfer Level,RTL)⑤门级(Gata Level)

其中前三种属于高级别的描述方法,门级描述主要用逻辑门以及逻辑之间的连接来构筑电路模型。

Verilog HDL中有下面4种描述设计的方法:

①结构描述 ②行为描述 ③数据流描述 ④混合描述

二、结构描述

结构描述的方式主要有以下几种形式:

①调用Verilog内置门元件(门级结构描述):调用Verilog内部基本门级元件对电路元件进行描述,这种情况下的模块都是独立模块

②调用模块:在多层次结构电路设计中,顶层模块调用底层模块对硬件电路进行描述,这种情况下的模块也是独立模块

③用户自定义元件UDP(也在门级):由设计者自己定义元件的功能

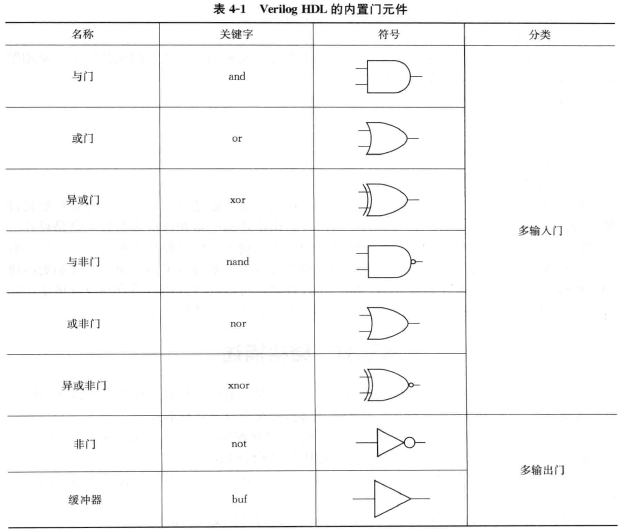

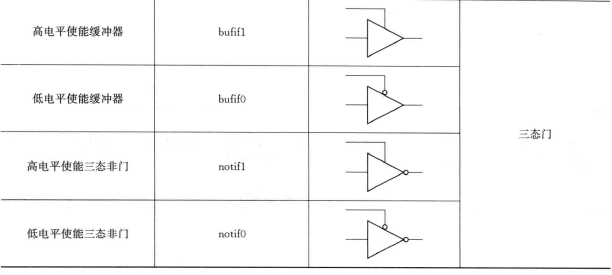

1.Verilog HDL内置元件

Verilog HDL内置基本元件主要是门元件(Gate-Level Primitive)和开关级元件(Switch-level Primitive)。

基本门主要分为以下几类: