多周期路径及set_multicycle_path详解

参考博文:多周期路径及set_multicycle_path详解_Jackiezhang1993的博客-CSDN博客_multicycle path

默认情况下综合工具会把每条路径定义为单周期路径,即源触发器在时钟的任一边沿启动(launch)的数据都应该由目的触发器在时钟的下一上升沿捕获(capture)。

有的设计可能存在时序例外(timing exceptions),如多周期路径、虚假路径等。数据从起点到终点的传输时间需要一个时钟周期以上才能稳定的路径,这类路径被称为多周期路径。在设计中很多地方都有涉及多周期路径,比如当个两个触发器之间的逻辑如果一个周期执行不完,这种情况一般有两个解决方案:

①插入流水线使得组合逻辑打散 ;

②使用使能信号控制,几个周期读取一次数据。

方法2就需要设定multi-cycle path,方法2和1之间是有区别的。方法1数据的吞吐量更大,方法2牺牲了数据吞吐量,但是设计中有的地方对吞吐量没有要求是可以使用这种方法的。

一、set_multicycle_path命令

命令格式如下:

set_multicycle_path

path_multiplier

[-setup|-hold]

[-start|-end]

[-from from_list]

[-through through_list]

[-to to_list]

path_multiplier:默认值setup时为1,hold时为0;

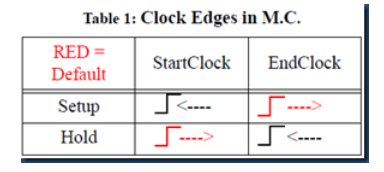

setup|hold:表明多周期路径设置是对setup(max_delay)或者是hold(min_delay),setup时默认移动capture_clk,hold时默认移动launch_clk;

start:表示强制移动的为start clock即launch clock;

end: 表示强制移动的为end clock即capture clock。

ps:当start clock和end clock同频时,不用指定start/end,因为移动哪一个都一样效果。

二、4种不同场景

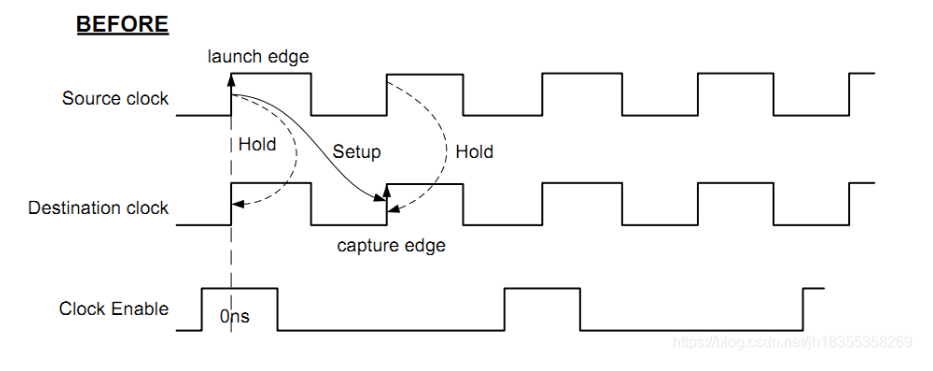

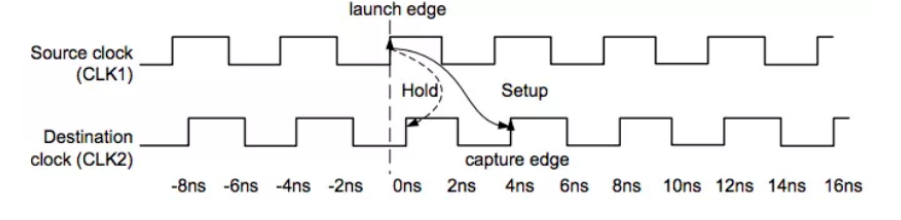

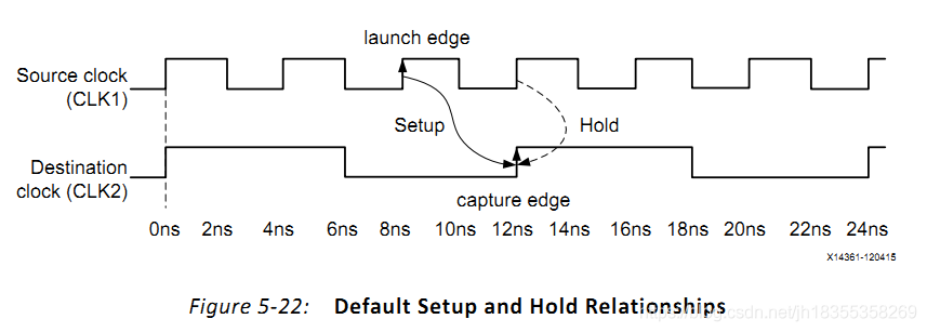

1、同频同相

如下图所示,时钟上升沿对齐,且默认的STA检查情况为单周期:

此时的multicycle默认设置如下(单周期路径默认关系):

set_multicycle_path 1 -setup -from CLK1 -to CLK2

set_multicycle_path 0 -hold -from CLK1 -to CLK2

即默认情况下:setup检查是从launch_clk的一个上升沿到capture_clk的下一个上升沿,hold检查是从launch_clk的一个上升沿到capture_clk的捕获沿的前一个沿。

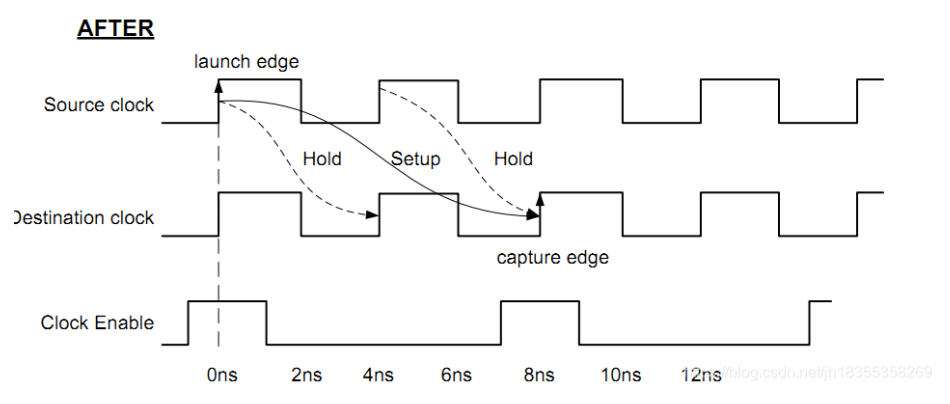

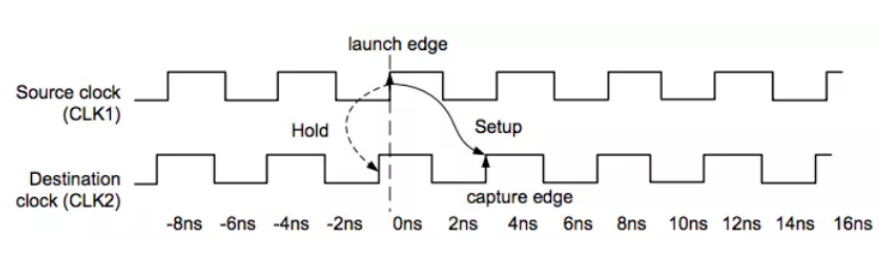

现进行设置:set_multicycle_path 2 -setup -from CLK1 -to CLK2 ,对应的时序检查变为(capture_clk右移(2-1)个周期):

此时hold检查还是默认设置,即跟随capture_clk向右移动1个period。

根据STA中的“Hold Relationship”,hold检查过于宽松,需要设置:

set_multicycle_path -hold 1 -from CLK1 -to CLK2

这样hold检查向后(左)移动(延迟)1个period,由于-hold默认移动launch_clk,也就是launch_clk向前(向右)移动了1个时钟周期(也可看做capture_clk向左移动了1个时钟周期),如下图:

补充:对于多周期路径,为什么要将保持检查沿恢复到初始位置?

对于上述clk的周期为T=4ns,现在若只设置set_multicycle_path 2 -setup -from CLK1 -to CLK2后,由于hold检查比setup检查往左一个时钟周期,则要求数据到达触发器的时间范围为:[4ns+Th,8ns-Ts],此时由于数据采集每2个时钟周期一次,这样对于保持关系过于苛刻,实际数据可到达的时间范围是[0ns+Th,8ns-Ts]。所以,可以设置set_multicycle_path 1 -hold -from CLK1 -to CLK2,这样使得数据到达触发器的时间范围变为上述范围(Th为保持时间,Ts为建立时间),这样多周期路径部分电路的优化范围就变大了。

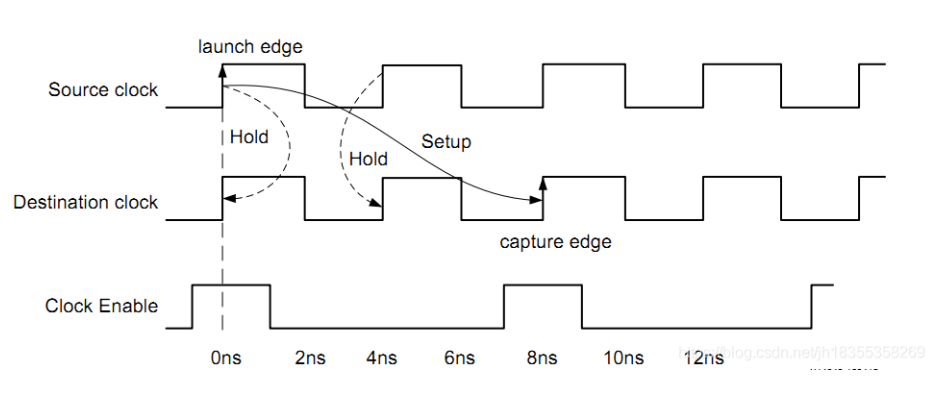

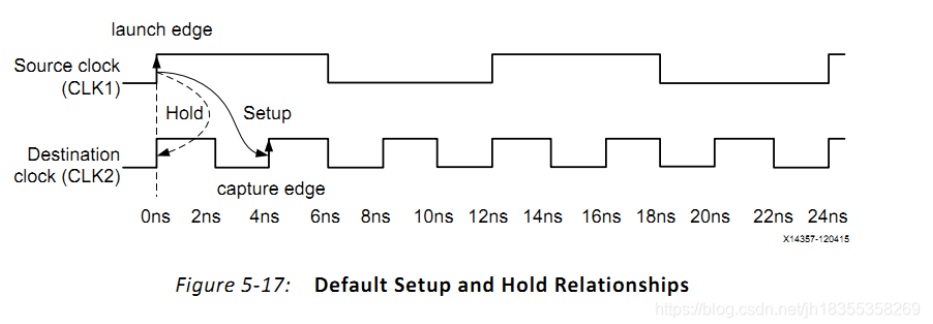

2、同频异相

①capture_clk比launch_clk稍晚一点(0.3ns),默认检查关系如下:

此时时钟周期为4ns,建立检查为0.3ns过小,而保持检查3.7ns过于丰富,时序很难收敛,需设置如下(hold检查的多周期路径无需设置,可以满足):

set_multicycle_path 2 -setup -from CLK1 -to CLK2

②目的时钟超前发送时钟0.3ns

此时建立检查3.7ns,保持检查0.3ns,比较正常无需增加约束。

3、慢到快

默认检查关系(最悲观):

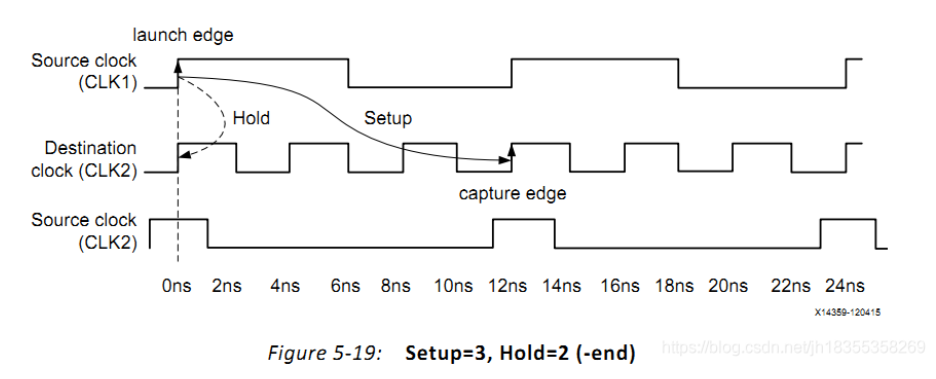

默认设置:

set_multicycle_path 1 -setup -end -from CLK1 -to CLK2

set_multicycle_path 0 -hold -start -from CLK1 -to CLK2

现将setup放松2个周期检查,设置如下:

set_multicycle_path 3 -setup [-end] -from CLK1 -to CLK2

此时-setup默认右移capture_clk,增加-end便于可读性。

此时为遵守严谨的保持关系,需设置如下:

set_multicycle_path 2 -hold -end -from CLK1 -to CLK2

此时注意:

①由于launch_clk和capture_clk的频率不一样,所以需要用-start/end来指定移动的clk,这样PT检查才不会出错。

②由于-hold默认向右移动launch_clk,现在加上-end后即为指定向左移动capture_clk。

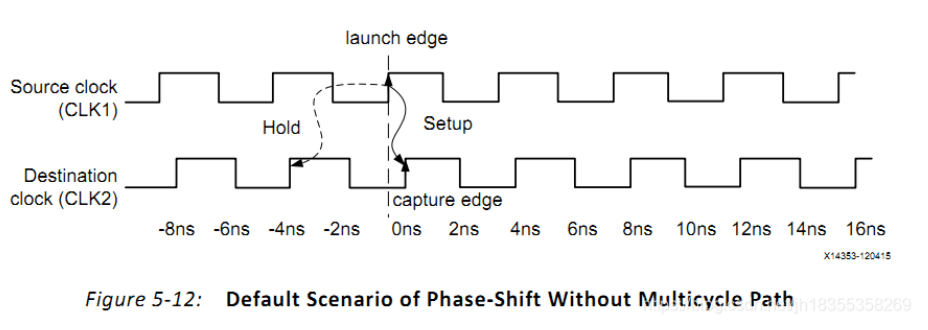

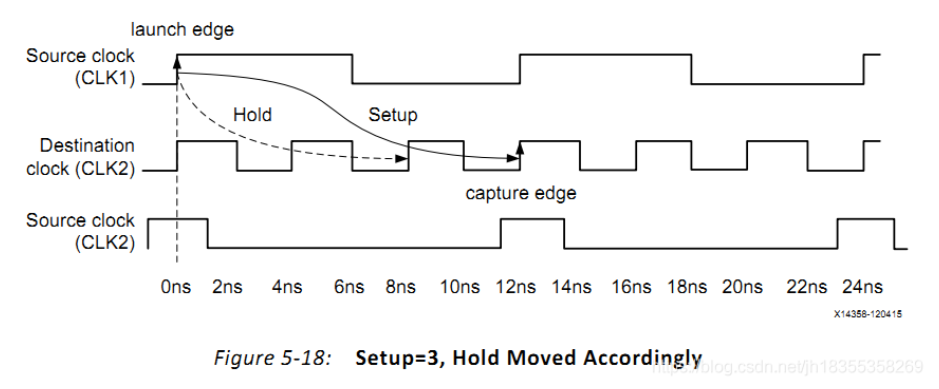

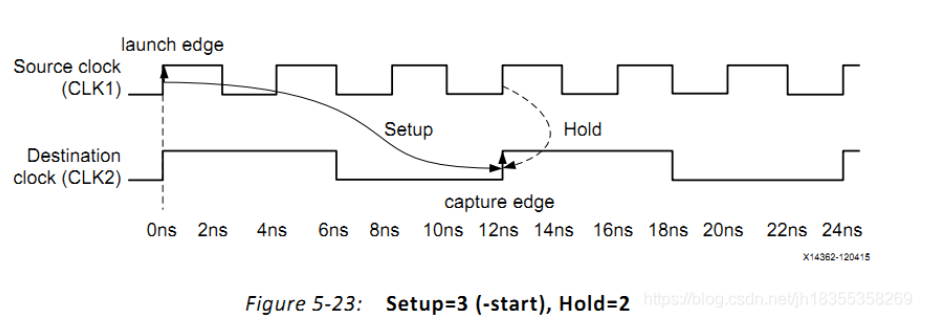

4、快到慢

时钟关系如下图,且分析最悲观情况下的建立/保持关系:

此时默认设置还是:

set_multicycle_path 1 -setup -end -from CLK1 -to CLK2

set_multicycle_path 0 -hold -start -from CLK1 -to CLK2

现在放松2个周期检查,设置如下:

set_multicycle_path 3 -setup -start -from CLK1 -to CLK2

根据严谨的保持关系,需要设置hold检查如下,其中-hold参数默认向右移动launch_clk,但由于时钟频率的不同建议加上-start增加易读性:

set_multicycle_path 2 -hold [-start] -from CLK1 -to CLK2

5、总结

①-setup/hold参数默认分别向右移动EndClock/StartClock;

②为了将保持沿恢复到初始位置,保持因子比建立因子小1;(异相情况除外)

对于N倍频同步时钟:

③建立数字等于两个时钟频率比N;

④将较快的时钟指定为设置对象

⑤需要使用-start/end参数对应指定强制移动StartClock/EndClock,若与setup/hold参数默认相反,则被强制移动的时钟移动方向向左;