Setup 和Hold (建立时间和保持时间)理解

参考博文:https://blog.csdn.net/wordwarwordwar/article/details/80160772

STA分析是基于同步电路设计模型的,在数据输入端,假设外部也是同时钟的寄存器的输出并且经过若干组合逻辑进入本级,而输出也被认为是驱动后一级的同时钟的寄存器。在不设置约束的情况下,纯组合逻辑的输入->输出不得超过一个T,否则也会被认为是Timing violation.

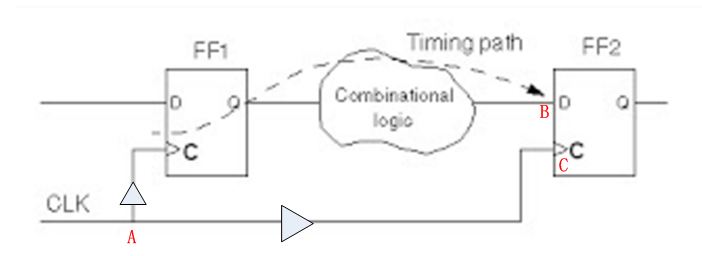

1. Timing path

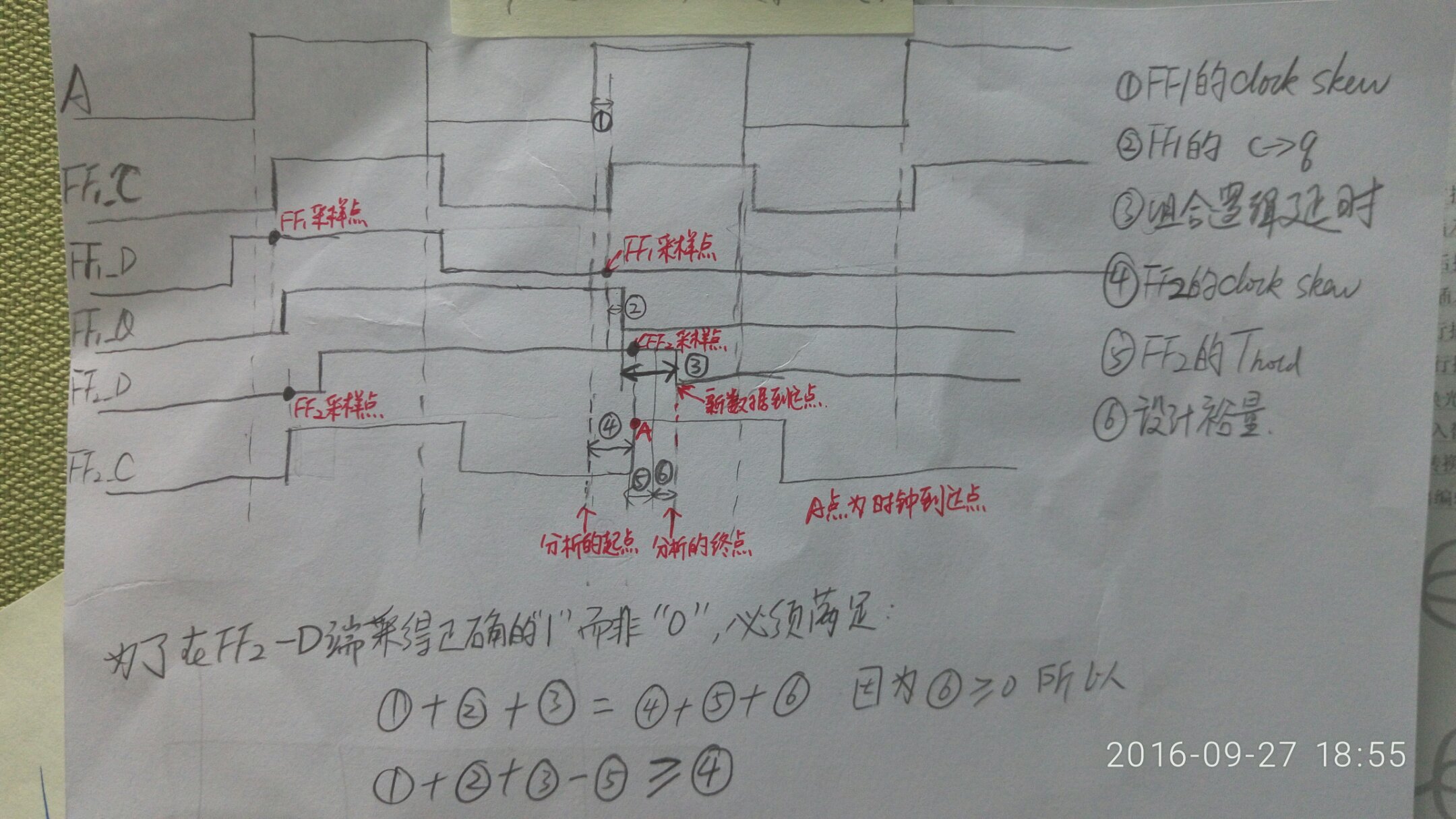

Timing path就是时间线。Timing就是从起始位置的时间点到终点位置的时间点之间的时间长度。Path是指跟位置相关,即时间起始或终点的位置。Timing path就是某位置的某一时间点到另一位置的某个时间点。对于DFF来说,上升沿类似于一瞬间的脉冲,只有在这短短的一瞬间,数据才允许通过。对于DFF来说,有两个输入点:数据D和时钟CK,有一个输出点:数据Q。由于是时间比较,所以对于D和CK一定要有一个共同的起始时间点,如下图中的A点出现clk上升沿的时刻。如下图,假设我们分析DFF2的数据和时钟到达的时间。二者共同的出发点是A的上升沿,因为A位于时钟通路上,FF1的时钟经过A点到达FF1-C点,在FF1-C上升沿打开FF1,然后数据才能从FF1-Q输出,进而传递到FF2-D。在A点, FF2的时钟沿经过clock tree,达到FF2-C点。所以数据走过的路程是:

Data path: A->clk_tree_buf1->FF1-C -> FF1-Q -> Comb_logic -> B

而对于FF2来说只要满足下个周期的上升沿能够采样即可,所以时钟到达FF2-C的路径是:

Clk path: A -> clk_tree_buf2-> C.

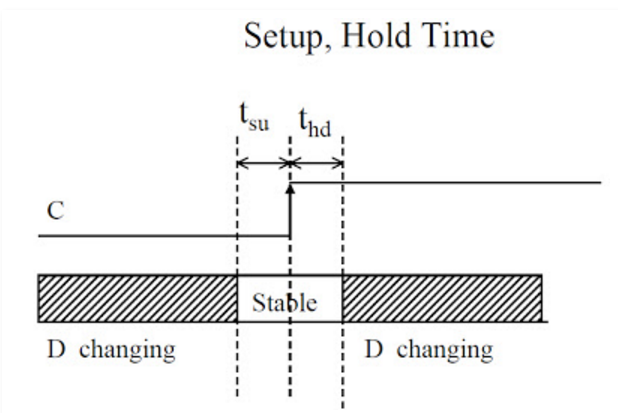

2. 什么是建立时间和保持时间?

对于某个DFF来说,建立时间和保持时间可以认为是此器件固有的属性。有关DFF的内部结构及setup和hold时间对应的逻辑门会在其他文章中进行细致描述。

在理想情况下,只要在时钟沿来临时,有效数据也来临(时钟沿之前或同时),则能够正确采集到数据;而在时钟沿之后(或同时),即使数据发生变化,也不会影响DFF的输出了。然而在实际中,上升沿打开开关需要时间,逻辑门的状态改变(电容充放电等)都需要时间,因此数据的采集是需要一定时间的,在这个时间内数据不能发生变化。上升沿时候开关关闭也需要时间,如果在这个时间段内数据有变化的话,那么新数据就有可能被传递到下一级,进而发生错误,所以数据必须保持一定时间不变。(细节部分可以参考DFF的内部结构)。

总而言之在DFF的输入端口上看,

- 在clk上升沿来之前,数据必须提前一个最小时间量“预先准备好”,这个最小时间量就是建立时间;

- 在clk上升沿来之后,数据必须保持一个最小时间量“不能变化”,这个最小时间量就是保持时间。

3. 建立和保持时间要求、及其公式

满足建立和保持时间要求,电路状态改变就是正确的,电路功能就不会发生错误;如果不满足,电容就没有足够的时间充放电,造输出点的电平可能既非0也非1,造成“亚稳态“输出。如果前级驱动够强劲,电路就能按照趋势变化下去,一定时间后该点的值就会变化为“正确值”,如果驱动不够强劲,电路就会恢复之前的值,最终得到何值是不可控的,所以我们要避免亚稳态。在使用DFF时,必须满足其建立时间和保持时间的要求。

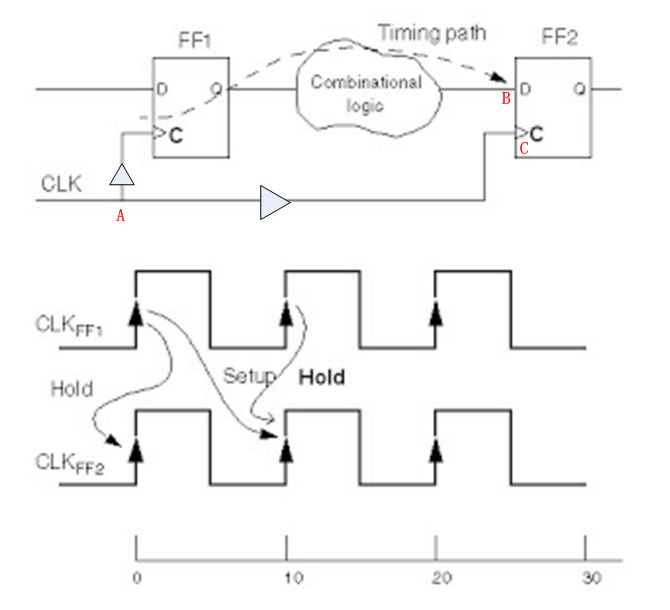

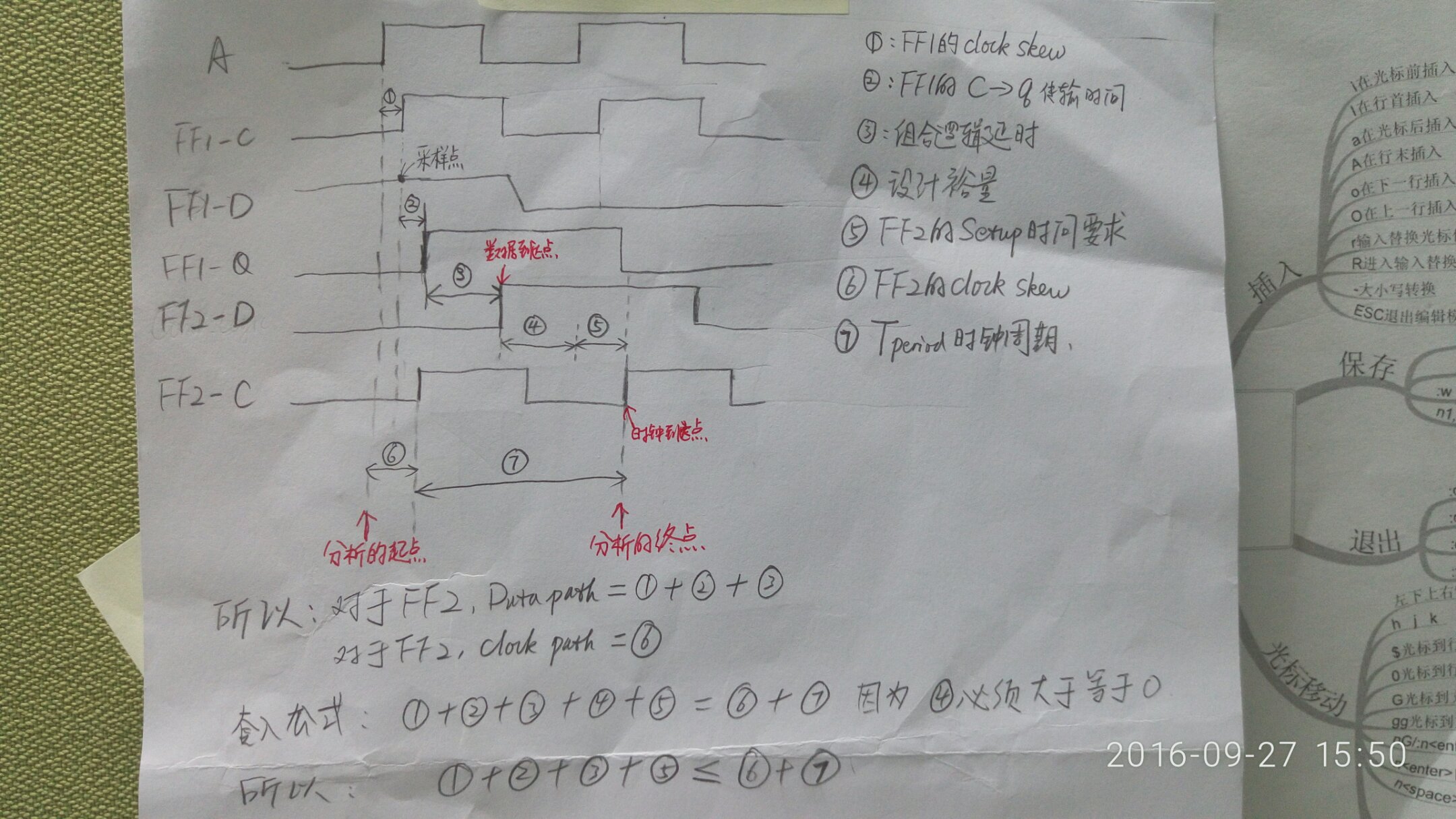

现在在回头分析data path和clk path,假设t0时刻FF1采集到数据并传递给FF2,那么FF2只要在t10上升沿采到数据即可,所以数据有一整个Tperiod的时间来传递到FF2-D端。因为要满足建立时间要求,所以对于FF2来说,数据要比时钟“走得快”:

Tdata_path+ Tsetup <= Tclk_path+ Tperiod

所以

Tclk_delay_FF1 + Tc->q_FF1+ Tcomb_logic+ Tsetup<= Tclk_delay_FF2 +Tperiod

在分析STA时,不满足此公式的即为setup violation。对应时序图的分析,见下图:

保持时间比较难理解,其实质是当前时钟沿的FF1输出不能太快在当前沿到达FF2。以上图为例,即在t10时刻,为防止FF1采到的新数据太快到达FF2而“冲掉”原来的正确数据,数据必须要在一定时间之后才允许到达,所以保持时间分析,分析的是FF1和FF2的同一个时钟沿。因为datapath和clk_path要满足保持时间要求,所以

Tdata_path– Thold >= Tclk_path

所以:

Tclk_delay_FF1 + Tc->q_FF1+ Tcomb_logic– Thold>= Tclk_delay_FF2

在STA分析时,不满足此公式的即为Holdviolation。

其中Tclk_skew =Tclk_delay_FF2– Tclk_delay_FF1. 这条公式在分析Tskew时用得上。

对应于时序图,见如下图的分析:

4. 实际电路的Setup和Hold公式及violation分析

因为在不同的情形下,例如不同的温度,电压,loading等等,每一段电路的delay是不同的,所以对于同一段电路,其delay可以在如下范围中:

Min_delay<= Delay <= max_delay

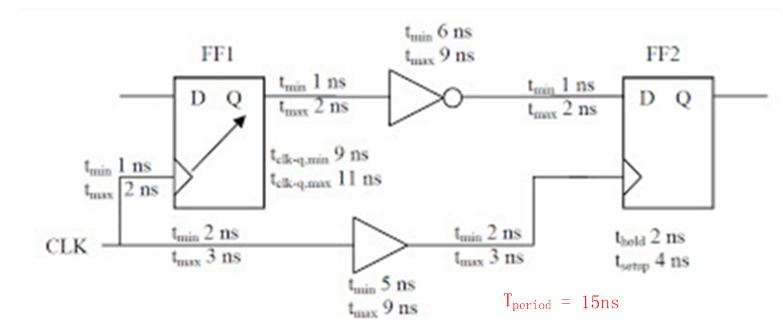

如下图:

建立时间

公式为: Tclk_delay_FF1 + Tc->q_FF1+Tcomb_logic+ Tsetup <= Tclk_delay_FF2 + Tperiod

应该满足MAX_data_path_delay + Tsetup <= MIN_clk_path_delay + Tperiod,才能保证电路是可靠的。所以在实际电路中:

Tdata_path_max+ Tsetup <= Tclk_path_min+ Tperiod

对应上图,该公式应该是:

2ns+ 11ns + 2ns + 9ns + 2ns + 4ns <= 2ns + 5ns + 2ns + Tperiod

所以: 30 <= 9 + 15.因为违反了该公式,所以该电路出现了setup violation。

保持时间

公式为: Tclk_delay_FF1 + Tc->q_FF1 + Tcomb_logic –Thold>= Tclk_delay_FF2

应该满足MIN_data_path_delay – Thold>= MAX_clk_path_delay.才能保证电路是可靠的。所以在实际电路中:

Tdata_path_min- Thold >= Tclk_path_max

对应上图,该公式应该是:

1ns +9ns + 1ns + 6ns + 1ns – 2ns >= 3ns + 9ns + 3ns

所以: 16ns >= 15ns,满足公司要求,所以该电路无holdviolation。

在某些电路中,可以认为clk tree上面没有延迟,可以认为wire没有延迟,那么setup和hold公式就得到简化。