ARMv7-A 处理器窥探 —— Memory Model

1、Memory Type

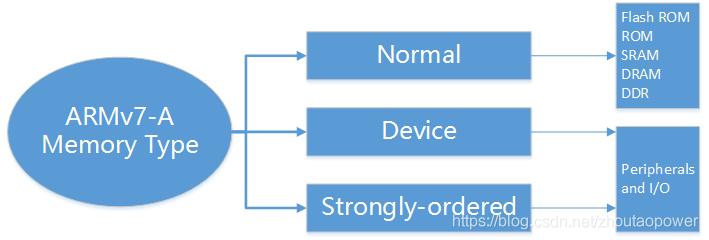

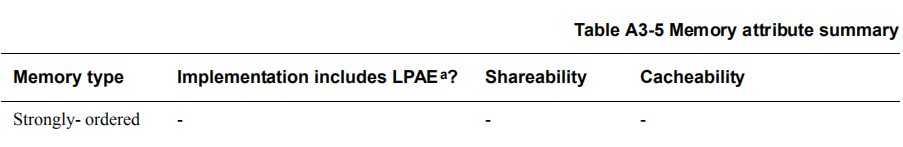

ARMv7-A 处理器中,将 Memory定义为几种类型(Memory Type):

- 1、Strongly-ordered;

- 2、Normal;

- 3、Device;

它的定义如下所示:

注意:这里的 Memory 指的不是内存,可以翻译成储存器,是地址空间的概念;

普通的内存(RAM),只读的内存(ROM),这些都属于 Normal Type 的范畴;

外设和I/O,这些属于 Device 和 Strongly-ordered 范畴;

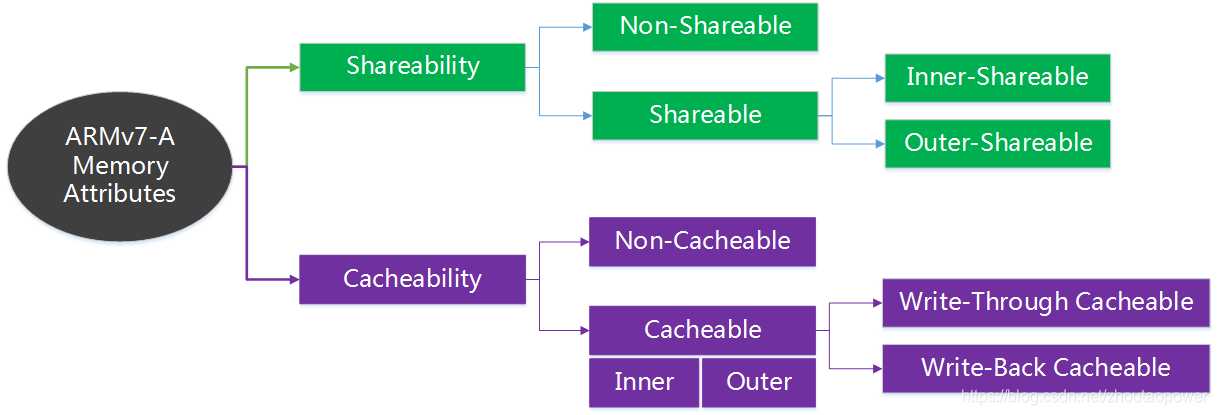

2、Memory Attributes

对于地址空间来说,每种地址空间,ARMv7-A 使用 attribute 来描述这个存储器地址的属性,总的属性分为两种:

- 1、shareability;共享属性

- 2、cacheability;缓存属性

它们描述了存储器是否可以共享,或者是否可以过cache;

2.1、Shareability Attributes

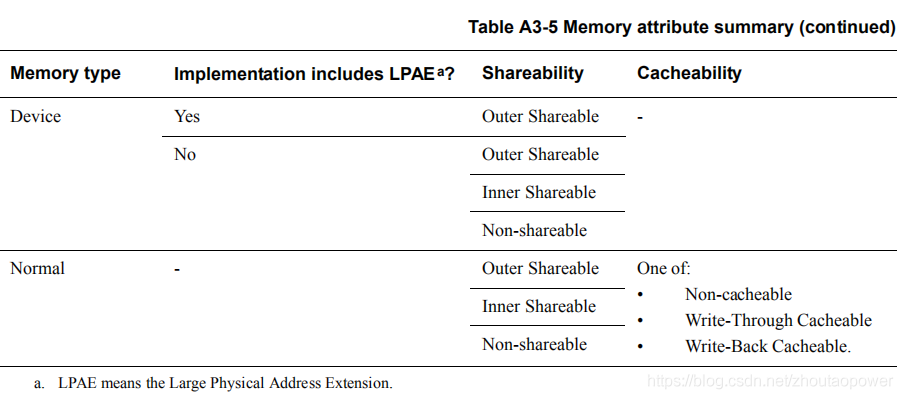

Shareability 共享属性用于描述存储器地址空间是否可以共享;只对 Normal Type 类型和 Device 类型有效;

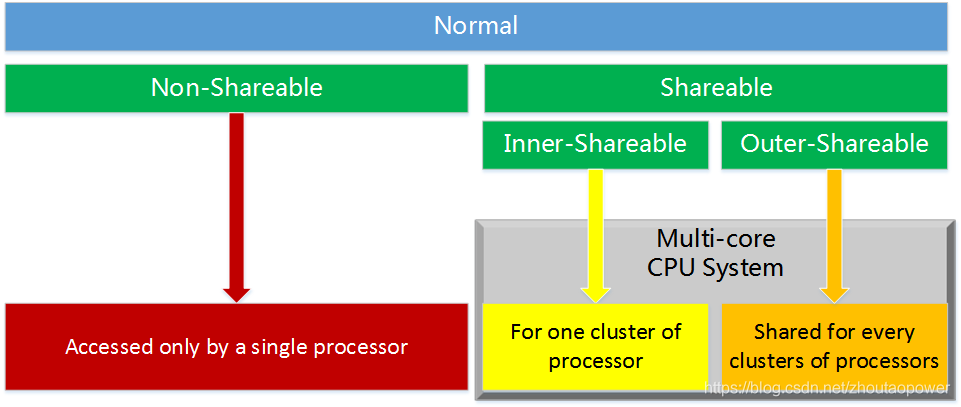

2.1.1、Normal memory with Shareability

Normal Type 是比较常见的存储器模型,它可以支持读/写或只读,它可以被配置成为 Shareable 或者 Non-Shareable;

在访问 Normal 存储器的时候(比如 DDR),一定要小心内存一致性的问题,因为系统中,常常会开启 cache,并在多核系统中,存在多 CPU 核心访问内存,内存屏障能够起到访问的保序作用,原子操作指令,可以起到访问互斥(LDREX/STREX);

对于 Normal Type 的内存属性描述如下:

- 当被配置成为 Non-Shareable 的时候,意味着在多核系统中,它只能被一个核访问;

- 当配置为 Inner-Shareable 的时候,意味着只能够被单个 CPU cluster 集群访问;

- 当配置为 Outer-Shareable 的时候,意味着只能够被多个 CPU clusters 集群访问;

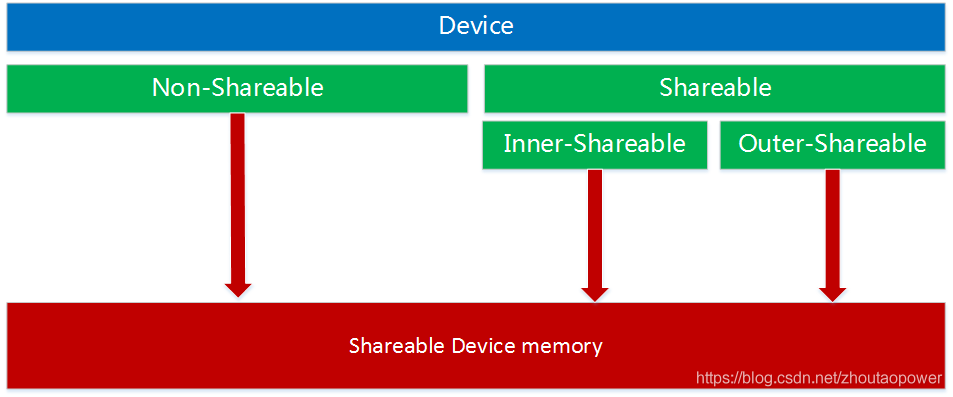

2.1.2、Device memory with Shareability

Device 类型存储器地址空间,可以配置为 Shareable(比如多核 CPU 中,UART 外设地址空间是对所有 CPU 共享的);当然,也可以配置为 Non-Shareable;

但是具体实际的设计实现中,不管是配置为 Non-Shareable,还是 Inner-Shareable,还是 Outer-Shareable,都一概视为 Outer-Shareable(毕竟是外设);

2.2、Cacheability Attributes

2.2.1、Normal memory with cacheable

Normal 类型的存储器(比如 DDR)除了有 Shareable 的属性以外,还可以携带 cacheable 的属性:

- Write-Through Cacheable:写透型 Cache 属性;

- Write-Back Cacheable:回写型 Cache 属性;

- Non-cacheable:不带 Cache 属性;

Non-Cacheable 很好理解,就是不带 Cache,直接与存储器交互,这样不会带来内存一致性问题,但是效率不高;

其余两种都是带 Cache 的访问,不过 Cache 的策略略有区别;写透也可以在一定程度上保证内存一致性问题,但要发起内存访问时序,降低性能;回写只是将数据写到了 Cache 中,并通过 Dirty 标记等方式来记录数据的有效性,从而避免直接的内存访问,可以提高性能;

2.2.2、Device memory with cacheable

Device 和 Strongly-ordered 类型的存储器(可以理解为外设)区域,都是 Non-cacheable 的,即,不缓存的;这个很好理解,写过驱动的朋友应该都能够知道,对外设的访问和对普通内存的访问是完全不一样的两个概念;

所以,最后总结起来就是:

3、Device VS Strongly-ordered

ARMv7-A 中,Device 类型的存储器和 Strongly-ordered 类型存储器,都是不可 Cacheable 的,并且他们的访问是不可被优化的,他们的唯一区别是在 Shareability 属性:

- 1、对 Strongly-ordered 存储器的写入,只有在写访问到外设或者存储器组件的时候,才算完成;

- 2、对 Device 存储器的写入,允许在写访问到达外设之前就完成;

上面这个说法是官方的意思,我理解一下,应该是 Strongly-ordered 不惜牺牲性能,去做保序的要求,一定要实际访问到外设,而 Device 类型的访问指令,可能还在路上(流水线中);

而且,Strongly-ordered 和 Device 类型要求,对他们的访问必须是对齐访问;

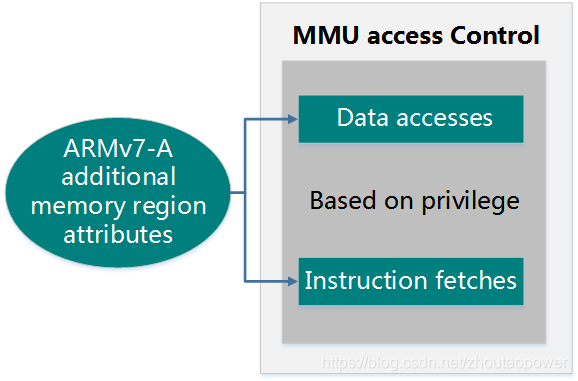

4、Access rights

存储器模型除了有各种属性以外,还需要支持访问权限(这个是必须的,否则访问非法空间,那还得了);

ARMv7-A 定义了扩展的存储器区域访问属性,也就是这个权限访问;访问权限分为两部分:

- 1、基于特权等级的限制数据的访问;

- 2、基于特权等级的指令访问;

PL0 的时候,也就是 User 模式,相当于非特权等级下,禁止访问结构体系下的某些特性,它不能更改许多配置设置。 在PL0上执行的软件只允许非特权内存访问;

当在 PL1 上执行的软件(通常操作系统都执行在 PL1 特权模式下)可以访问体系结构的所有特性,并且可以更改这些特性的配置设置;

值得注意的是,权限的配置以及更改,只能够在 PL1 模式下进行;

4.1、Privilege level access controls for data accesses

针对数据的访问来说,在 PL1 模式下,可以定义某存储器区域的访问权限为:

- 1、不可访问;

- 2、只有 PL1 特权才能访问;

- 3、特权和非特权模式都可以访问;

如果处理器尝试访问权限不允许的数据访问,则会生成数据中止异常(Data Abort)。 例如,如果处理器位于 PL0,并且试图访问被标记为仅特权模式可访问的内存区域,则会生成数据中止异常 Data Abort;

4.2、Privilege level access controls for instruction accesses

针对指令的执行来说,PL1 模式下,以定义某存储器区域的执行权限为:

- 1、不允许执行;

- 2、在处理器实现了 Large Physical Address Extension 情况下,PL1 不允许执行;

- 3、只能在 PL1 执行;

- 4、特权和非特权模式都可以执行;

访问权限的配置,在 CP15 的 MMU 相关的寄存器,他们的层次结构为: