ARMv7-A 处理器窥探 —— CP15 协处理器

1、ARMv7-A 协处理器

ARMv7-A 处理器除了标准的 R0~R15,CPSR,SPSR 以外,由于引入了 MMU、TLB、Cache 等内容,ARMv7-A 使用协处理器来对这些扩展来进行管理,ARMv7-A 支持 16 个协处理器,编号从 CP0~CP15,其中的 CP15 协处理器称之为系统控制协处理器,CP15 协处理器下的寄存器包含了 MMU、TLB、Cache等关键组件,其余的 CP0~CP14 有的控制Debug功能,有的控制 SIMD,有的控制浮点,咱们暂时只关注关键的 CP15;

2、CP15 协处理器

2.1、组成

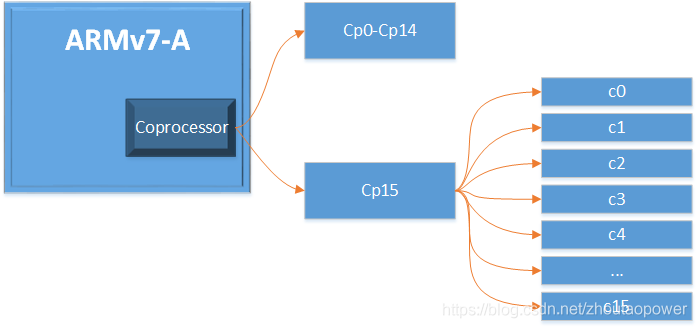

CP15 协处理器由16个子寄存器组成,分别为 c0~c15,所以 CP15 的层次关系为:

这里的 c0~c15 不是寄存器的含义,而是主(Primary Register)寄存器的意思,也就是每个主寄存器,都是一个寄存器组。

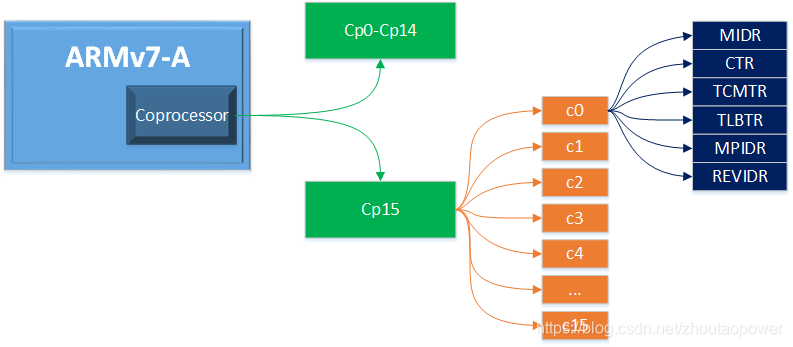

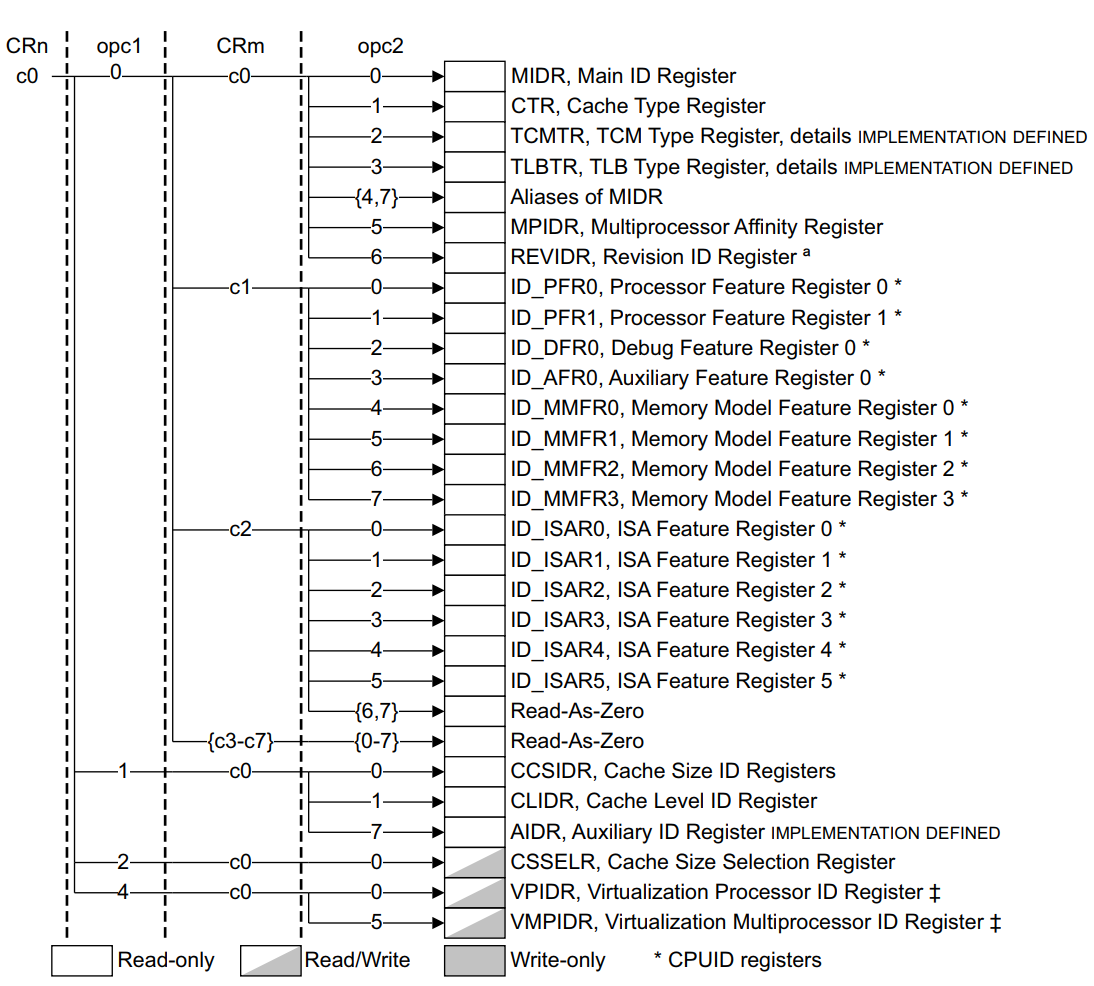

所以,针对 CP15 协处理器相关的层次结构总结下来为(这里以c0为例,c1~c15同样有很多寄存器,每个寄存器都是 32bits 的):

2.2、Cp15 协处理器寄存器组成

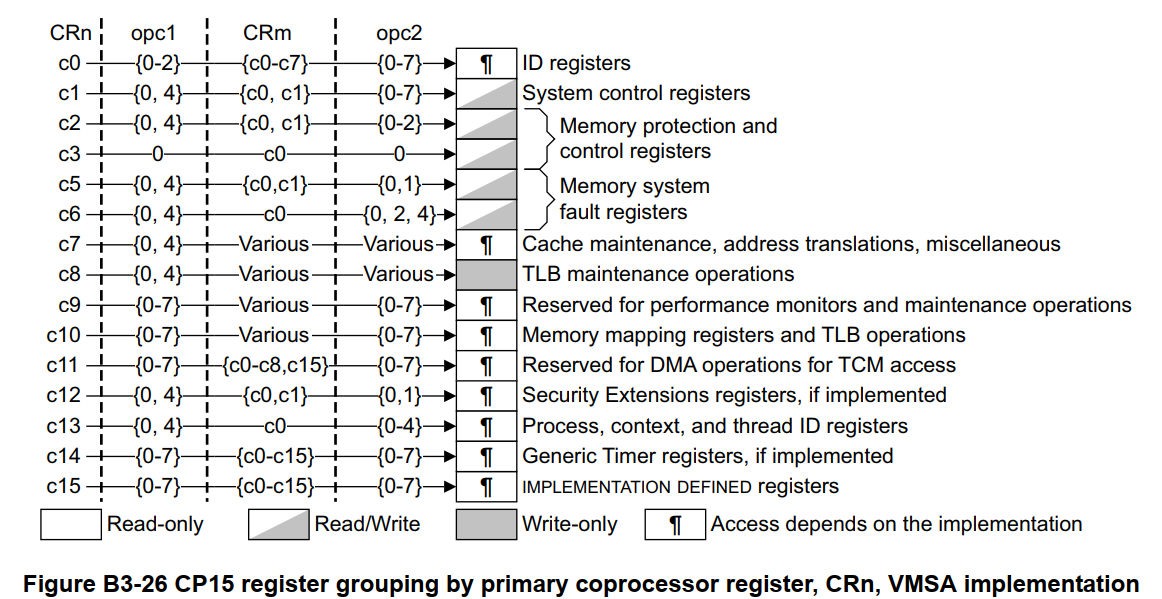

Cp15 协处理器的所有寄存器访问,都要依赖这几个值的组合达到访问的目的,前面说过整个 Cp15 的寄存器,分为 c0~c15,一共 16 个 Primary Regiser,再在每个 Primary Regiser 下面,又细分了很多具体的每个长度为 32bits 的寄存器,他们的整体组织结构为:

可以看到,Cp15 协处理器的 CRn 编号从 c0~c15,每个 Primary Regiser 都标记得有访问权限;后面的 opc1、CRm、opc2 的取值访问也都标记得清清楚楚;

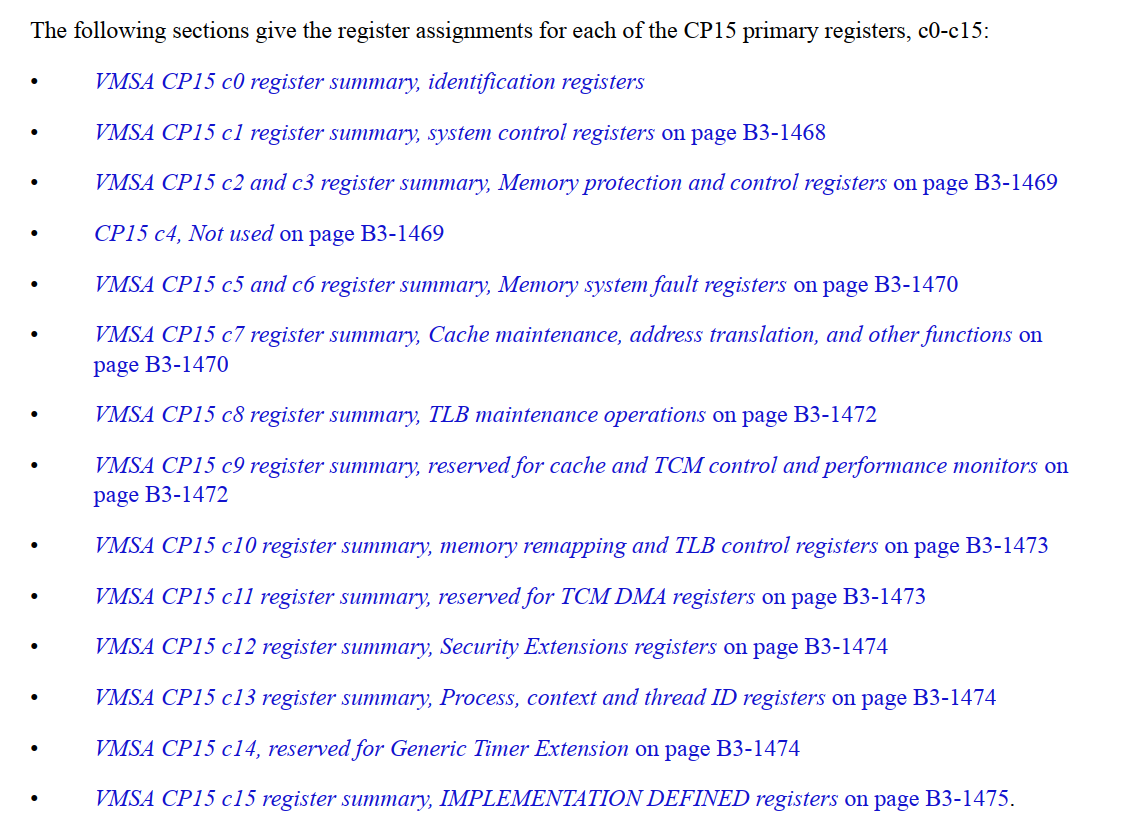

每个主寄存器的功能,下图链接都有详细的介绍

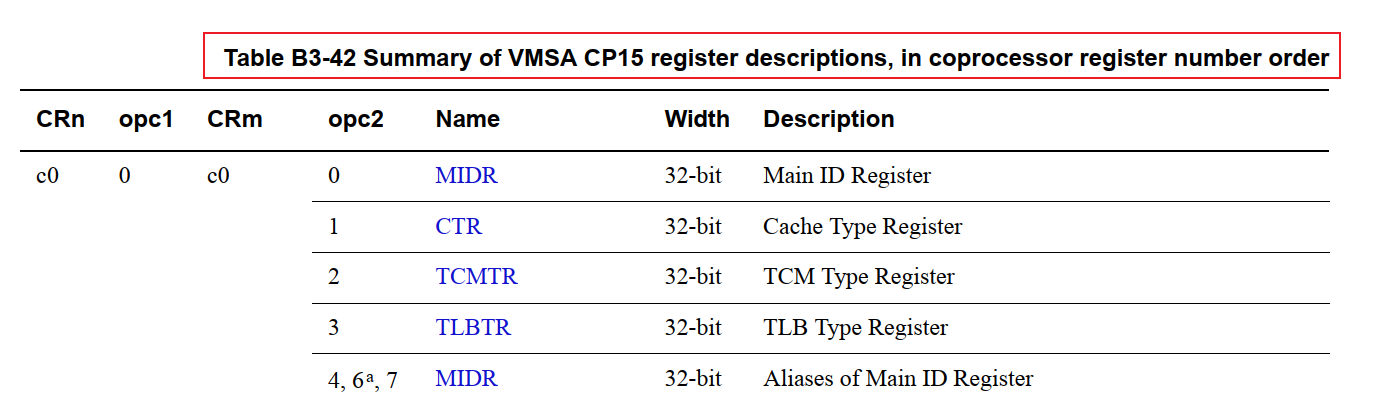

对于主寄存器c0,做下详细介绍

c0下的所有寄存器如下图

对于每个寄存器的介绍,可点下下图的蓝色字体

2.3、访问指令

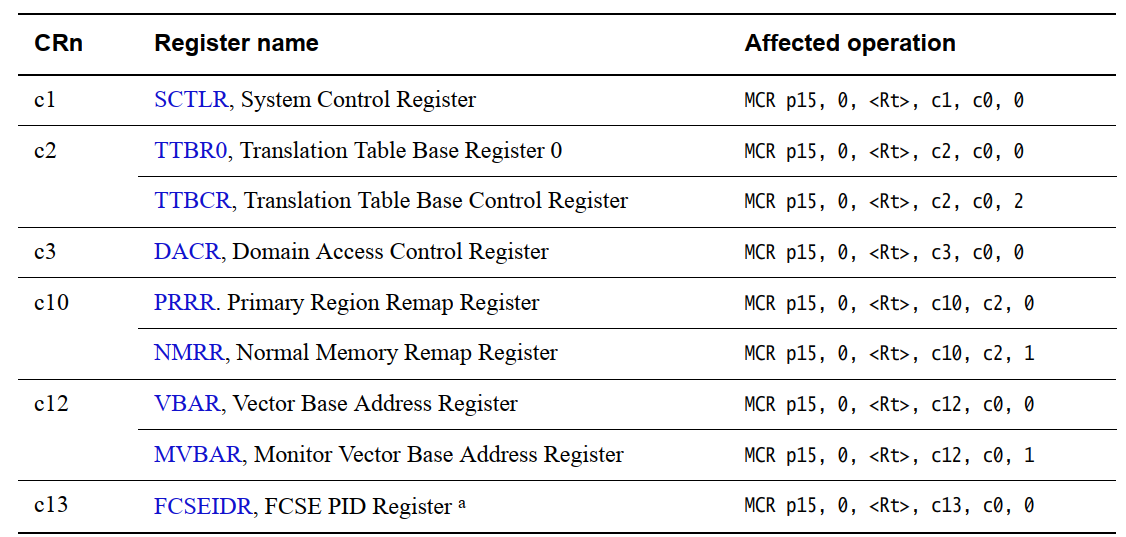

与 CPSR 类似,协处理器的访问是通过指定的汇编指令进行访问;常用的有 MCR/MRC 两条:

MRC: 将 CP15 协处理器中的寄存器数据读到 ARM 寄存器中。

MCR: 将 ARM 寄存器的数据写入到 CP15 协处理器寄存器中。

使用这两条指令,外加一些标准的指令,就可以实现读改写;

2.3.1、MCR

MCR 指令的格式如下:

MCR<c> <coproc>, <opc1>, <Rt>, <CRn>, <CRm>{, <opc2>}

其中:

- coproc:访问协处理器的名字,取值范围从 p0~p15;

- opc1:协处理器要执行的操作码,取值范围从 0~7;

- Rt:ARM 的寄存器(比如 R0),要写入到指定协处理器寄存器的数据就保存在此寄存器中;

- CRn:指定协处理器的目标寄存器;

- CRm:协处理器中附加的目标寄存器或者源操作数寄存器,如果不需要附加信息就将 CRm 设置为 C0,否则结果不可预测;

- opc2:可选的协处理器特定操作码,取值范围从 0~7,当不需要的时候要设置为 0;

2.3.2、MRC

MRC 指令的格式如下:

MRC<c> <coproc>, <opc1>, <Rt>, <CRn>, <CRm>{, <opc2>}

其中:

- coproc:访问协处理器的名字,取值范围从 p0~p15;

- opc1:协处理器要执行的操作码,取值范围从 0~7;

- Rt:ARM 的寄存器(比如 R0),将指定协处理器寄存器的数据读在此 ARM Core 寄存器中;

- CRn:指定协处理器的目标寄存器;

- CRm:协处理器中附加的目标寄存器或者源操作数寄存器,如果不需要附加信息就将 CRm 设置为 C0,否则结果不可预测;

- opc2:可选的协处理器特定操作码,取值范围从 0~7,当不需要的时候要设置为 0;

2.3.3、指令使用举例

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 上周热点回顾(3.3-3.9)

· AI 智能体引爆开源社区「GitHub 热点速览」