override 作用

override指示符

通常在执行 make 时,如果通过命令行定义了一个变量,那么它将替代在 Makefile中出现的同名变量的定义。

就是说,对于一个在 Makefile 中使用常规方式(使用“=”、“:=”或者“define”)定义的变量,我们可以在执行 make 时通过命令行方式重新指定这个变量的值,命令行指定的值将替代出现在 Makefile 中此变量的值。

如果不希望命令行指定的变量值替代在 Makefile 中的变量定义,那么我们需要在 Makefile 中使用指示符“override”来对这个变量进行声明。

override作用

- 保护makefile中定义的变量的值;

- 提供一种在makefile中增加或者修改命令行参数的方式;

实际情况下,我们经常会有这种需求:通过命令行指定一些附加的参数选项,对于一些通用的参数选项在makefile中指定.

1 保护makefile中定义变量值示例

1.1 没有使用override的情况

make命令行指定的变量值将会覆盖makefile中定义的同名的变量值

SRCS := A.c B.c C.c all: @echo "SRCS: " $(SRCS)

1.2 使用override的情况

make命令行指定的变量值将不会覆盖makefile中定义的同名的变量值,所以override有保护makefile中变量值不被命令行参数修改的作用。

override SRCS := A.c B.c C.c all: @echo "SRCS: " $(SRCS)

2 修改makefile中定义变量值的示例

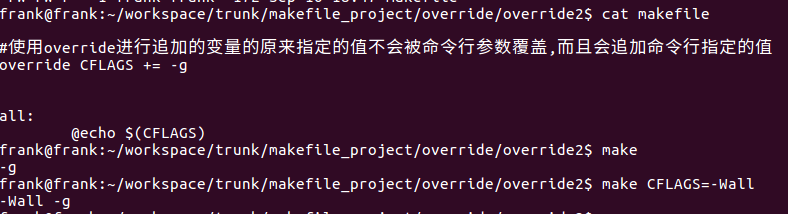

#使用override,对于进行追加的变量,原来指定的值不会被命令行参数覆盖,而且会追加命令行指定的值 override CFLAGS += -g all: @echo $(CFLAGS)

标签:

make/Makefile

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· 开发者必知的日志记录最佳实践

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· 写一个简单的SQL生成工具

· AI 智能体引爆开源社区「GitHub 热点速览」

· C#/.NET/.NET Core技术前沿周刊 | 第 29 期(2025年3.1-3.9)