高频下SPI总线的采样延时

概述

本文以 SPI Nor 为例,讲解在高频下SPI控制器的采样延时机制。

在MXIC的某款 SPI Nor 的规格书,在所有的读命令都有这么一句介绍:

The address is latched on rising edge of SCLK, and data of each bit shifts out on the falling edge of SCLK at a maximum frequency XXX

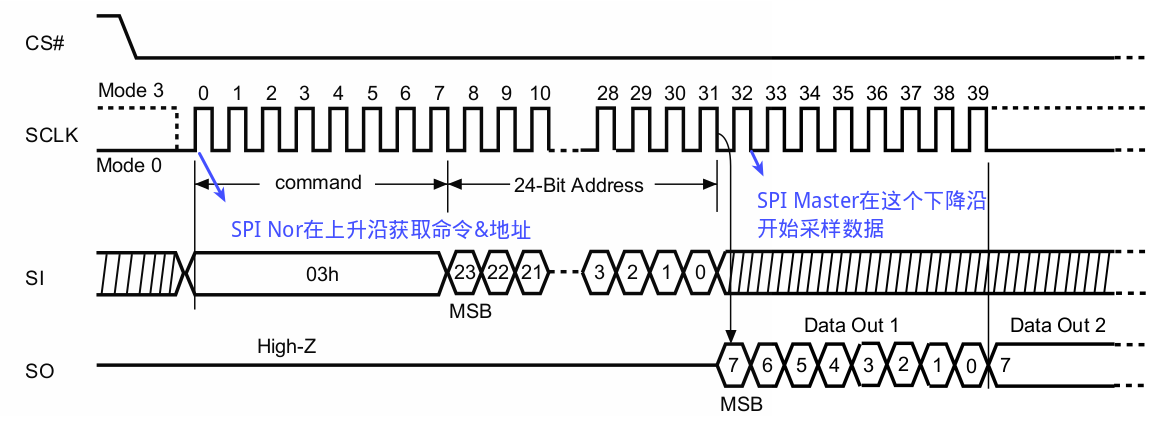

字面意思,就是说SPI Nor 在时钟的上升沿获取命令和地址,而 SPI Master 应该在时钟的下降沿采样 SPI Nor 返回的数据。

查阅大量的 SPI Nor 的规格书,普遍使用 SPI mode0 和 mode3 的模式下。不管是 SPI Mode 0 还是 Mode 3,都是从上升沿开始采样。不清楚 SPI 的4种工作模式的同学看这:《SPI总线传输的4种模式》。

SPI总线交互中,不管是哪个 SPI 模式,SPI Master 往往会在第一个上升沿采样点发送数据 ,在紧接着的下降沿用于接收数据。

我们看下一 Normal Read(0x3B) 命令的时序图:

在低频下,例如24MHz以下的频率,上面的采样点是非常稳定的,但是一旦跑到高频,例如 100MHz 的频率下,SPI Master 获取数据的时候必须额外加一个延时,否则会采样出错。

不同频率下采样延时不同,有时候是延时半个周期,有时候是延时一个周期。某款 SPI 控制器的规格书规定如下:

| 频率 | 延时周期 |

|---|---|

| <= 24MHz | 0 |

| <= 60MHz | 0.5 |

| > 60MHz | 1 |

为什么上升沿发送数据,下降沿接受数据呢?为什么不能做到上升沿发送和接受数据呢?为什么要有这个延时呢? 带着疑问,我们分析下实际输出过程。

实际传输过程

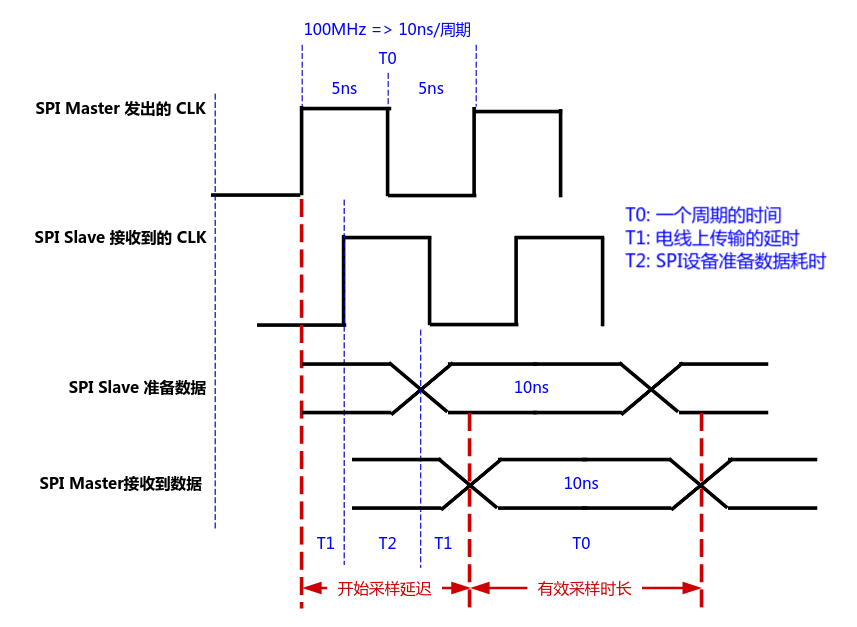

实际的 SPI 传输,我们必须考虑到 电路传输耗时 以及 设备准备数据耗时。

SPI Master 发起一个上升沿,SPI Slave并不是马上就能获取到上升沿,这期间会有延时,这就是数据传输的延时。同样的,SPI Nor 的数据并不是时刻准备着的,在 SPI Master 要读某笔数据时,SPI Nor需要时间准备数据。总的来说,实际的 SPI 传输过程,总会有延时。

用一张图来描述实际传输过程:

- 在某一时刻,SPI Master CLK 发出一个上升沿跳变

- 经过电路上的数据传输,过了 T1 时刻 SPI Slave 才收到上升沿跳变。因此,T1 就是电线上传输造成的延时。

- SPI Slave 准备数据用了 T2 时间

- SPI Slave 把数据传输回 SPI Master,同样要经过电路传输,因此会有 T1 的延时。

因此,从 SPI Master 发出第一个上升沿开始到能正确采样到数据,总的延时为: 2 * T1 + T2,也就是说,

SPI Master 在发送完地址后,必须过 2 * T1 + T2 时间才开始采样数据,才能获取到正确的数据。

这其实能说明为什么对 SPI Nor 设备,SPI Master 必须在上升沿发送命令和地址,在下降沿而不是上升沿获取数据,因为数据传输和数据准备需要一些时间。

在高频下,我们只是这样还不够。

高频下传输过程

假设 SPI Nor 运行在 100MHz 下,那么一个时钟周期就是 10ns,半个时钟周期就是 5 ns。

我们不妨计算下,在 100MHz 的频率下,SPI Master 采样数据的有效时间范围:

从 SPI Master 时钟的上升沿开始计算,计算上各种延时,那么 SPI Master 采样数据的有效时间范围应该是:

[ 2 * T1 + T2 , 2 * T1 + T2 + T0 ]

因为是 100MHz ,所以一个周期为10ns,即 T0 = 10ns。

以 XTX 的某一款 Nor 为例,查询规格书,在 AC Characteristics 的表格中,找到这么一行:

| Symbol | Parameter | Max | Unit |

|---|---|---|---|

| t CLQV | Clock Low To Output Valid | 6.5 | ns |

意思是说,从 时钟为低电平到有效数据输出的时间 为 6.5ns,换句话说,从接收到地址后,SPI Nor准备数据需要 6.5ns,即 T2 = 6.5ns。

根据有效采样时间 [ 2 * T1 + T2 , 2 * T1 + T2 + T0 ],可以计算出:

当电线传输损耗为1ns时,有效采样时间为(ns):[8.5, 18.5]

当电线传输损耗为2ns时,有效采样时间为(ns):[10.5, 20.5]

如果不加延时,SPI Master 依然是上升沿发送数据,下降沿采样数据,此时 SPI Master 采样数据的时刻是 5ns,完全不在上面计算的有效采样时间范围,自然无法采样到正确数据。

如果延时半个周期呢?采样时刻为:5ns + 5ns(半个周期) = 10ns,当电线损耗为 1ns 时勉强可用,当电线损耗为 2ns 时,就有无法正确采样的风险。

如果延时一个周期呢?采样时刻为:5ns + 10ns(一个周期) = 15ns,不管是电路损耗为 1ns 还是 2ns,都能使用,兼容性更强。

怪不得 SPI 控制器 建议 100MHz 频率下采样延时一个周期呢!

浙公网安备 33010602011771号

浙公网安备 33010602011771号