为什么计算机能读懂 1 和 0

2014-10-21 16:43 bbmarkcc 阅读(858) 评论(0) 收藏 举报from: http://www.zhihu.com/question/20112194#answer-8269873

关于计算机为什么能读懂0和1, @萧井陌 同学的答案中已经回答地相当仔细了,相信有钻研精神的朋友读完他的答案,就能在布尔代数原理和基本电路原理上对计算机的0和1有一个感性的认识。唯一有点美中不足的是他没有在物理层面上解释电路器件的运作方式,那么答主就来解释一下计算机的硬件核心:IC电路在物理层面是如何工作以及是如何制备出来的。

首先还是通过两个不同层面的基本介绍来总结一下 @萧井陌 同学的答案。

一、逻辑实现

IC数字电路中,用高电压(比如3.3V)代表1,低电压(比如0V)代表0。利用布尔代数的与、或、非基本逻辑,就可以构造出不同的电路,实现复杂的运算。

与逻辑:1与0=0、1与1=1、0与0=0

或逻辑:1或0=1、1或1=1、0或0=0

非逻辑:非1=0、非0=1

比如要实现一个1位的加法器(C=A+B):

1+0=1

1+1=0

0+0=0

因为是1位加法器,我们就不考虑进位了。那么逻辑的实现就是:

C=(A 与 非B)或(非A 与 B)

这样在逻辑上一个简单的加法器就实现了。复杂的IC数字计算电路,就是由几亿个这样的简单逻辑构成的。

在这一个层面的总结中,我们了解到,IC芯片的数学原理是布尔代数,这是芯片工作的逻辑基础。

二、电路实现

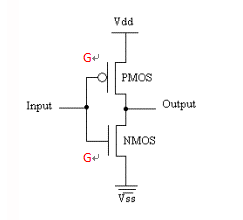

以上介绍的只是纯逻辑的实现,那么怎么在电路上把它实现出来呢?举个最简单的例子,非逻辑,我们用一个称为非门的电路来实现。

以上是一个非门的电路表示。如果Input为高电压(代表1),Output就是低电压(代表0),反之亦然。图中,Vdd表示高电压,Vss表示低电压(接地,即为0)。

PMOS可以看做一个用G端电压控制的开关器件:如果加在G端是高电压,那么PMOS可以看做是断线,如果加在G端的是低电压,那么PMOS可以看做是一根导线。NMOS正好相反,如果G端是低电压,则是断线,如果G端是高电压,则是导线。

那么看这个非门的电路,当Input为高电压时,PMOS断线,NMOS导通,Output相当于接地(Vss),那么Output就是低电压了;当Input为低电压时,PMOS导通,NMOS断线,Output相当于接Vdd,那么就是高电压。

这样我们就在电路层面实现了最基本的门逻辑-非门。与逻辑和或逻辑可以使用相似但稍复杂的电路来实现。IC数字电路归根结底都是靠这三种电路来实现的。

在这一个层面的总结中,我们了解到,其实计算机的工作原理并没有想象中那么“智能”,其实跟用水闸开关控制水流的冲力去推动风车转动的基本思想是一致的。计算机并不“懂得”0和1,它只是靠我们精妙的组织具有特定特性的物理器件,让器件发挥自身的物理性质,从而能在电压上反应出一个计算电路的输入和输出。

有了以上总结,我们就可以研究现代IC芯片的基本器件单元:MOS管了。

三、MOS管

从以上介绍中可以看出,数字电路中最重要的器件就是MOS管了,分为PMOS和NMOS。不同于电阻、电感、电容等基础电子器件,MOS管的导通与否是通过G端的电压来控制的,那么就不能使用最基本的电阻器等原件来实现了,需要重新设计一种器件。

以NMOS为例:

以上是一个NMOS的剖面图。黄色区域为掺杂了正离子的硅,绿色区域为掺杂了负离子的硅。上面的三块灰色区域为源(Source)、栅(Gate)、漏(Drain)的电极,分别对应了非门电路中NMOS连接Vss、Input(G)、Output的三个电极。从以上非门的介绍中可以了解到,我们使用NMOS,是希望通过控制Gate的电压,来控制从Source到Drain能否导通。

如图所示,现在红色虚线勾勒出的区域,从左到右形成了一个N-P-N的结构,表示掺杂了负离子的硅-掺杂了正离子的硅-掺杂了负离子的硅。因为正负离子的同性相斥、异性相吸的特征,在P、N的交界处,会形成一段“耗尽层”,其中是没有电子的(都被同性相斥、异性相吸到其他区域去了),那么如果Gate上不加电压的话(电压为0),从Source是Drain是不能导通的,对应了以上电路分析时的断线情况。如果Gate上加上合适的电压,那么情况就不一样了,因为电压为正,那么会吸引下方红色虚线勾勒区域内的负离子到Gate的下方来(电容器原理),从而在Gate下方形成了一段有负离子(N-type)的区域,也就是说原来的掺杂了正离子的硅在Gate下方的一小段区域发生了翻转变成了掺杂了负离子的硅,这样就将Source和Drain连接了起来。因为Source和Drain本身也是连接着负离子区域,这段区域就相当于一条导线,那么从Source到Drain就导通了。这就是NMOS能通过Gate控制导通能力的原理。PMOS原理类似,只不过掺杂的离子极性和NMOS刚好是相反的。

由以上介绍我们知道,控制芯片电路中的“水闸”其实是一个运用电子的基本物理特性工作的人造器件。在现代电路中,这样的器件尺寸是非常小的,基本在100nm级别(也就是说人的头发丝的截面可以放得下几百个这样的MOS器件)。那么这么小的器件,人类是怎么制造出来的呢?

四、物理实现

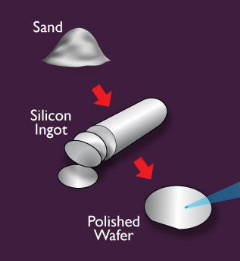

了解了MOS管的功能和它的结构后,就可以继续了解CMOS工艺了。CMOS工艺的目的就是在硅晶圆上通过多道工序,建造Source、Gate、Drain结构,实现NMOS和PMOS管,从而构造出与或非门,构建出更复杂的逻辑。硅晶圆其实就是从沙子中提取出来的硅单质,我们把它制作成薄片,在表面同时制备成千上万个MOS器件,形成IC芯片。

首先介绍一下一些基本工艺的目的和原理:

1、 生长SiO2:将硅晶圆放入通了氧气的烘烤炉中,使Si氧化,在表面生成一层SiO2。一般是为了绝缘。

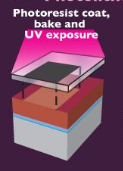

2、 光刻(湿法):因为半导体器件的尺寸非常小,不可能通过机械手段加工,所以只能通过刻蚀的方法。原理是先在要刻蚀的表面均匀涂抹一层光刻胶并烘干,然后通过掩膜板(上面绘制了需要刻蚀出的图像,需要刻蚀的部分为透明的,不需要刻蚀的部分用黑色阻挡),将紫外线照射到光刻胶上。光刻胶分为正胶和反胶,如果是正胶的话,照射到紫外线的部分就溶解掉了。这样,需要刻蚀的部分上覆盖的光刻胶就被紫外线透过掩膜照射溶解了,而不需要刻蚀的部分因为紫外线不能透过掩膜的黑色部分,所以仍在器件表面。这时将器件放到能溶解其表面物质的溶液中,被光刻胶覆盖的部分因为接触不到溶液,所以不会被去除,而没有光刻胶的部分就溶解掉了,于是就在器件表面形成了需要刻蚀出的图形。

3、 离子刻蚀:前序步骤和湿法光刻是一样的,都是用光刻胶形成图形。但是不同于用溶液溶解,离子刻蚀是使用高能离子打向器件表面,没有被光刻胶保护的部分就被打掉了,被光刻胶保护的部分留了下来。

然后我们就可以了解一下MOS的具体制备流程了(以下图片来自FSI)。

1、 STI浅沟槽隔离:STI的目的是为了在IC电路中,将各器件隔离开来,否则会有漏电等情况发生。STI使用SiO2作为隔离介质,因为SiO2有良好的绝缘性。

首先将切下来的硅晶圆做清洁。

在Si表面生长一层很薄的SiO2,然后在上面覆盖一层Si3N4。这里Si3N4起到一个占位的作用。

涂抹光刻胶并烘烤,用紫外线透过掩膜进行光刻。

没有被掩膜黑色区域保护的光刻胶部分就被去掉了,留下了被保护的部分。

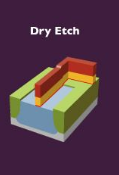

干法刻蚀,就是离子刻蚀,没有光刻胶保护的部分被高能离子打掉了,从而形成了凹槽。

去除残留的光刻胶并清洁硅晶圆。

在晶圆上沉积一层较厚的SiO2,因为是沉积得到的,表面很不光滑。

通过CMP(化学机械研磨),将不光滑的表面磨平。

这时用能溶解Si3N4的溶液将Si3N4去除。之前提到,Si3N4是占位的作用,它去除后,SiO2的高度就略高于晶圆表面了,这也是为了起到更好的保护隔离作用。

2、 生长阱。阱就是之前介绍MOS管时的黄色区域,作用之前也提到过了,是为了形成N-P(阱)-N或者P-N(阱)-P这样的结构。

首先还是光刻,用掩膜留下跟需要刻蚀图形相同的部分光刻胶。

进行离子注入。假设我们是要制作NMOS,那么就注入正离子(形成P阱)。注意没有被光刻胶保护的部分会注入,而被光刻胶保护的部分就不会注入到了。

去除光刻胶并清洁表面。

退火,主要目的是为了让离子在硅晶圆中更好地扩散,形成合适尺寸的阱。

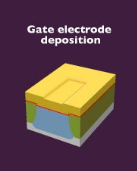

3、 制作栅(Gate)。Gate就是控制Source和Drain是否导通的部分,一般材质是多晶硅,现在有时也用其他材质了。

先对晶圆做一下清洁。

在晶圆上覆盖一层多晶硅。注意,要覆盖只能是晶圆表面全部覆盖,因为尺寸太小在这一步不能可能控制它的覆盖部分,只能在后续工艺中用光刻去除不需要覆盖的部分。

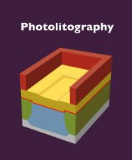

还是涂抹光刻胶,用紫外线透过掩膜照射,留下一部分。

湿法刻蚀,把没有被光刻胶保护的多晶硅去除。

去除光刻胶并清洁。这样就留下了我们需要的多晶硅部分了。不过这一部分形成的多晶硅层还不是Gate用的多晶硅,这个叫做牺牲层,主要是为了形成真正的Gate垫背用的。原因是由于Gate的尺寸很小,目前刻蚀工艺无法形成特别精确的矩形图形,所以使用了两步工序,这一步形成的多晶硅还会在以后被刻蚀掉,具体原理不再赘述。

再次覆盖一层多晶硅。

覆盖一层电极物质,一般是金属(比如Al)。

涂抹光刻胶并刻蚀光刻胶。

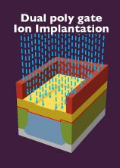

栅离子注入。没有被光刻胶保护的多晶硅部分就被注入了离子了,这是为了增强Gate的导电性。

去除光刻胶并清洁。

继续涂抹光刻胶并刻蚀光刻胶。注意这一步形成的图形就是栅真正的结构了。

干法刻蚀。没有被光刻胶保护的金属(黄色部分)和多晶硅(表面红色部分)就被高能离子轰击掉了,留下了我们需要的栅结构。

去除光刻胶并清洁。

在栅上覆盖一层氧化层(紫色部分),这是为了在下一步离子注入时保护栅。到这一步,栅(Gate)就制作完成了。

4、 在阱上制作Source和Drain的高掺杂部分。由MOS结构图可知,Source和Drain之间有一个N-P-N(或P-N-P结构)。之前在制作阱的时候,我们把中间的这个部分(也就是阱)制作完成了,现在就是制作两边的部分。

首先还是光刻,留下部分光刻胶。

离子注入,被光刻胶和栅保护的部分是注入不到离子的,而中间两块区域就被注入了和阱的极性相反的离子了,于是就形成了N-P-N或P-N-P的结构。

去除光刻胶和保护层并清洁。

5、 形成栅两旁的保护层。这是为了防止栅和源、漏之间由于量子隧穿效应形成漏电流。用SiO2保护就可以了。

沉积一层SiO2和Si3N4。

直接用高能离子轰击表面,控制轰击的时间,从而就把大部分SiO2保护层去掉了,留下了栅两边的比较厚的部分。

清洁表面。从以上步骤我们也可以看出,之所以MOS工艺中要用一步步复杂的光刻、刻蚀、沉积,主要原因就是因为器件太小了,没办法直接进行机械加工操作,只能通过化学或离子轰击的方法来制作,但是这些方法又只能针对一个表面,所以需要用光刻胶和掩膜板来一次次地制作保护区域,形成我们要制备的图形。

6、制作Source和Drain的低掺杂部分。之所以在制作Source和Drain时要分为高掺杂和低掺杂两块区域,是为了导通时有更好的导电性(高掺杂),同时避免连接电极时的附生电容效应(低掺杂)。

首先还是上光刻胶并刻蚀出图像。

低掺杂的离子注入,形成了两边的亮蓝色区域。

去除光刻胶并清除。

退火,使掺杂离子稍扩散。这样高掺杂和低掺杂区域共同构成了源和漏。

7、 金属硅化物的制备。主要是用来连接Gate和电极的,导电性介于金属和多晶硅之间。

首先是清洁表面。

在表面覆盖一层金属硅化物。

退火。

通过刻蚀等方法将不需要的金属硅化物部分去除,留下连接栅的那部分。

再次退火。到这一步金属硅化物(栅到电极的连接部分)就制作完成了。栅的形状是L形,之后会在L的尾部连接金属电极。

8、制作接触电极。栅、源、漏的硅部分已经制作完成了,现在要把它们用金属导线引出来,这样才能连接到电路中去。

首先覆盖一层SiO2和Si3N4。这是MOS管和上层导线的隔离层。

涂抹光刻胶,在光刻胶上形成几个穿孔。前面两个是用来连接源和漏的,后面那个是用来连接栅的。

干法刻蚀。用高能离子轰击晶圆表面,上一步形成的3个穿孔下方由于没有保护,SiO2隔离层就被击穿了,栅、源、漏就被暴露了出来。

去除光刻胶并清除表面。

在表面沉积一层金属,这样金属就填充了穿孔,从而连接了栅、源、漏,将它们引了出来。

CMP工艺,打磨掉表面多余的金属。

清洁表面。

9、制作金属层。这一层就完全根据电路设计中的引线来制作了,使用的金属材质和图形都是因设计而异的。

首先沉积一层介电层(就是绝缘层,用来隔离)。

光刻出跟需要制备的金属层图形相同的光刻胶层。

干法刻蚀,用高能离子轰击,刻蚀掉不需要的介电层。

去除光刻胶并清洁。

覆盖一层金属,这层金属填充到了介电层被刻蚀出的凹槽中,连接到了下方的金属电极。

CMP工序,去除掉表面多余的金属。

清洁表面。

然后就是根据电路结构继续制作金属互联层,一层层地连接到外部电路中去。一般一个简单的芯片需要10-20层互联结构。最后就是将芯片打上与外部电路连接的电极,一块完整制作好的晶圆就产生了。一般一块晶圆上会有几十块芯片,把芯片切下来就可以测试、封装、使用了。

如此,一块芯片就制作完成了。计算机通过以高低电压形式表示的1、0状态作为输入,在芯片上的千千万万个MOS管的计算下,得到同样是以电压形式表示的输出,然后通过以电压驱动的输出设备(比如显示器)显示给用户。整个过程其实是利用了电子的物理特性和极其精妙的器件组合,获得了一个“自动化”的处理方式。

浙公网安备 33010602011771号

浙公网安备 33010602011771号