EZ-USB™ FX3 USB调试记录

官方文档下载链接:EZ-USB™ FX3 USB 5 Gbps外设控制器 - Infineon Technologies

芯片型号 :

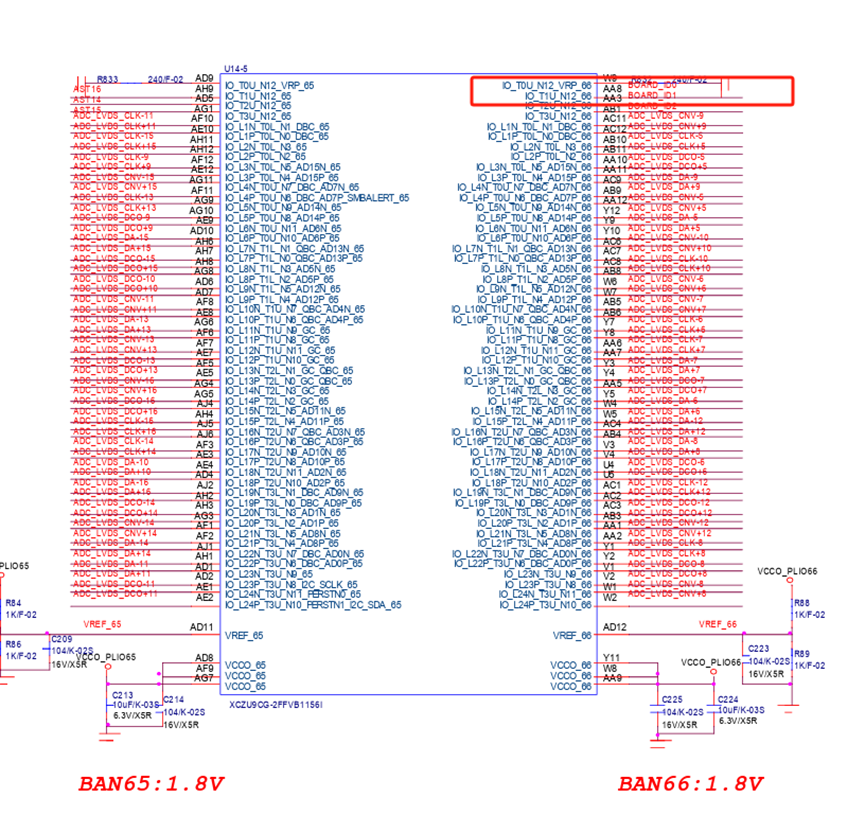

Product family : Zyng UltraScale+MPSoCs

Project part : xczu9cg-ffvb1156-2-i

调试阶段-1

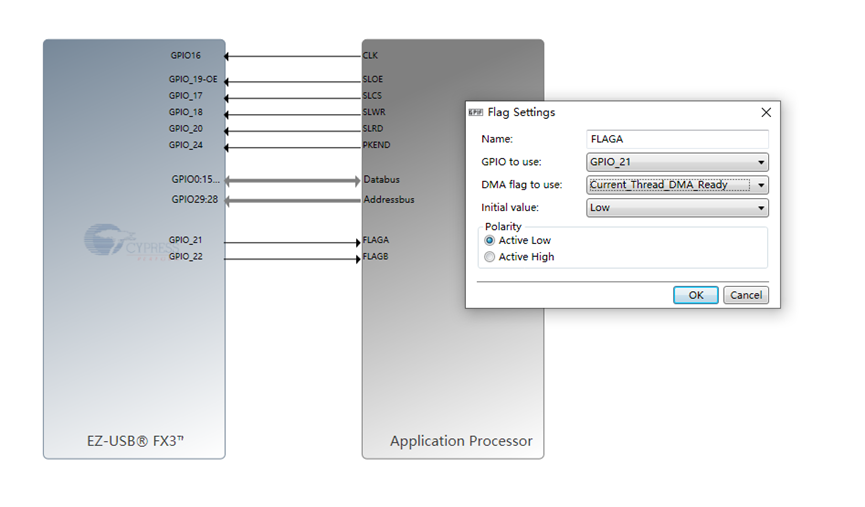

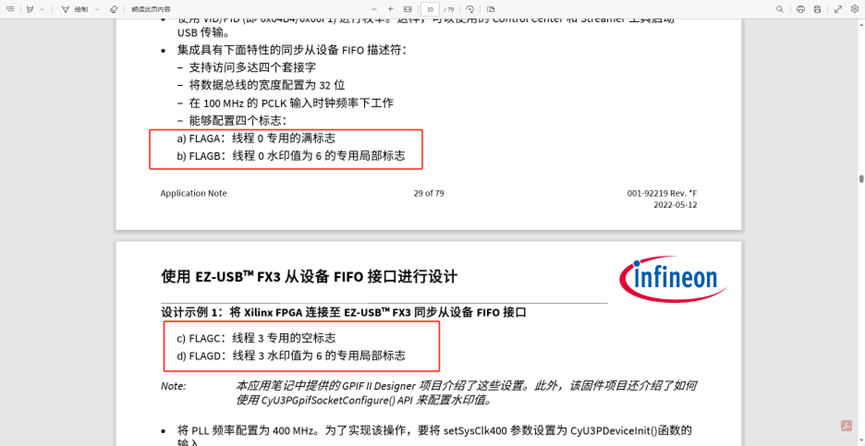

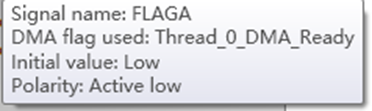

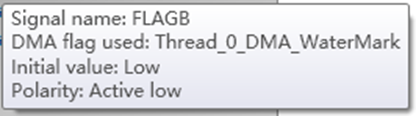

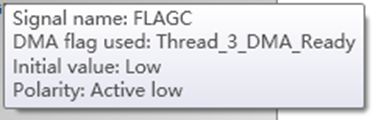

约束中,硬件上部分功能引脚未连接。在USBFIFO芯片datasheet中未标出flagc与flagd,只有在示例程序中才有体现两个标志位,故硬件设计上有所遗漏。

调试阶段-2

根据datasheet设计硬件时未引出flagc与flagd,软件尝试修改固件功能,只使用flaga与flagb标志位,但修改固件功能的同时,FPGA例程也必须修改,工作量较大。

调试阶段-3

为先确认开发板与FPGA连接的硬件原理与PCB走线正常,使用飞线连接两个flag信号,保障能够直接使用现有固件与FPGA例程测试硬件通路。

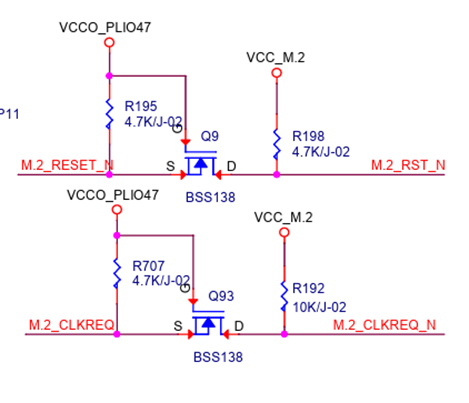

在第一次飞线时,飞线连接到了3.3V电源域的IO引脚,开发板对FPGA板连接为1.8V的电源域,故导致电平逻辑不正确,例程无法正常工作。

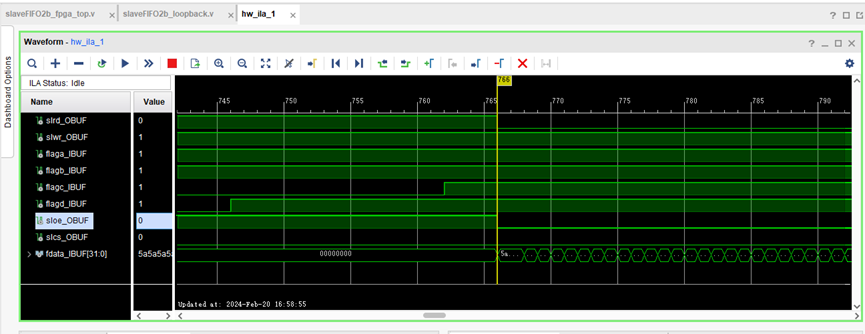

第二次飞线时,在3.3V电源域基础上添加MOS管作电平转换,将开发板输入的3.3V flag信号转换为1.8V,但由于高速传输下,由于MOS管的寄生电容产生了高容抗,flag信号延迟过大。FPGA使用在线debug观察flag时序明显与datasheet不符。

第三次飞线直接将flag信号连接到1.8V电源域的IO口。

调试阶段-4

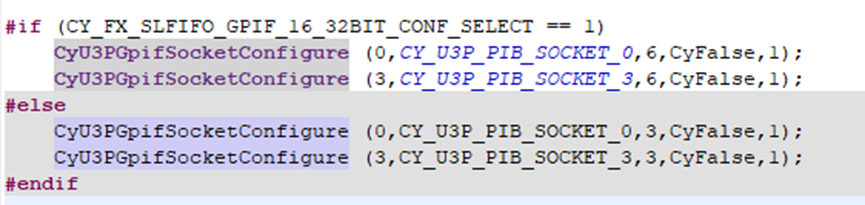

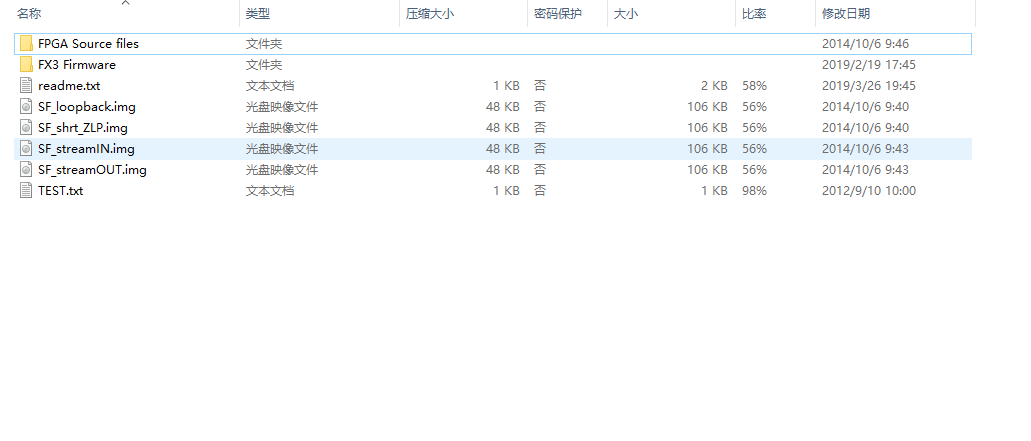

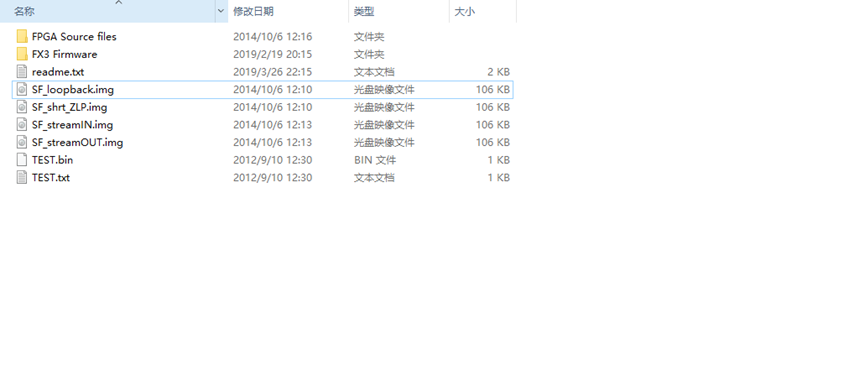

现需要向USBFIFO载入固件,根据例程设计文档配置如下。

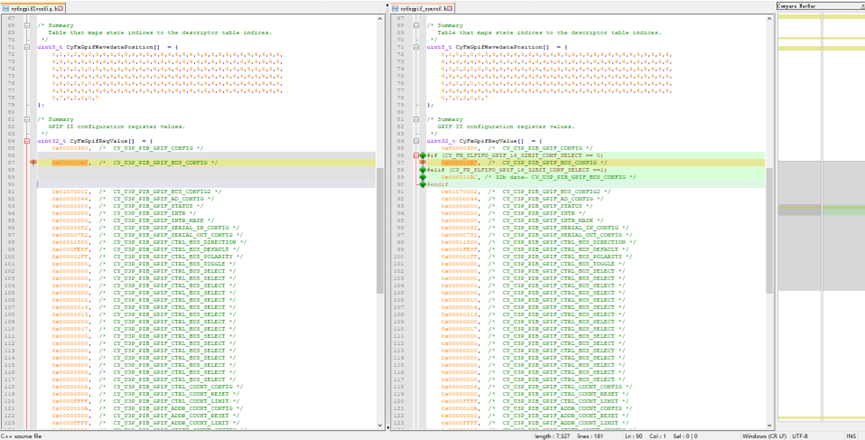

产生的.h文件与SDK安装后自带的固件包中的.h进行比对,代码无任何差异。

将使用该.h文件编译过的固件烧录到USB开发板中。

从PC端向固件中发送数据,flagc作为读空信号一直未被使能,未知问题。

后续从文档《AN65974》压缩包中获取的固件代码解决了此问题。

调试阶段-5

调试阶段-4中编译的固件无法正常使用,故使用例程文档中自带的固件- SF_loopback.img,可在PC端读写数据,但接收数据与发送数据不符。

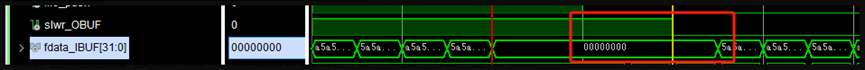

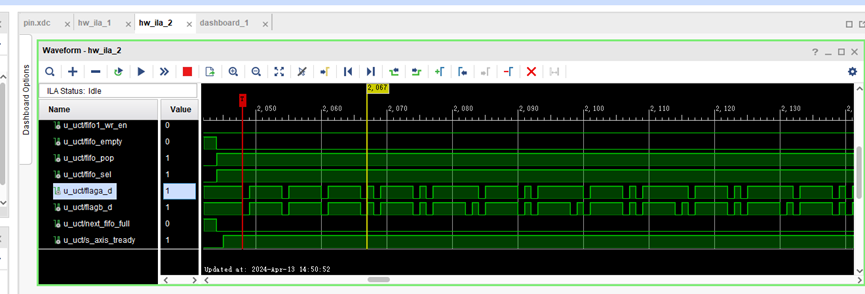

根据ila探针已定位可能由于到slwr提早拉低,推测data线还未完成翻转就被送入USBFIFO。

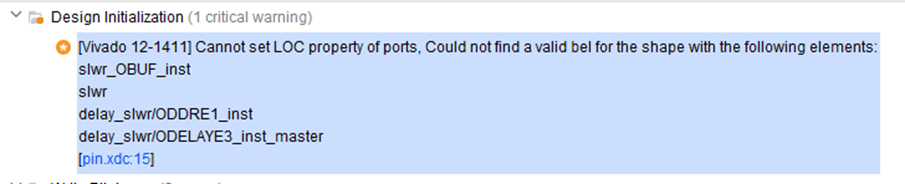

尝试直接使用原语增加延迟链路,由于原语链路与实际物理设计不符导致route失败

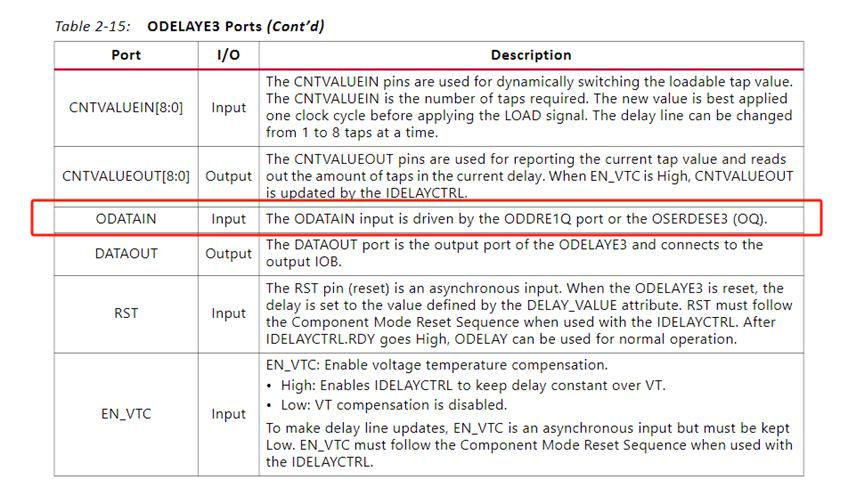

根据《ug571》,需要在delay前加入ODDRE1原语。

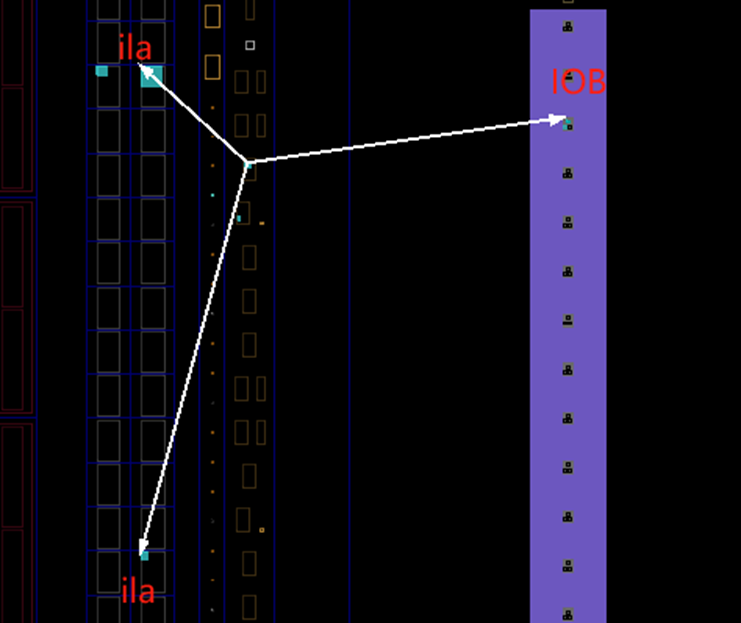

加入原语后route依然失败,观察device走线,经过delay_chain之后除了送入IOB,此外还送入了ila,这在物理上无走线设计,需删除ila连接部分。

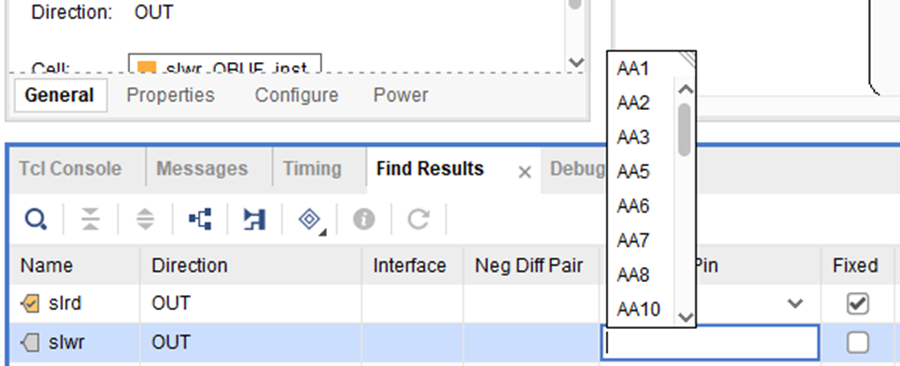

删除ila部分后,原语链路依然不正常。但其它部分IO可正常设置,判断依然是物理设计上欠缺链路硬件导致的。

调试阶段-6

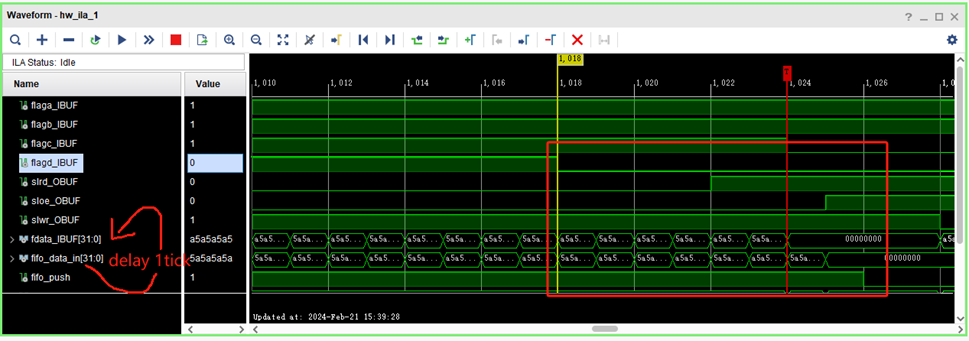

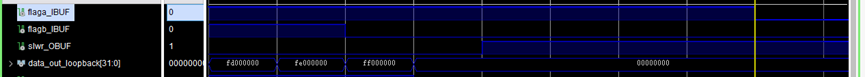

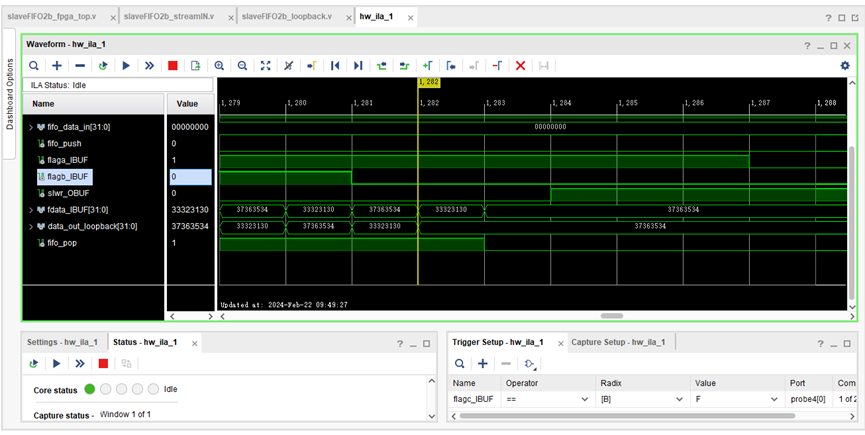

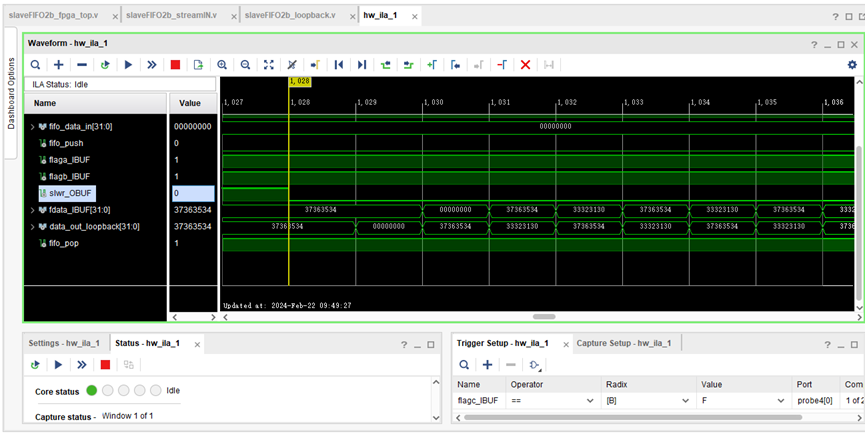

调试阶段-5似乎无法找到突破口,故选择重新观察时序图,发现在固件设置水印值为6的情况下,在flagd拉低之后,fifo还送入了7次数据。其中fifo_data_in是fdata_ibuf的延时一拍,fifo_push是fifo_write的enable。

观察发送数据末端,发现其与文档描述有些许出入。

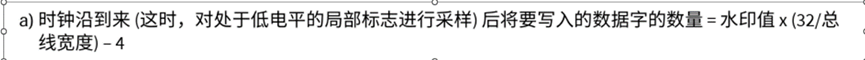

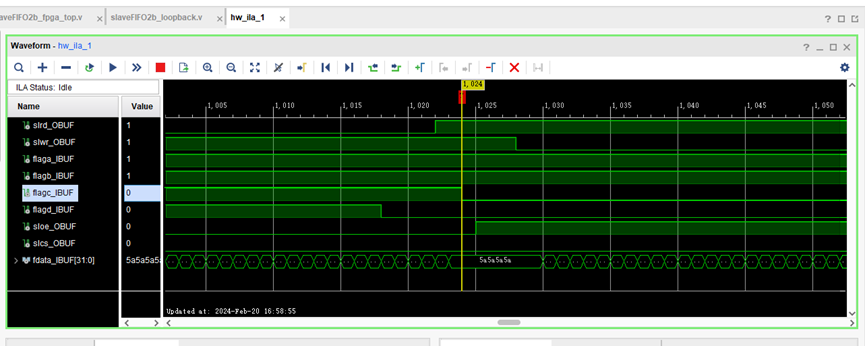

根据如上文档截图中的描述,此时水印值为6,当检测到flagb低电平时,可继续写入的数据量应该为6*(32/32)-4=2,即2次32bit。在下图中slwr在flagb拉低后却持续了3个周期的低电平,明显不符时序。

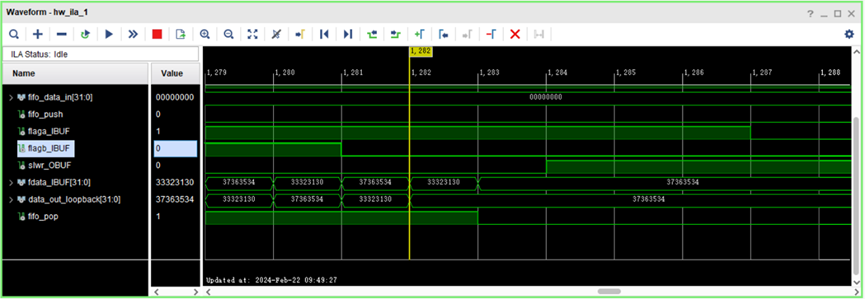

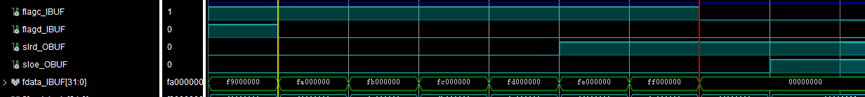

修改程序后时序符合规范。如下图

调试阶段-7

PC端发送1024字节,FPGA回传1024字节,使用MATLAB校验,发现产生错误。

调试阶段-8

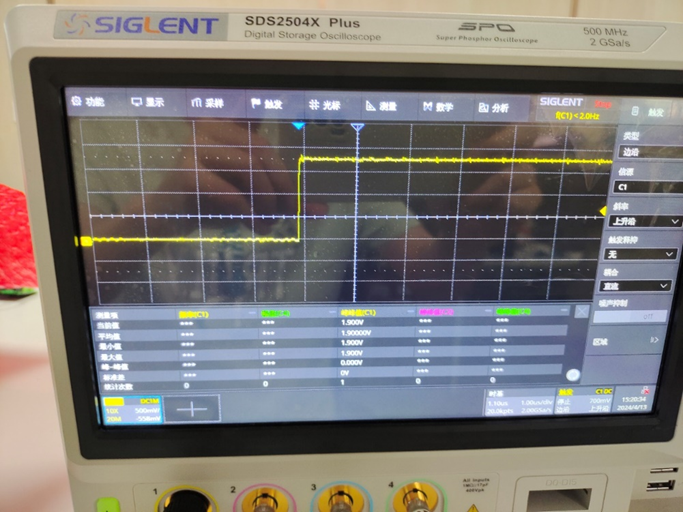

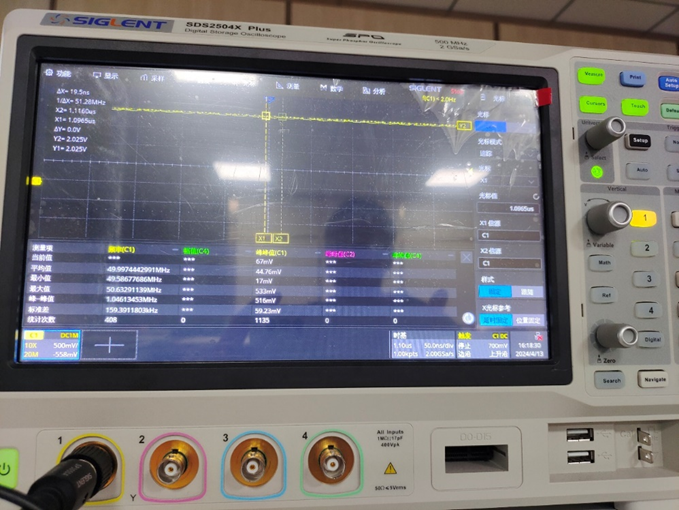

现起始发送阶段与停止发送阶段时序已均符合要求。观察到在发送数据还未全部填满USBFIFO分配的RAM区域时,flag存在拉高的现象如下图。由于从FPGA到FX3 USBFIFO间还存在插针引脚、FPC线,故不排除32位并行数据线产生强磁场的问题。

fpga检测到flagb拉高后开始发送数据,32bit数据线每经过1个时钟周期就会同时翻转一次,fpga上检测到flagb也在持续翻转,示波器接入USBFIFO端引脚,观察如图,示波器通道1接入的是flagb信号。

如果32bit的fdata一次只翻转1bit,明显flagb的信号质量就好多了,flagb如下图示波器。

如果在FPGA数字大板FPC座子电阻处测量如下图也存在问题。

当连同FPC线将USBFIFO拔出后再次在FPC座子端测量信号质量如下图所示,明显较上一张图改善许多

调试结果

由上数据可认为在FPC线传输链路上,32bit数据线的持续同时翻转产生的串扰影响了邻近的控制引脚。后续改板需将FX3 USBFIFO的芯片贴近FPGA附近,经过FX3 USBFIFO芯片后转换成USB3.0接口再离开FPGA数字板接入PC,此种方案较为稳定与安全。

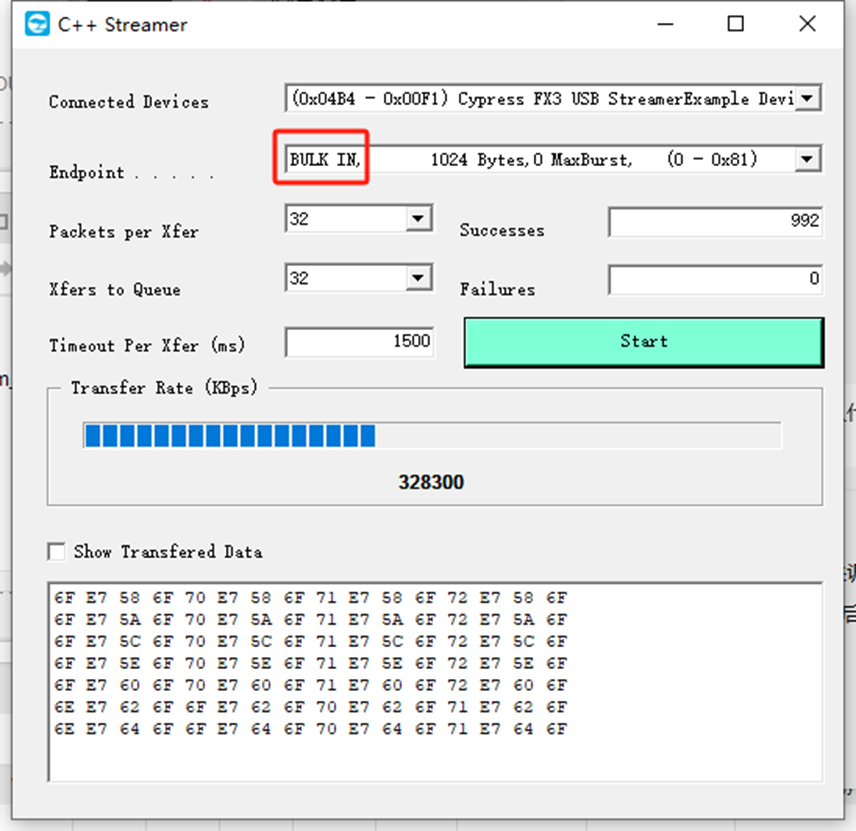

跑流实验

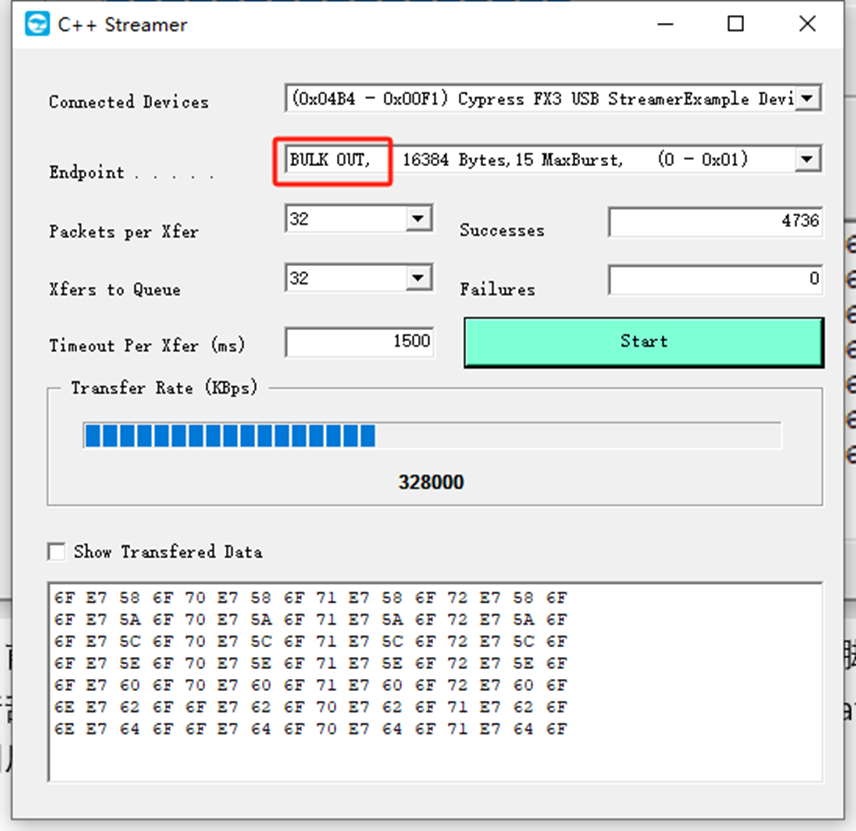

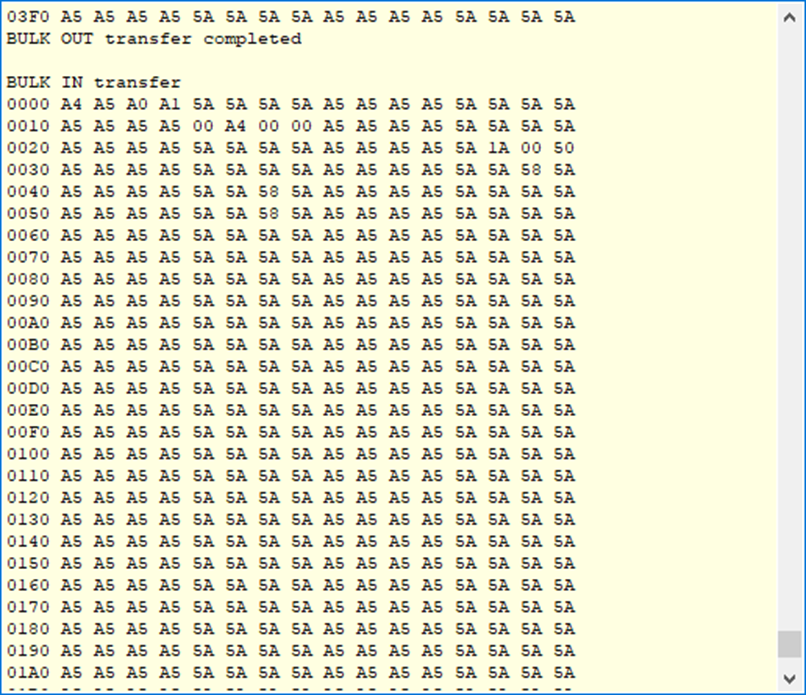

按照示例文档《AN6597》 page43中描述进行试验。注意,stream_in与stream_out的USBFIFO固件相同可通用,但FPGA端的选择模式需要变换。测试结果如下

1、 stream_in(FPGA→PC)

2、 stream_out(PC→FPGA)

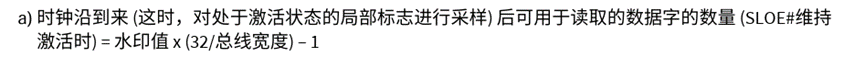

关于水印值Water mark的解读 :

1、作写入时

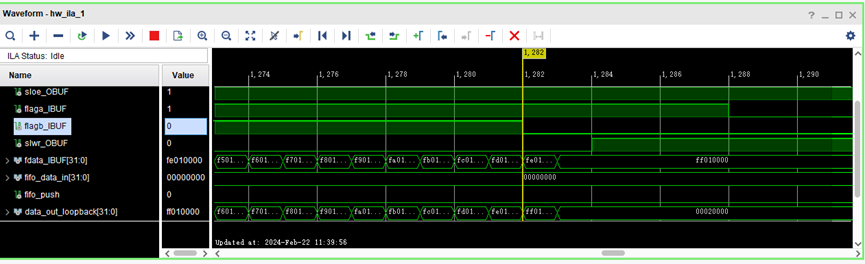

其中总线宽度是32bit,所以当水印值设置为6的时候,可写入的数据量为6x(32/32)-4 = 2次32bit的时候,水印标志(flagb)就被拉低了,再过2个周期slwr也应该被拉起。此时再经过4个周期full标志(flaga)被拉为高电平,与水印标志刚好相差6个周期。如下图。

2、作读取时

设置为6的时候,倒数第6个数据读出即时钟上升沿到来的同时(没有任何延时),它也将被拉低,此时剩余可读取的数据量为6x(32/32)-1 = 5次32bit。

从时序图来看,当读出水印标志位(flagd)为0的时候,与此同时读出的数据应该是倒数第6次的32bit数据,data线应该继续翻转5次,射出5次数据,当读到empty(flagc)为0时,data线上数据也已无效。如下图

其它问题记录

1、FPGA数据输出到data线上时需更换顺序以便在PC上观察

assign data_real[31:24] = data_cnt[7:0];

assign data_real[23:16] = data_cnt[15:8];

assign data_real[15:8] = data_cnt[23:16];

assign data_real[7:0] = data_cnt[31:24];

2、(无具体参考价值)32M频率下官方提供的原始RTL代码读写的时序图

3、此外由于fifo初上电需要复位指针,使用PLL的lock信号产生复位信号,为fifo添加异步复位后,整体程序正常。

4、示波器探头接入PCLK时寄生电容会增大,产生数据错误问题,需注意。调试阶段-5的延迟问题就是由此解决的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号