VHDL RTL代码及testbench编写

Background

因为使用verilog比较多, 对VHDL不熟, 因此学习下VHDL语法, 并练习写了个简单的分频器和仿真.

RTL design

使用VHDL写一个简单的分频器, 话不多说, 代码如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

--use ieee.std_logic_arith.all;

-- entity clkdiv

entity clkdiv is

port

(

-- clk_in: in bit; -- if clk_in is defined as bit type(not std_logic), rising_edge(clk_in) will generate compilation error

clk_in: in std_logic;

clk_out: out std_logic;

rst_n: in std_logic

);

end clkdiv;

-- architecture

architecture behavior of clkdiv is

-- declare signals

signal cnt : std_logic_vector(7 downto 0);

signal temp : std_logic;

begin

-- count process

PROCESS_CNT: process(clk_in, rst_n)

begin

if(rst_n = '0') then

cnt <= "00000000";

--elsif(clk_in'event and clk_in='1') then

elsif rising_edge(clk_in) then

if(cnt = 9) then

cnt <= "00000000";

else

cnt <= cnt + 1;

end if;

end if;

end process;

-- divider process

PROCESS_DIV: process(clk_in, rst_n)

begin

if(rst_n = '0') then

temp <= '0';

--elsif((clk_in'event) and (clk_in = '1')) then

elsif rising_edge(clk_in) then

if(cnt < 5) then

temp <= '1';

else

temp <= '0';

end if;

end if;

end process;

-- assign clk_out = temp

clk_out <= temp;

end behavior;

testbench simulation

使用VHDL写testbench

library ieee;

use ieee.std_logic_1164.all;

entity tb is -- testbench empty entity, no need to define port

end tb;

architecture behavior of tb is

component clkdiv -- declaration of test entity

port(

clk_in, rst_n: in std_logic;

clk_out: out std_logic

);

end component;

-- port input signal

signal clkin: std_logic;

signal rst: std_logic;

-- port output signal

signal clkout: std_logic;

-- clock cycle definition

constant clk_period: time :=20 ns;

begin -- architecture begin

b1: clkdiv

port map(

clk_in=> clkin,

rst_n => rst,

clk_out => clkout

);

-- generate test clock

clk_gen: process

begin

clkin <= '0';

wait for clk_period/2;

clkin <= '1';

wait for clk_period/2;

end process;

rst_gen: process

begin

rst <= '0';

wait for 15 ns;

rst <= '1';

wait;

end process;

end behavior; -- architecture end

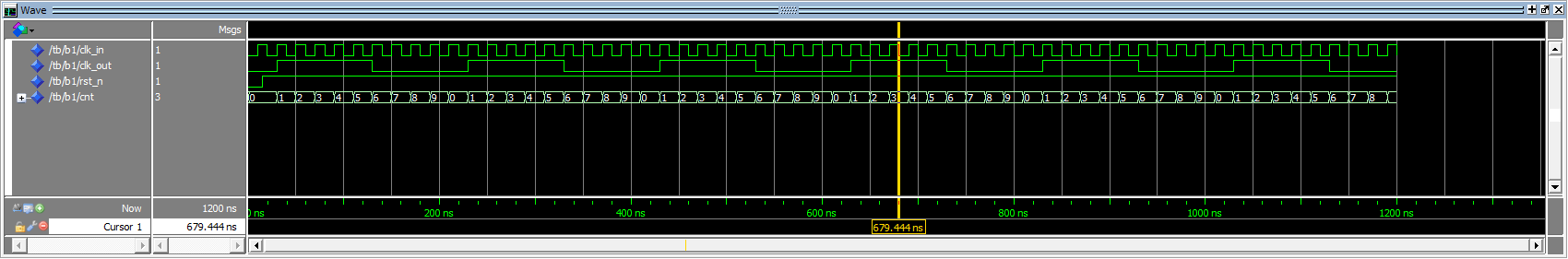

waveform viewing

使用modelsim来进行仿真, 并查看波形

---------------------------------------------

Study needs record, record needs review

---------------------------------------------