计算机组成原理学习之中央处理器(一)

中央处理器是控制计算机完成取指令和执行指令任务的部件;是计算机的核心部件,简称CPU。

CPU的基本认功能分为四个:比较好想的就是指令控制,有指令就有操作,那就是就是操作控制,然后就是比较容易忽略的操作的时间特性,必须注意的一点是计算机类的任何操作都是在一定的周期内有条不紊的进行的,所以这就需要时间控制,最后就是最重要的数据加工。因为电脑本身就是对数据进行加工,这才是它的根本任务。

记起来就是指令控制,操作控制,时间控制,数据加工。

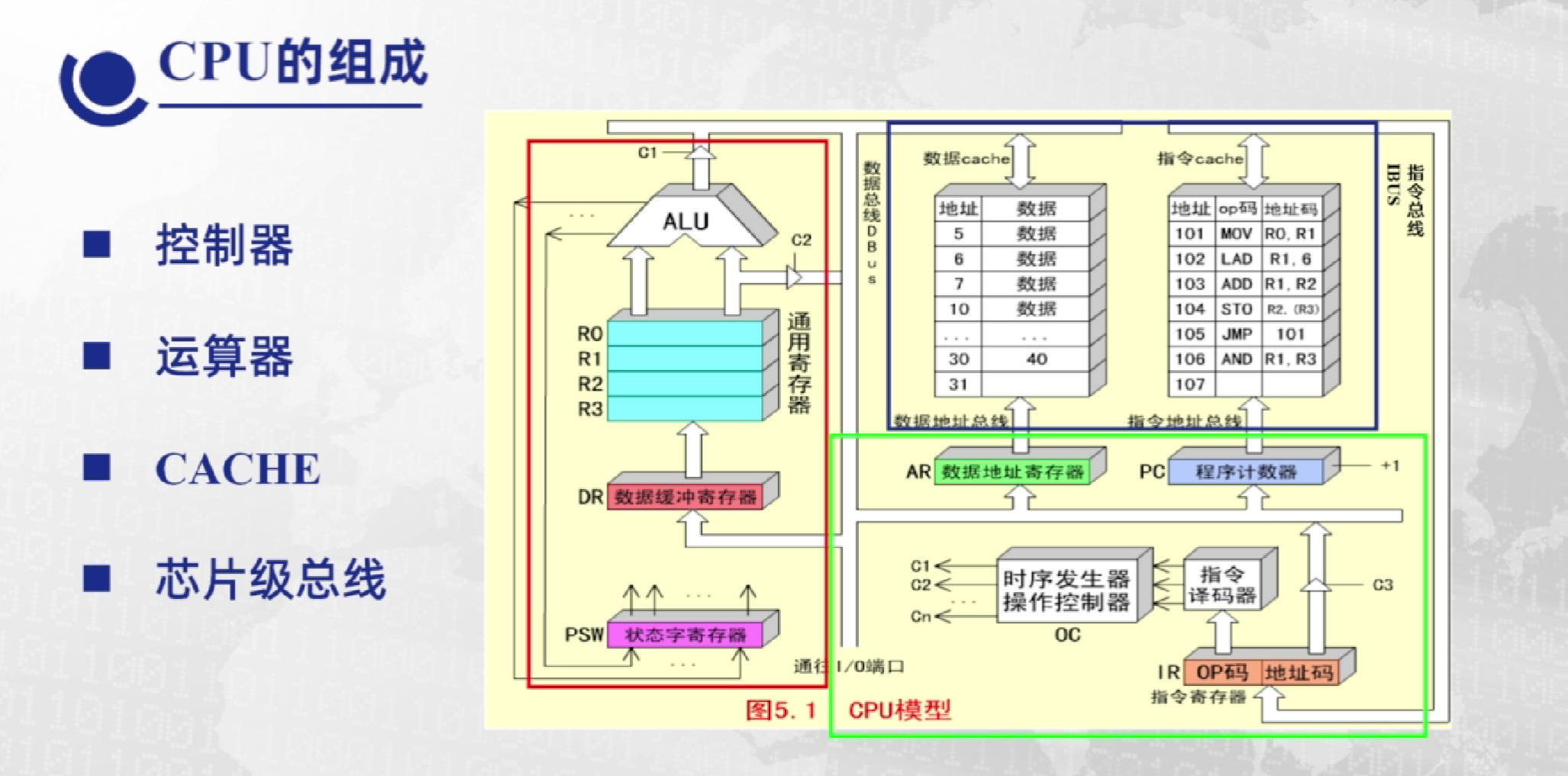

CPU的组成:

控制器是发布命令的“决策机构”,有它来完成协调和指挥整个计算机系统工作。

运算器由算术逻辑单元(ALU),通用寄存器,数据缓冲寄存器(DR)和状态条件寄存器(PSWR)组成,它是数据加工处理部件,运算器所进行的全部操作都是控制器所发出的操作信号来指挥的,所以是执行部件。

Cache是高速缓冲存储器,它是介于CPU和主存之间,引入Cache的目的是为了弥补CPU和内存之间速度的差异。这里由指令Cache和数据Cache,这样,指令和数据可并行处理,提高CPU的处理速度。

最后由于CPU内部采用超大规模集成化电路,所以CPU内部的各种部件需要通过总线进行信息传输。处于CPU内部的总线叫做芯片级总线。

对于运算器和Cache的讲解是在前面的章节(然而我还没学。。。)

所以这章的重点是在控制器中。

控制器的功能:

1.控制取出,解释和执行指令。

1)从内存中取值,并提供下一条指令地址

2)对指令进行译码/测试,产生执行部件的运行所需要的控制信号。

2.只会并控制CPU,内存和I/O设备之间的数据传送。

1)存储器和控制器之间流动的信息————指令流。

2)存储器和运算器之间流动的信息————数据流。

3.中断控制————对异常情况和外部请求的处理。

总的来说,控制器就三个方面的功能,指令,信息流动,中断处理。

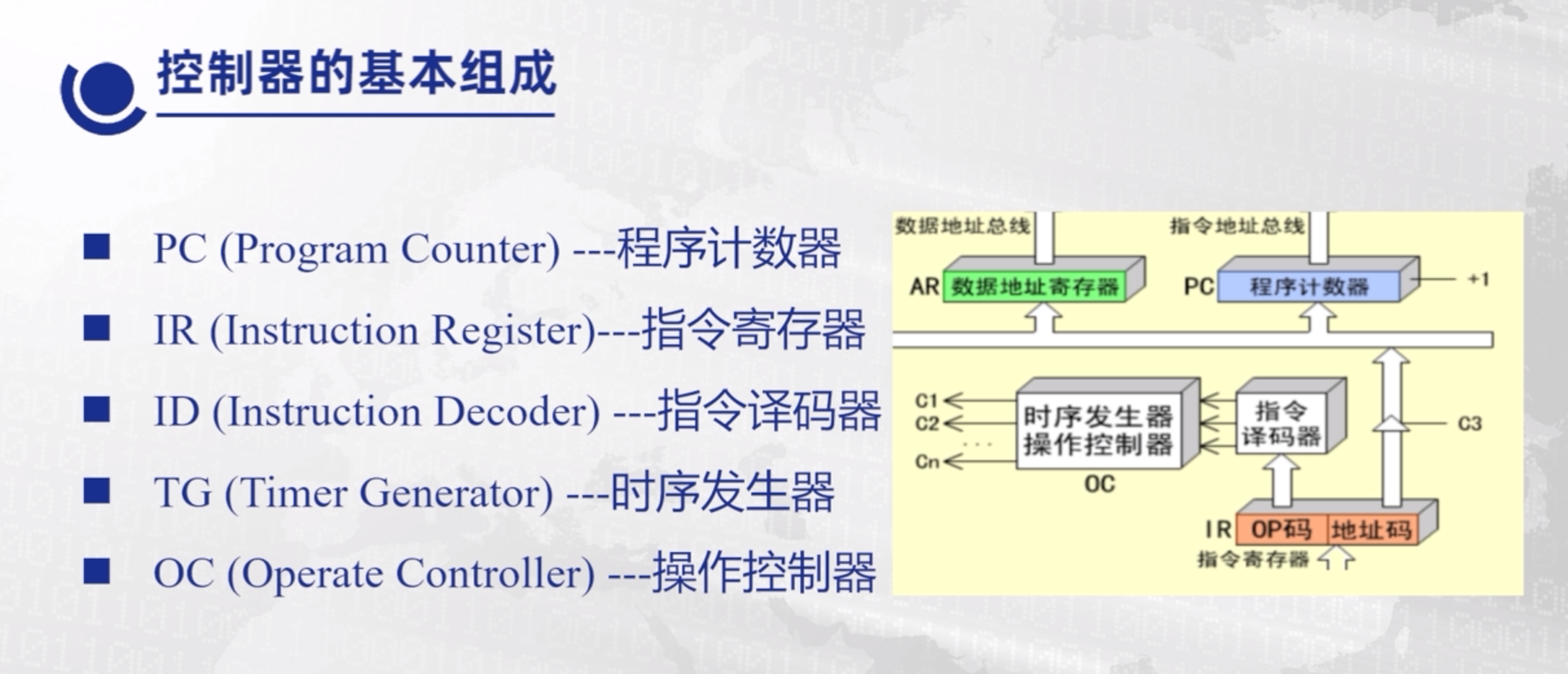

1.指令译码器(Instruction Decoder)(ID):

对指令的操作码译码,为操作控制器提供输入信号。

2.操作控制器(Operater Controller)(OC)(听名字就高大上):

根据指令操作码和地址码,时序信号,产生各种控制信号序列,建立正确的数据通路,从而完成取指令和执行指令的控制。

操作控制器分为三种:时序逻辑性,存储逻辑性,时序逻辑和存储逻辑结合型。

由以上三种类型可分为:

硬布线控制器(时序逻辑型)

微程序控制器(存储逻辑型)

硬布线控制和微程序控制的混合型。

3。时序发生器(Time Generateor)(TG):

产生各种时序信号

对各种操作实施时间上的控制。

其中前四个是控制器中的,后两个是运算器当中的。

接下来就是关于CPU中时序的知识点。

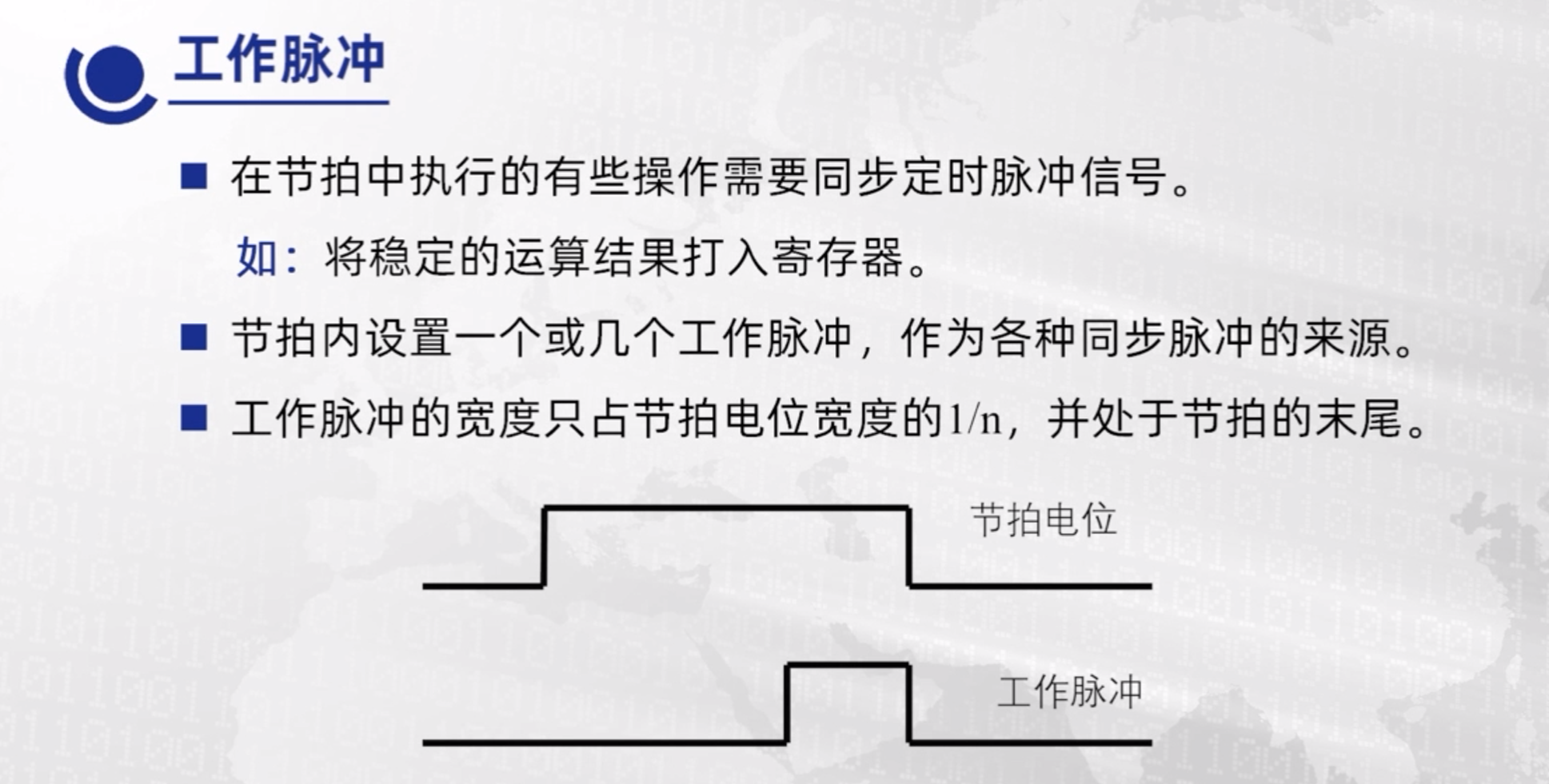

CPU用来约束自己的操作的“作息表”,需要一些时序信号来约束,而时序信号有两种,节拍电位和工作脉冲。

首先来看节拍电位

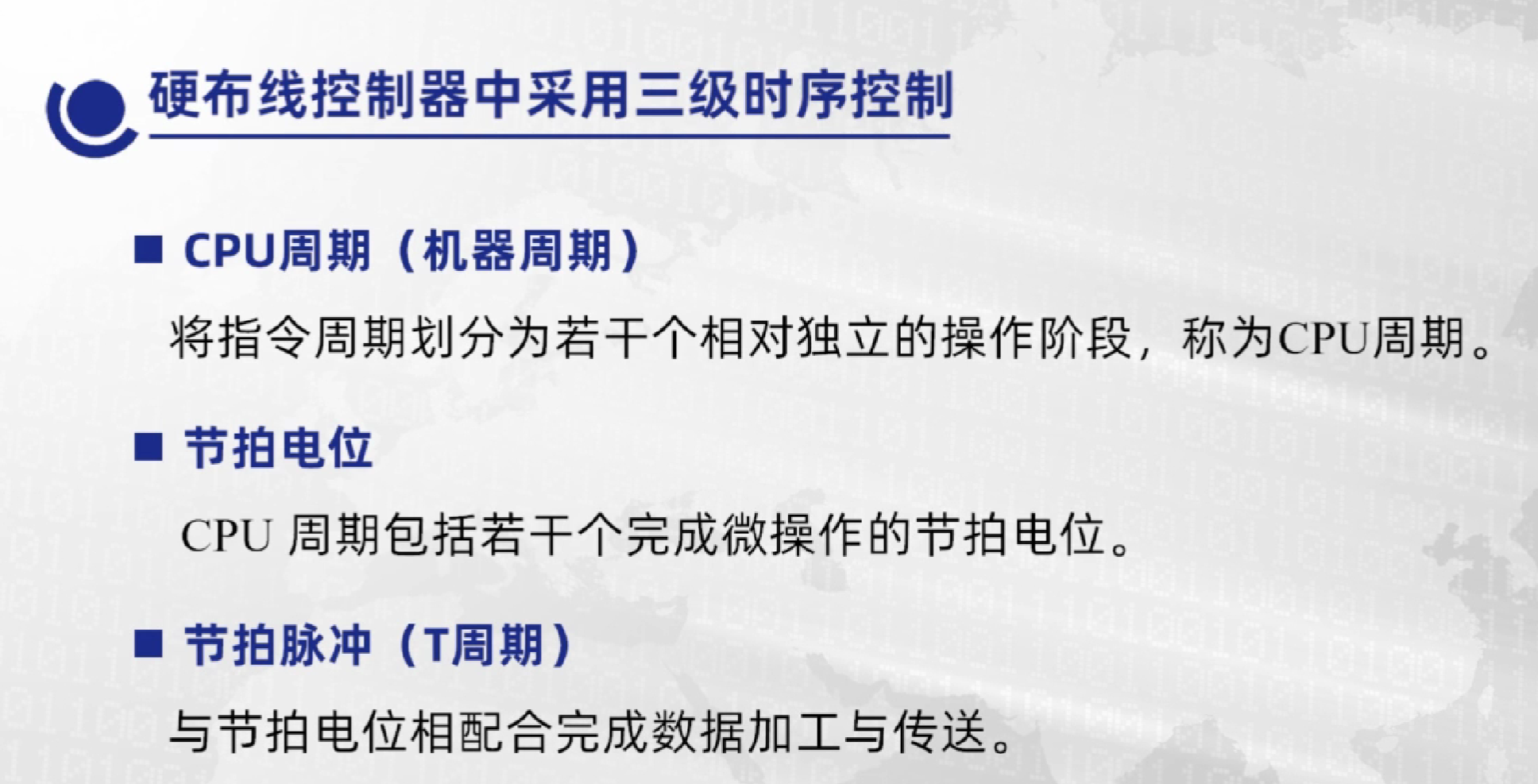

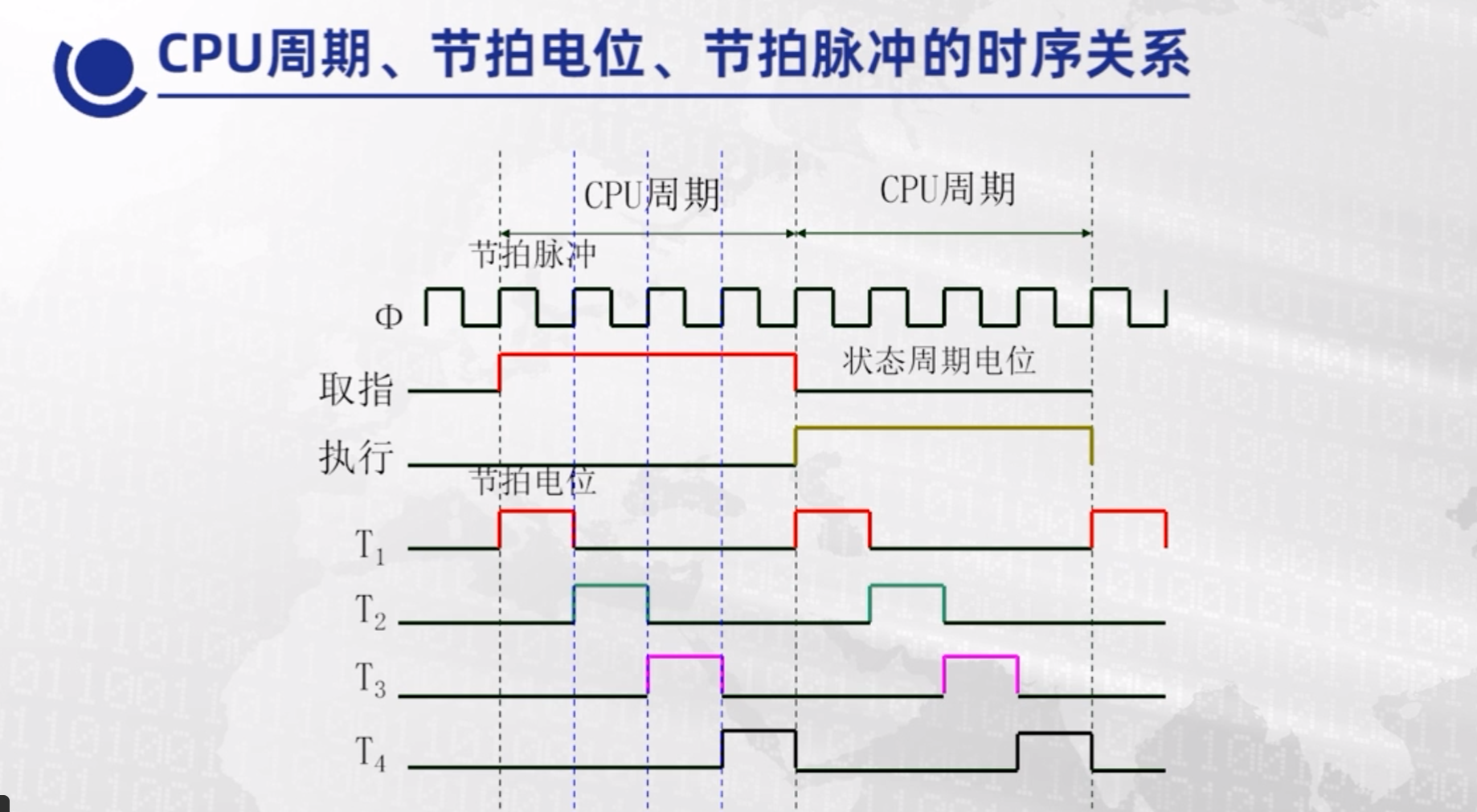

从定义上看,节拍电位的定义和T周期容易搞混,但实际上工作脉冲才是T周期,可以这样理解,一个CPU周期例如取指令,其实包含了很多微指令,而每个微指令又包含了很多的时间脉冲,所以节拍电位可以和这些微指令对应上。

统一节拍法就是不管三七二十一,在所有微操作中找出时间最长的微操作作为节拍的时长,在所有CPU周期中找出最多的节拍数的CPU周期作为每个CPU周期中的节拍数,这样起码能保证能执行所有的操作。

显然,三种方法中,效率最高的肯定是分散节拍法,但电路设计应该难度偏大,而延长节拍法则更像是定长节拍法和不定长节拍法的综合,兼顾了运行效率和设计难度。

工作脉冲的理解,学过数字逻辑,所以可以互补的理解下,在触发器中,当脉冲变化时才能改变其状态,这也是同理,节拍电位必须一致保持,当工作脉冲来临的那一刻,才能真正的改变其状态。

而微程序控制器中采用节拍电位,节拍脉冲二级时序控制。

浙公网安备 33010602011771号

浙公网安备 33010602011771号