Quartus II 16.0+modelsim-alter10.4

一、打开Quartus,点击new project Wizard。选择新建工程。点击next之后,在需要填写项目的地址,和项目名称。(项目地址自己选择,项目名称需要和之后建立的顶层实体(模块)名称一致)。

二、在之后的add files环节可跳过。之后再添加。然后选择自己的器件类型。

三、之后就看到界面。点击file->new file ->选择建立的文件类型。这选择verilog类型。点击OK之后就可以写自己的代码。

四、完成后点击保存。此刻注意文件名和顶层实体名称一致,然后加入后缀。(verilog后缀为.v)

也就是,工程名,文件名,顶层实体名(或者称之为模块)要一致。

五、完成后点击编译即可。

点击上图中蓝色的三角形即可。会有窗口提示是否有误。有误的话,根据提示修改。

重点是与modelsim的仿真:

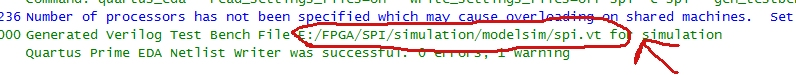

六、生成TestBench文件。点击Processing-》Start->Start Test Bench Tempalte Writer.会在下方提示生成文件的位置

七、打开TestBench可对TestBench写自己的激励文件。激励文件中系统生成的模块名在第九步会有用。

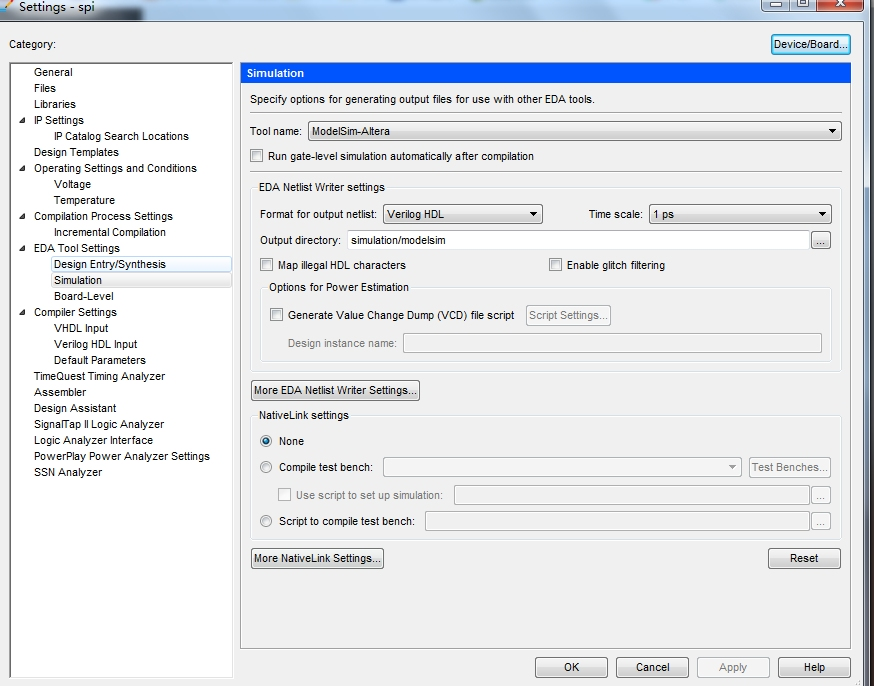

八、右键项目,点击settings。出现界面。

九、在EDATool Setting-》Modelsim。进行配置。Tool-name选择自己用的modelsim或者modelsim-altera.

在EDA Netlist Setting ->Format for output 选择语言。在output directory 选择路径。一般按上图路径选择。simulation-》modelsim。

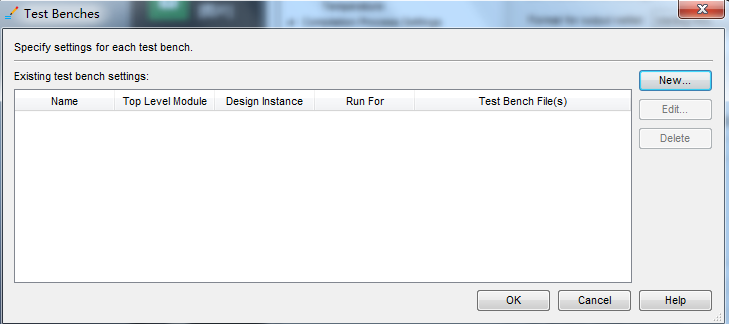

在 compile testbench 点击testbench。出现下图。点击new.

.

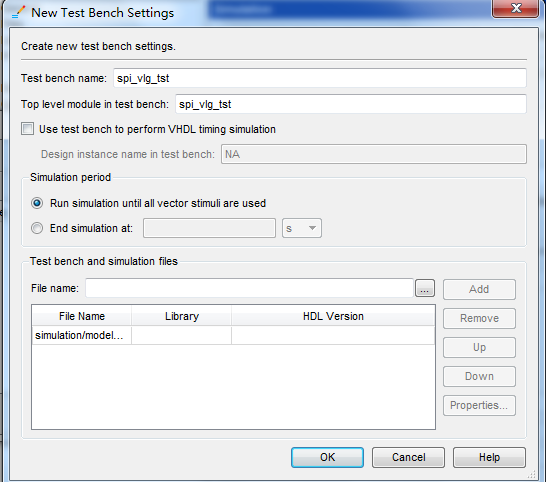

出现下图

。

在TestBenchname这块要把系统生成的测试文件的模块名复制过来,这步很重要!!!

在Filename这块,点击后面的..,选择激励文件,后点击add,就看到添加进去。结果如上图。连续点击OK后,配置完成。

十、点击菜单栏中的tolls-》Run simulation Tool->RTL simulation。会自动启动modelsim,出现波形。

注:中间可能会提示添加modelsim安装包的位置。

若没出现modelsim波形很有可能和激励文件有关系。建议:一开始自己不要填写激励文件。就用系统自动生成的。在确保能产生波形之后再写自己的激励代码再simulation.

仿真波形没出现可能的原因:

①测试文件initial部分在最后是时间延时导致。

②可能给某个变量进行加减法运算未赋初值。