计算机体系结构-hw5

计算机体系结构-hw5

前言

Problem 1

(a)

cache总大小(data array size):1KB

block size: 8bytes

因此,组(sets)个数:1024B / 8B = 128

(b)

由于是直接相联映射,128个组,1个路,每个组中可以存8B(8个地址,字节编址)。

因此,按照上述的内存访问序列,我们分析如下:

- 0x0: 访问第一个组,发现没有cache,cache miss(装入0x0-0x7)

- 0x8: 访问第二个组,发现没有cache,cache miss(装入0x8-0xF)

- 0x10:访问第三个组,发现没有cache,cache miss(装入0x10-0x17)

- 0x18:访问第四个组,发现没有cache,cache miss(装入0x18-0x1F)

- 0x20:访问第五个组,发现没有cache,cache miss(装入0x20-0x27)

- 0x28:访问第六个组,发现没有cache,cache miss(装入0x28-0x2F)

这些地址用二进制表示:

0000000 000

0000001 000

0000010 000

0000011 000

0000100 000

0000101 000

注:index的位数:7bits,block offset的位数:3bits

综上所述,上述的访问序列,均会访问不同的组,都会缺失,因此缺失率为100%。

(c)

- 对于第一个选项,增加相关度为2,则:

- 组个数:1024B / 8B / 2ways = 64

- index bits = 6

- block offset = 3

这样的话,这些地址用二进制表示:

000000 0 000 -> (0组0路,地址:0-7)

000000 1 000 -> (0组1路,地址:8-F)

000001 0 000 -> (1组0路,地址:0-7)

000001 1 000 -> (1组1路,地址:8-F)

000010 0 000 -> (2组0路,地址:0-7)

000010 1 000 -> (2组1路,地址:8-F)

按照上述的内存访问序列来访问(同组不同路),我们发现缺失率还是100%。

- 对于第二个选项,增加block size为16bytes,采用直接相联映射,则一个组有一个block,因此,一个组的大小:16B:

- 组个数:1024B / 16B / 1ways = 64

- index bits = 6

- block offsets = 4

这样的话,这些地址用二进制表示:

000000 0000 -> (0组,地址:0-F)

000000 1000 -> (0组,地址:0-F)

000001 0000 -> (1组,地址:0-F)

000001 1000 -> (1组,地址:0-F)

000010 0000 -> (2组,地址:0-F)

000010 1000 -> (2组,地址:0-F)

按照上述的内存访问序列访问:

- 0x0:访问第一个组,发现没有cache,cache miss(装入0x0-0xF)(因为块大小为16B)

- 0x8:访问第一个组,cache hit

- 0x10:访问第三个组,发现没有cache,cache miss(装入0x10-0x1F)

- 0x18:访问第四个组,cache hit

- 0x20:访问第五个组,发现没有cache,cache miss(装入0x20-0x2F)

- 0x28:访问第六个组,cache hit

总上所述,缺失率为:3 / 6 = 50%,因此选择第二个选项。

Problem 2

(a)

- N = 2,代表二路组相联:一个组两个路。

- 组个数:32K words / 2words / 2 ways = 8K

- index bits = 2^3 /* 2^10 = 13 bits

- 因为block size = 2 words,所以block offset = 1 bit

- 因为word size = 32bits = 4Bytes(一个字可以存四个地址)

- 所以 Byte offset = 2 bits

- 因此:tag bits = 32 - 13 - 2 - 1 = 16bits

(b)

tag size = 8K * 2 * 16bits = 256Kbits

(c)

size of each cache set =

- Word size = 32bits

- 一个block为2words,因此data:64bits

- tag:16bits

- vaild bit 和 dirty bit 共 2bits

- cache way:64 + 16 + 2 = 82 bits

- 又因为是二路组相联,因此:cache set bits = 82 * 2 = 164 bits

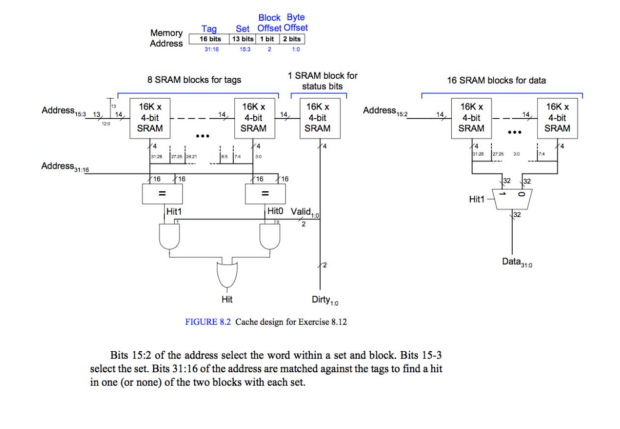

(d)

注:设计不了一点,太难了。如果你有需要,请参考计算机体系结构:量化研究方法

致谢

[1] 以上图片来自于计算机体系结构刘珂老师的课程

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 分享一个免费、快速、无限量使用的满血 DeepSeek R1 模型,支持深度思考和联网搜索!

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· ollama系列01:轻松3步本地部署deepseek,普通电脑可用

· 25岁的心里话

· 按钮权限的设计及实现