基于EP4CE6F17C8的FPGA开发流程(以半加器为例)

一、电路模块

1、 芯片

FPGA芯片型号为EP4CE6F17C8,属于ALTERA公司Cyclone IV系统的产品。此型号为BGA封装,共有256个引脚。芯片实物图如下所示。

其主要参数如下表所示。

2、 LED

开发板板载了4个用户LED发光二极管。4 个用户LED部分的原理图如下图所示,当 FPGA的引脚输出为逻辑 0时,LED会熄灭。输出为逻辑1时,LED被点亮。

其实物图如下所示。

LED的引脚分配见下表。

3、 按键

开发板板载了4个独立按键,其中有3个用户按键(KEY1~KEY3),1个功能按键(RESET)。按键按下为低电平(0),释放为高电平(1),4个按键的原理图如下图所示。

其实物图如下所示。

按键的引脚分配见下表。

二、实验代码

本例实现一位数的半加器,输入使用两个按键key1和key2,输出使用两个发光管led1和led2。代码使用Verilog编写,如下。

module h_adder_1bit(key1,key2,led1,led2); input key1,key2; output led1,led2; assign led2 = key2 ^ key1; assign led1 = key2 & key1; endmodule

上述代码也可以写成如下的形式,把端口定义直接放到端口名列表里面,建议采用这种形式来书写。

module h_adder_1bit( input key1,key2, output led1,led2 ); assign led2 = key2 ^ key1; assign led1 = key2 & key1; endmodule

三、代码说明

1、关键词module与end module之间描述了一个模块的功能,一个.v文件只能有一个模块。module后面是模块名称,其后的括号定义信号端口。

2、端口可申明为input、output及inout三种模式之一,默认为wire类型。

3、assign语句为并行语句(同时执行),用于引导纯布尔型的赋值表达式。assign语句只能处理wire类型的变量,描述输入与输出之间的逻辑关系。

四、实验步骤

1、新建工程

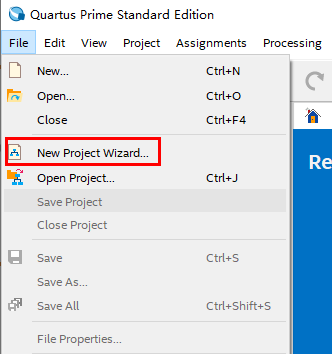

启动Quartus,点击File->New Project Wizard,通过向导来建立工程,如下图如示。

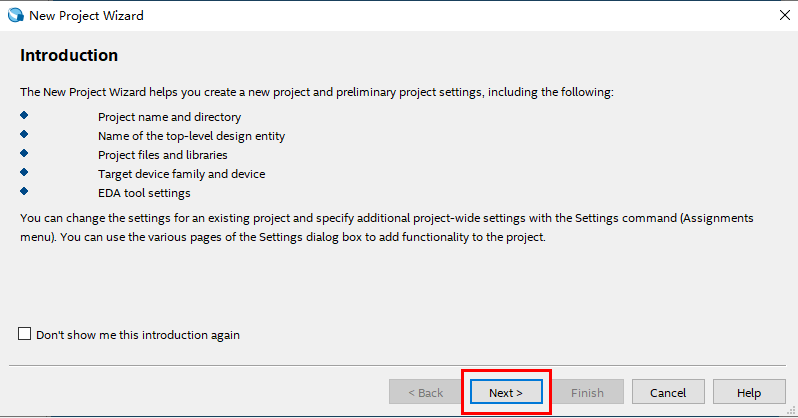

接着出现如下图所示的界面,提醒你建立工程需要的步骤,点击Next继续。

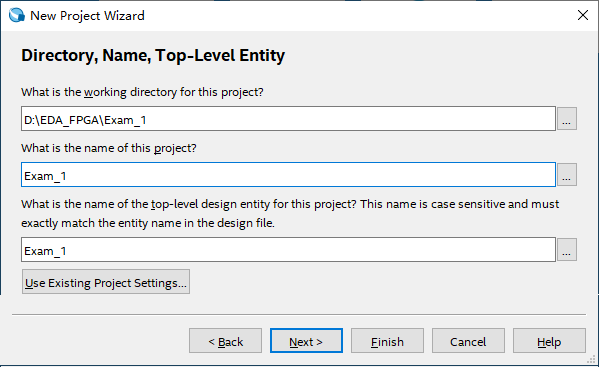

之后出现如下图所示的对话框,让你确定工程所在的文件夹及工程名称,根据自己的情况输入。需要注意的是,工程名称与顶层设计实体的名称是一致的,输入时会连动。另外,工程文件不要放在桌面或某个盘的根目录下,要放置到一个具体的文件夹中,如本例放在了D:\EDA_FPGA\Exam_1下。输入完成后点击Next进入下一步。

接下来会问你建立工程的类型,默认工程为空,如下图所示,点击Next继续。

接着出现如下图所示的对话框,让你向建立的工程添加文件。由于目前还没有文件,所以直接点击Next进入下一步。

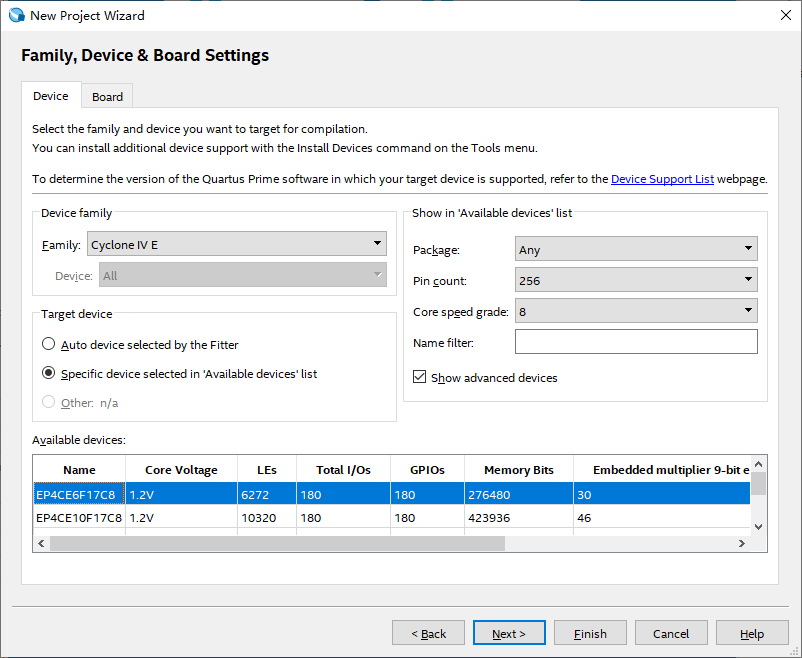

之后出现器件选择的对话框,如下图所示。在该对话框中,需要确定你使用的FPGA芯片型号。可通过条件筛选来缩小选择范围,先点击Family右边的下拉列表框,选择Cyclone IV E系统,再点击Pin count右边的下拉列表框,选择256脚,再点击Core speed grade右边的下拉列表框,选择8,最后就可在最下边的器件列表中找到EP4CE6F17C8的型号,点击选中它,然后点击Next按钮进入下一步。

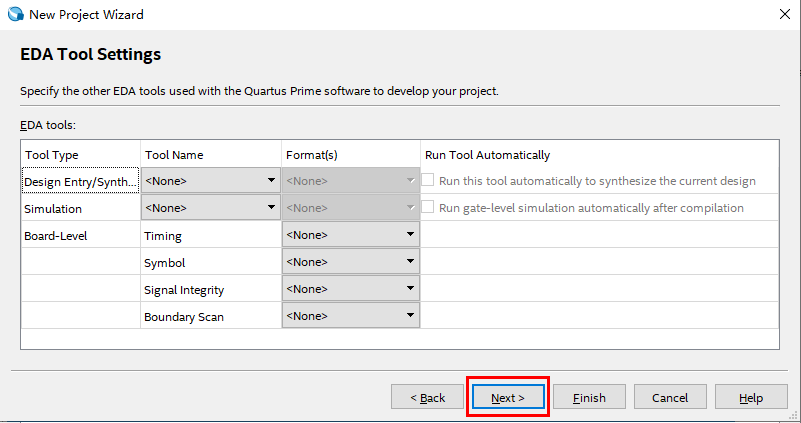

接下来出现如下图所示的对话框,让你选择工具设置,这里不需要配置,直接点击Next进入下一步。

最后出现如下图所示的新建工程的简要概况,可阅览一下,然后点击Finish按钮结束。

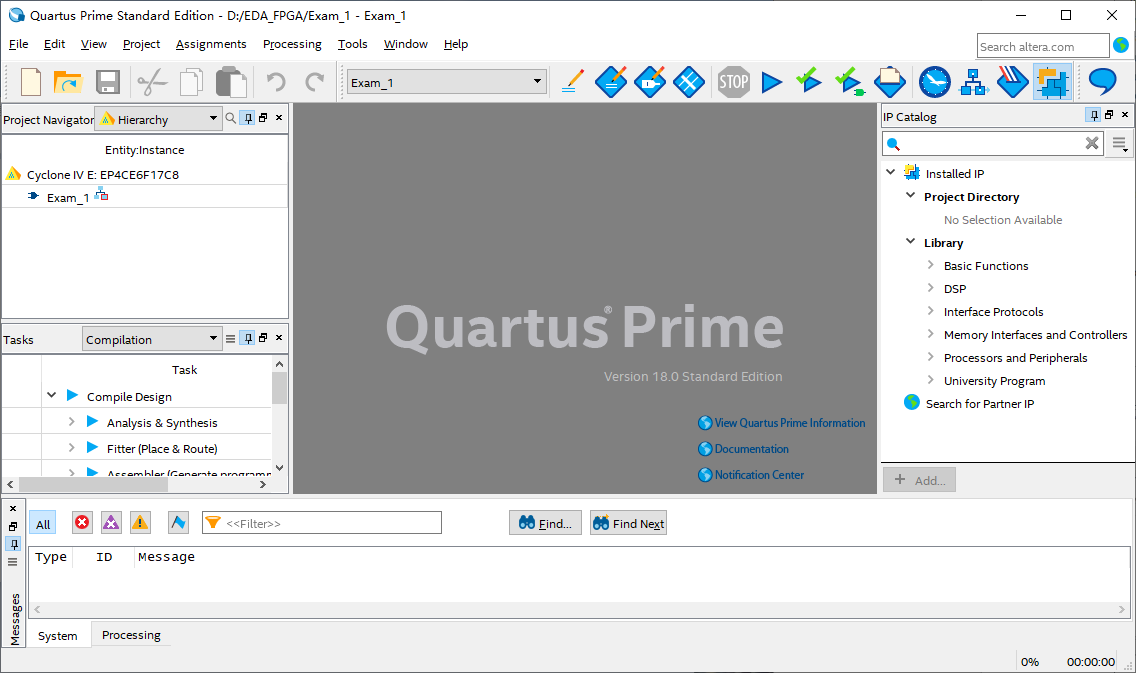

建立好的工程界面如下图所示。

2、编写代码

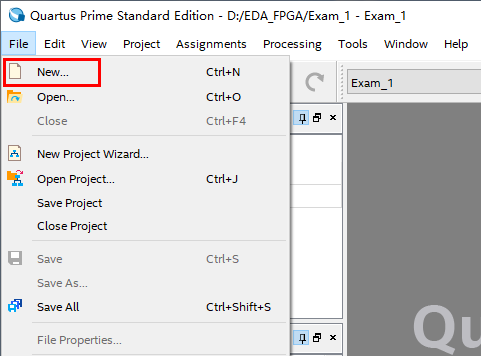

在上面建好的工程中,点击File->New,新建一个项目,如下图所示。

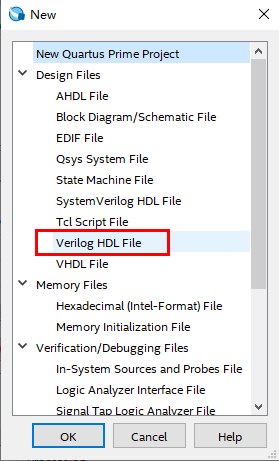

在打开的对话框中,点击选中Verilog HDL File一项,如下图所示,然后点击OK确定。

接下来在新建的空白文档中输入前面半加器的Verilog代码,完成后点击保存,这里需要特别注意,保存文件的名称要与描述模块的名称一致,后缀为.v,如下图所示。

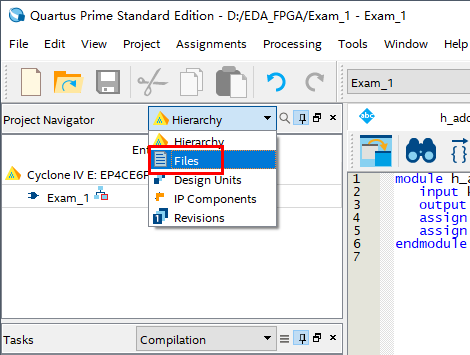

3、设置为顶层实体

在新建立的工程中,默认顶层实体为工程名称,这里需要修改一下。点击Hierarchy下拉列表框,选择Files,如下图所示。

然后选中刚才添加进来的文件h_adder_1bit,点击右键,选择Set as Top-Level Entity一项,把该文件设置为顶层实体,如下图所示。

最后再确认一下,点击刚才的下拉列表框回到Hierarchy下,可以看到顶层实体已经变成了刚才新建的文件,如下图所示。

4、管脚约束

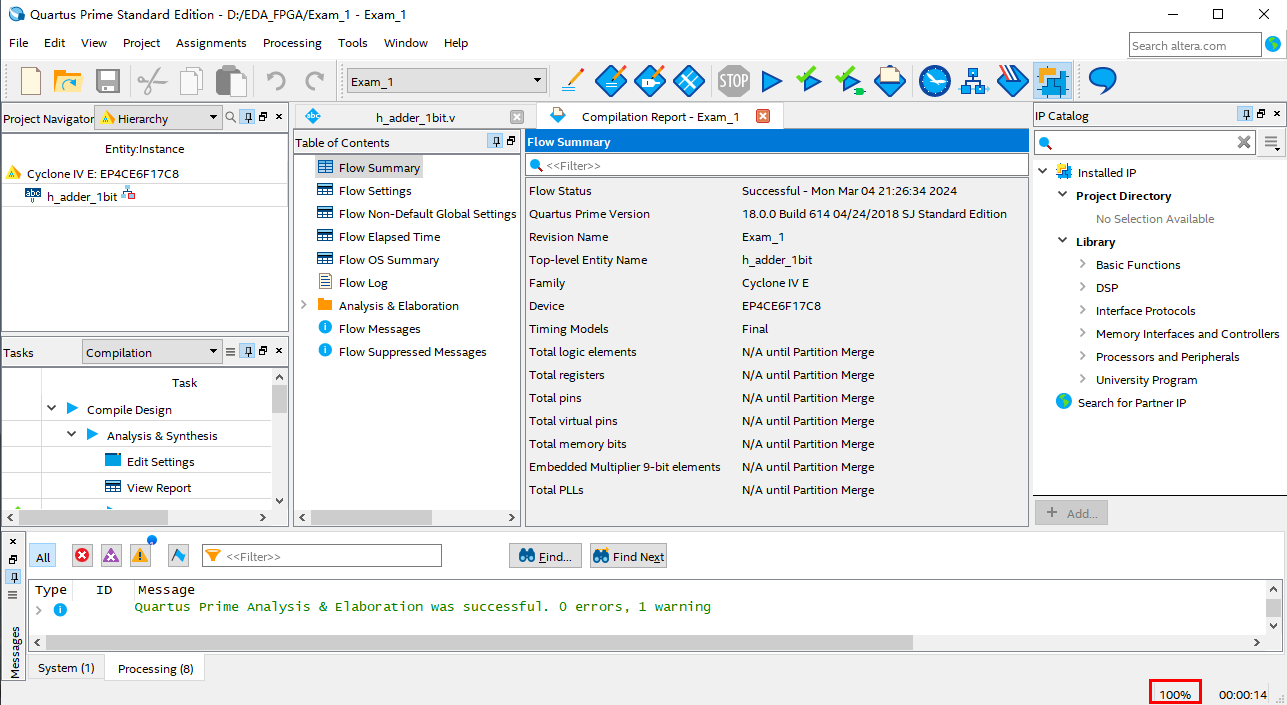

在上面新建好的工程中,并没有把芯片的引脚与代码中的端口进行映射。在前面给出的电路图中,已经实现了芯片管脚与外围器件的连接。而这里要做的是,把芯片具体的管脚与代码中所描述的端口联系起来,因为在Verilog中只描述端口,并没有指定具体的芯片引脚,而管脚设置就是进行这个映射,它是通过开发环境Quartus的支持来实现的。在设置之前,由于Quartus还不知道代码中描述的有哪些端口,所以需要先对工程进行一下综合,点击工具条上的综合按钮,如下图所示。

综合完成之后,如果没有报错,会出现如下图所示的界面。注意综合需要一定的时间,一定要等到右下方显示的进度为100%时,才表明综合结束。如果其间有报错,则根据提示进行修改。

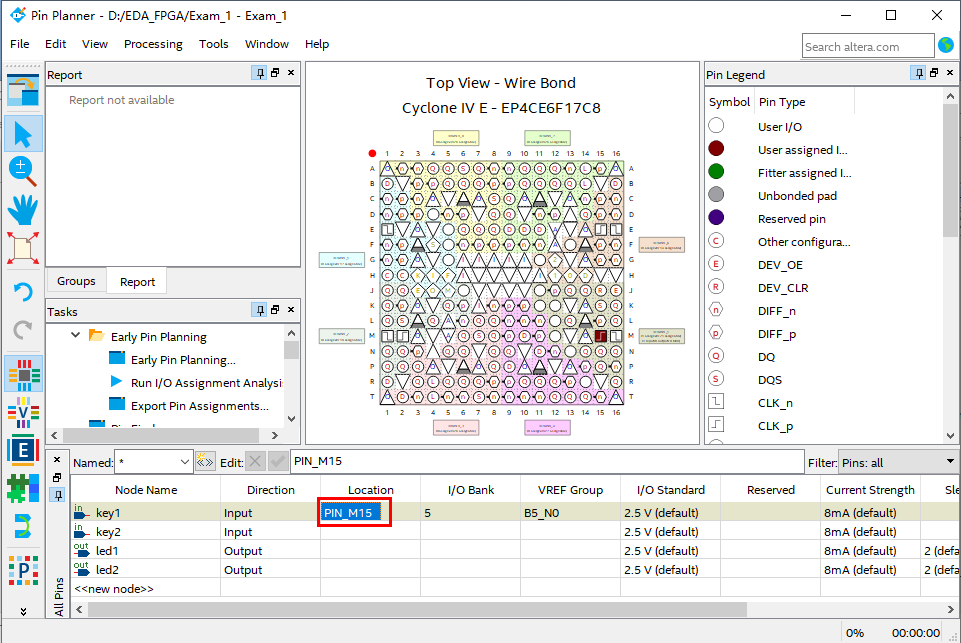

确保综合成功后,点击Assignments->Pin Planner,如下图所示,打开管脚配置的对话框。

在打开的对话框中,先对端口key1进行映射,点击key1一行对应的location一格,输入m15然后回车,它会自动填充完整(PIN_M15),如下图所示。

参照前面的电路图,把与key及led相连接的4个端口都进行映射绑定,完成后如下图所示。

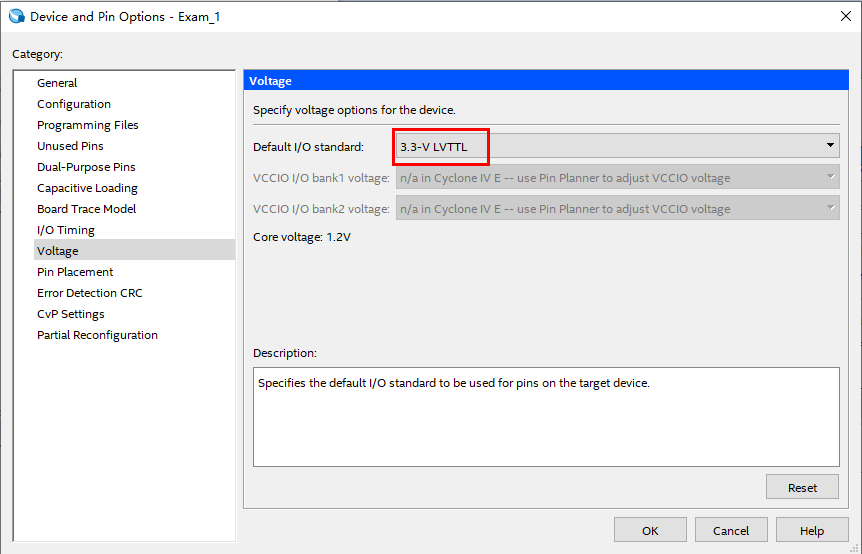

全部完成后,不需要保存,直接关闭对话框即可。接下来还需要对管脚的一些属性进行配置,点击Assignments->Device,如下图所示,打开器件对话框。

在打开的对话框中,点击Device and Pin Option按钮,如下图所示。

在打开的对话框中,先点击左边的Unused Pins,然后在右边点击下拉列表框,选择As input tri-stated,即把未使用的管脚全部设置为三态输入模式,如下图所示。

之后点击左边的Dual-Purpose Pins,然后把右边所有的下拉列表框,都选择为Use as regular I/O项(注:每个下拉列表框需要用鼠标点击三次才能选择),即把管脚都设置为标准I/O口,如下图所示。

最后点击左边的Voltage,然后把右边Default I/O standard下拉列表框,选择为3.3-V LVTTL项,即把电源选择为3.3V,如下图所示,完成后连续点击ok按钮回到主界面。

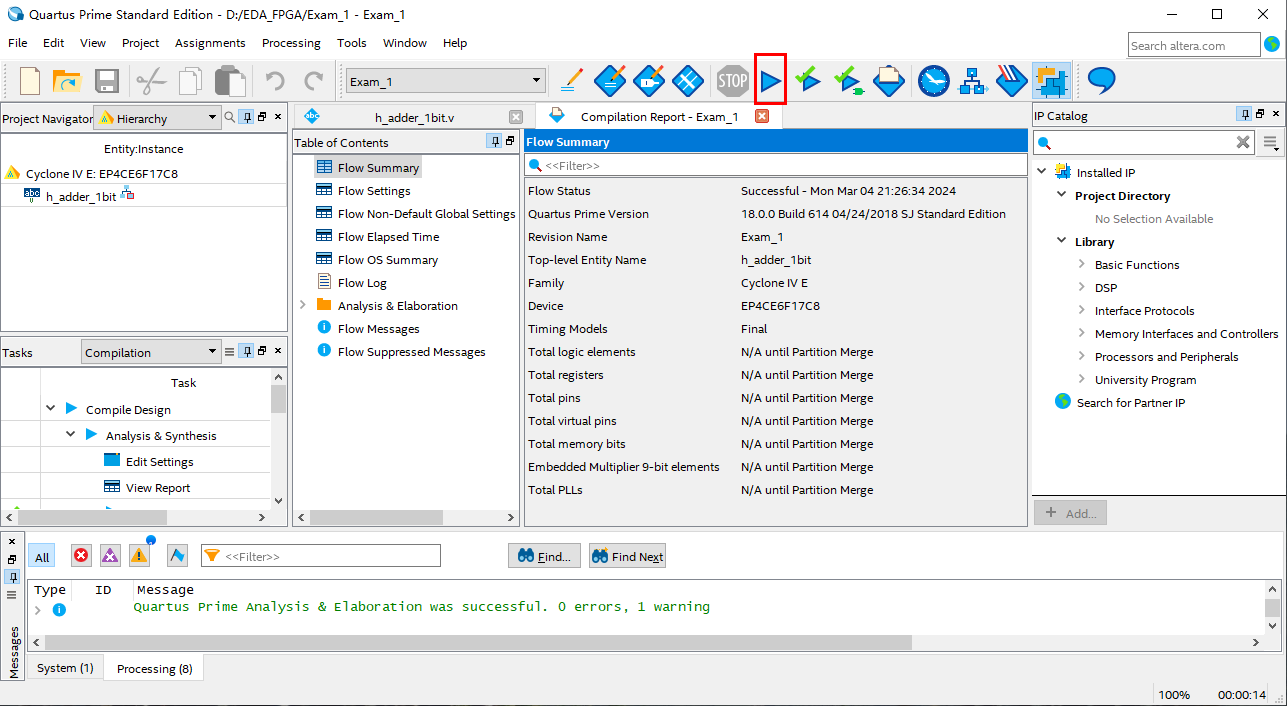

5、编译工程

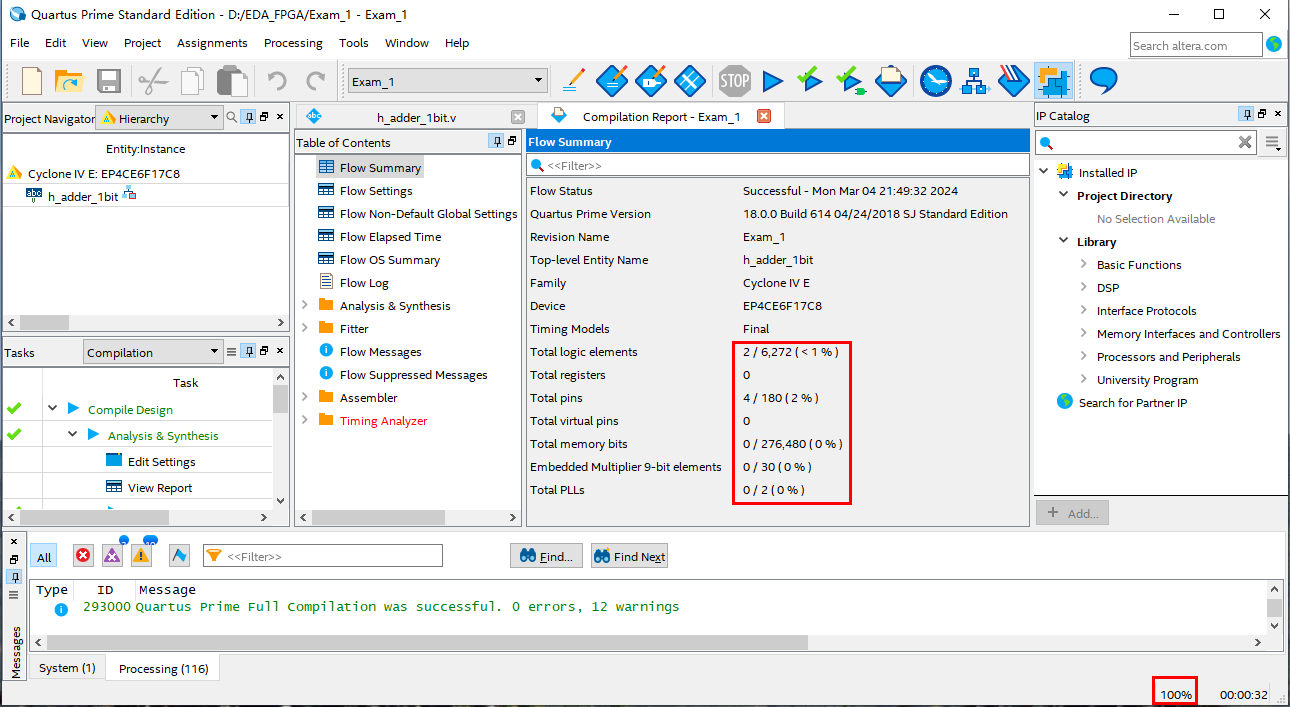

以上设置全部完成后,就可以编译工程了。点击工具条上的编译按钮,如下图所示,对整个工程进行编译。

工程编译需要一定的时间,等待右下边的进度条显示100%后,编译才成功,此时会显示工程所用逻辑门的个数,以及使用的管脚数量等信息,如下图所示。

还可以查看一下生成的电路原理图,点击菜单Tools->Netlist Viewers->RTL Viewer,会打开RTL浏览窗口,如下图所示。可看到综合出来的半加器由一个“与门”和一个“异或门”构成。

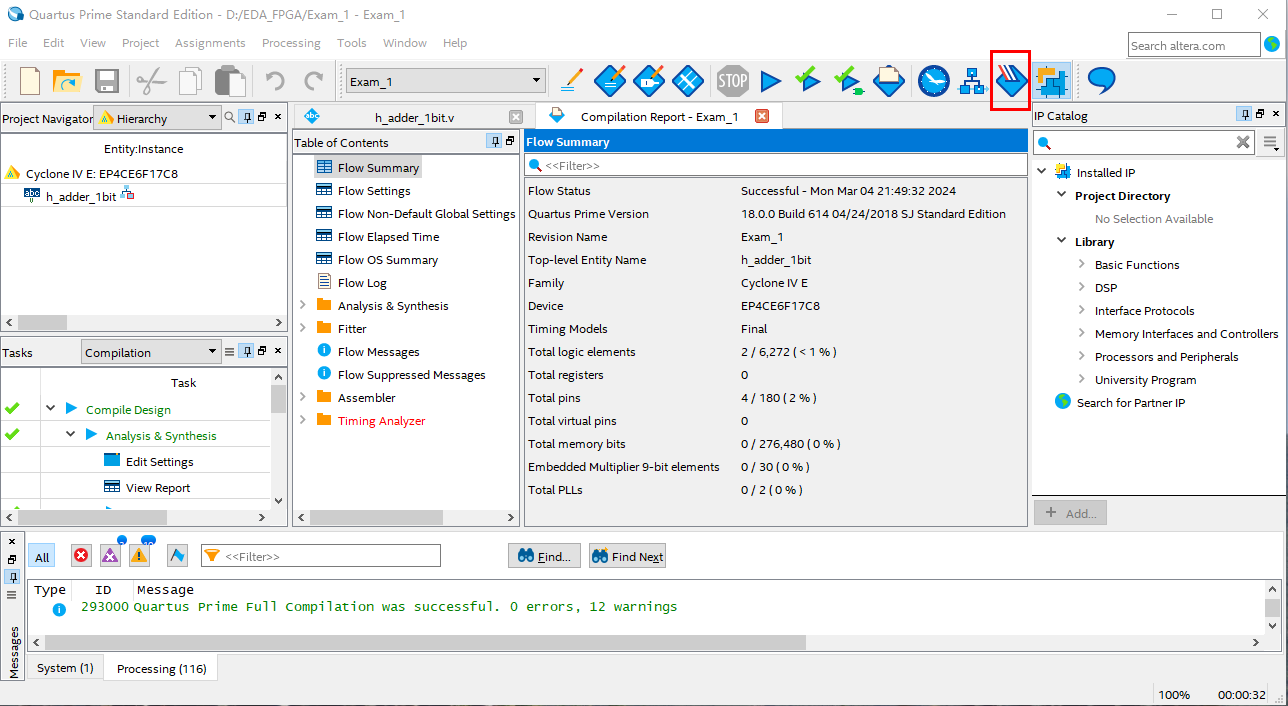

6、下载运行

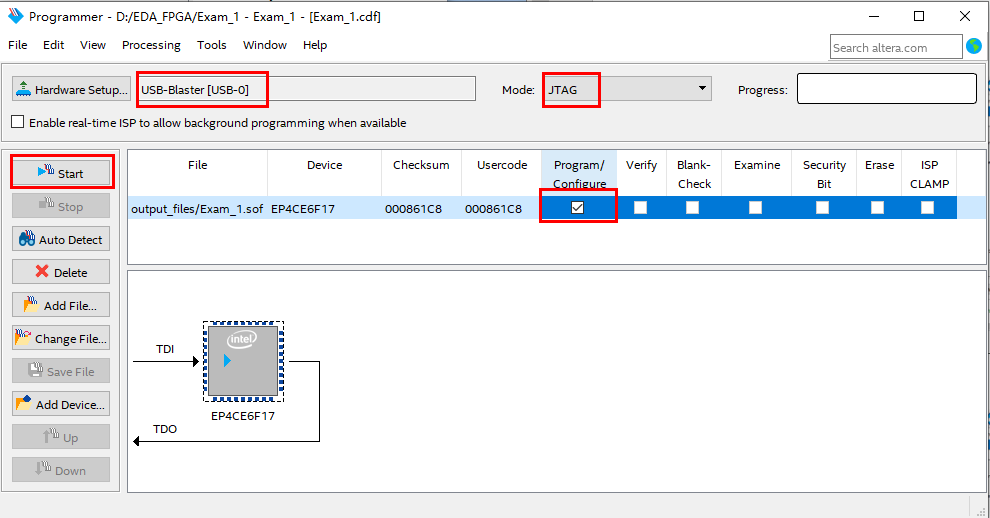

编译成功后,就可以把结果下载到开发板上进行验证。先给开发板上电,然后点击工具条上的编程按钮,如下图所示。

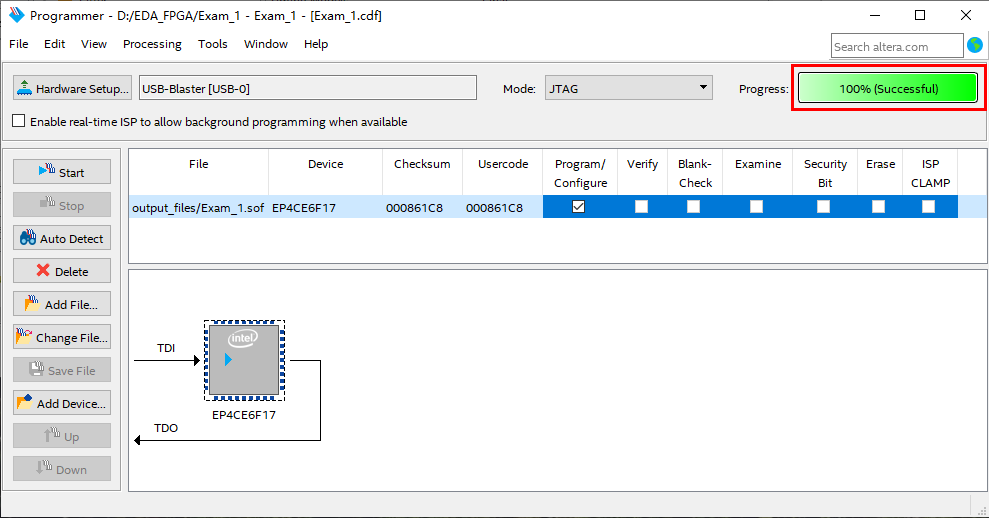

接着会出现如下图所示的对话框。先确认下载器已经找到(USB-Blaster[USB-0]),再确认下载模式为JTAG方式,然后在下载文件一行中确认已勾选了Program/Configure一项,最后点击左边的Start按钮进行下载。

下载成功后,会在进度条显示100%,如下图所示。注意,这里的下载只是下到FPGA芯片的内存中,掉电就消失了。

7、结果验证

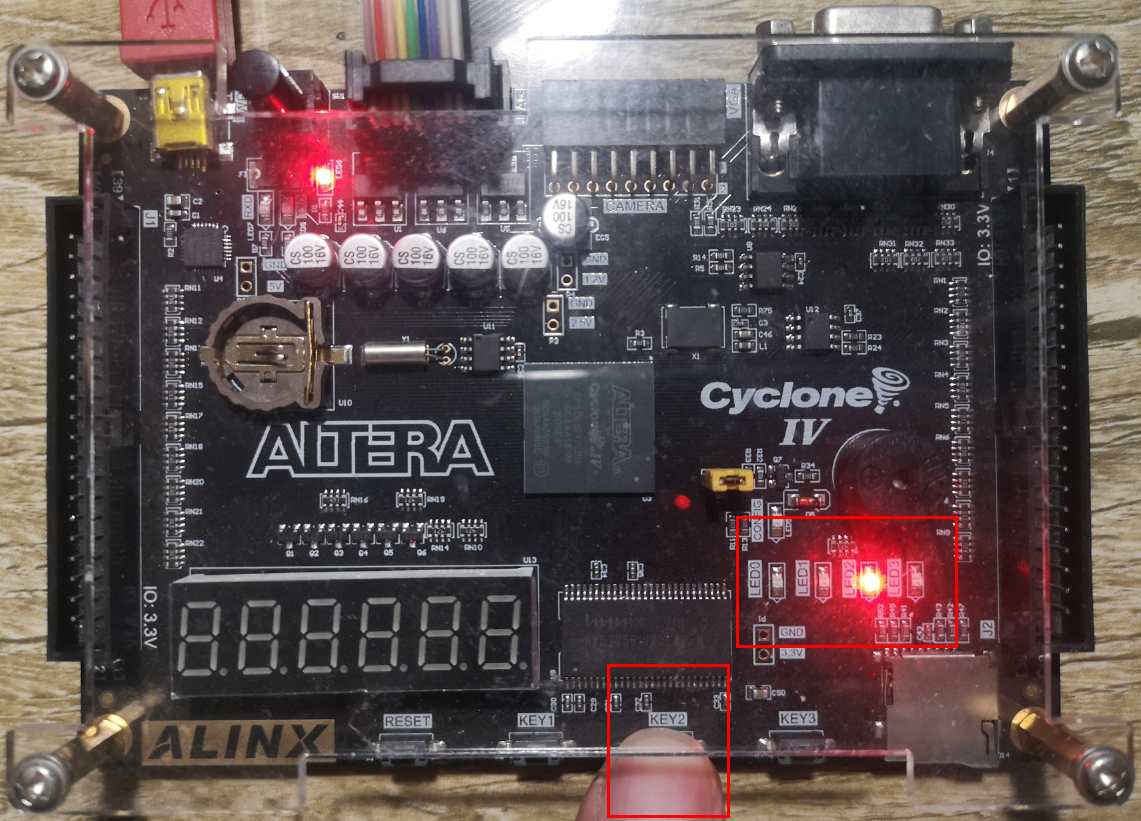

按照前面的电路,按键key没有按下时为1,按下时为0,输出为1时发光管led点亮,为0时熄灭。观察开发板,当key都没按下时(值都为1),led1亮(值为1),led2灭(值为0),如下图所示。证明,当进行1+1时,进位(led1)值为1,输出(led2)值为0。

当key1被按下时(值为0),led1灭(值为0),led2亮(值为1),如下图所示。证明,当进行0+1时,进位(led1)值为0,输出(led2)值为1。

当key2被按下时(值为0),led1灭(值为0),led2亮(值为1),如下图所示。证明,当进行1+0时,进位(led1)值为0,输出(led2)值为1。

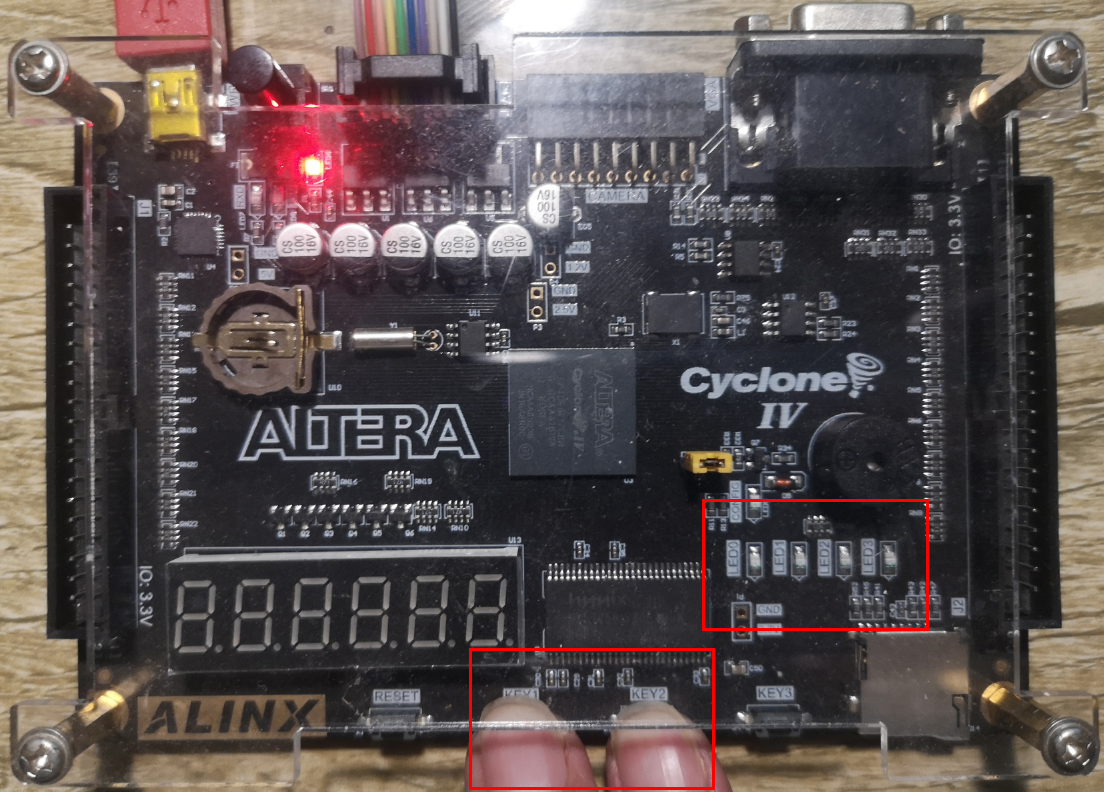

当key都被按下时(值都为0),led1灭(值为0),led2灭(值为0),如下图所示。证明,当进行0+0时,进位(led1)值为0,输出(led2)值为0。

8、固化到FLASH中

按照前面的方法下载程序,在开发板掉电后,程序也就消失了。为了让程序在开发板上电后就能执行,就需要把程序固化到外部的FLASHROM器件中,当开发板上电时,会自动读取并运行。在Quartus中,工程程序编译后生成的文件以.sof结尾,它不能直接装入到FLASH中,需要转换一下格式。在Quartus中点击File->Convert Programming File,如下图所示,打开程序转换对话框。

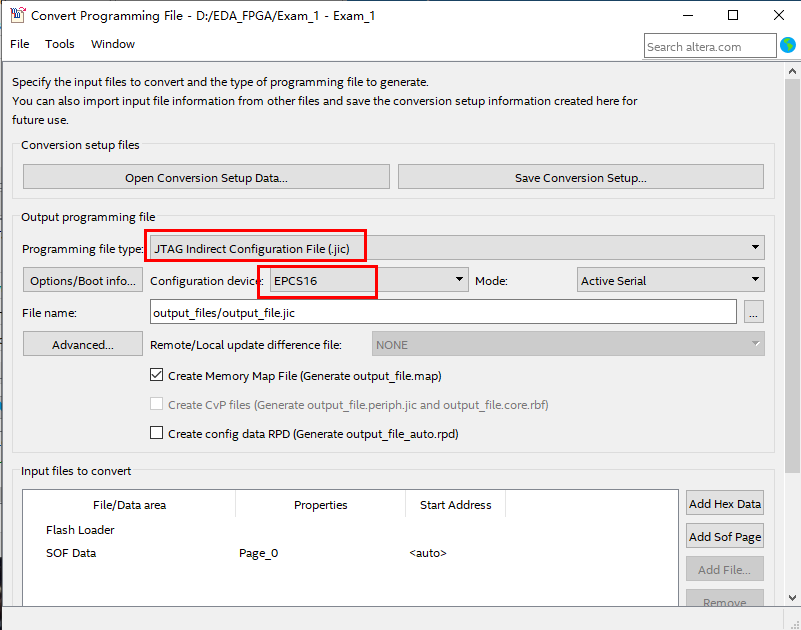

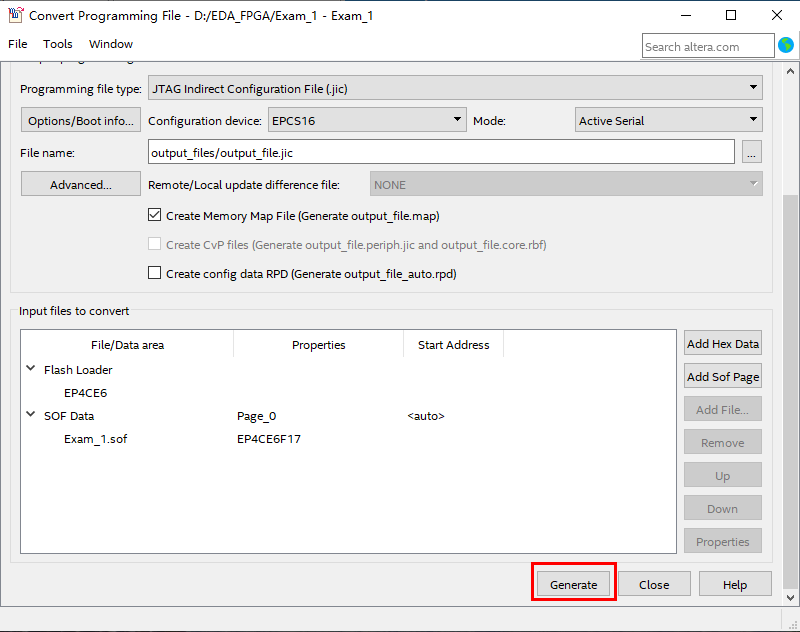

在打开的对话框中,先要选择好程序文件的类型及外部FLASH器件,点击Programming file type右边的下拉列表框,选择JTAG Indirect Configuration File(.jic)一项,点击Configuration device右边的下拉列表框,选择EPCS16一项,如下图所示。

接着点击下方的Flash Loader选中,然后再点击右边的Add Device按钮,如下图所示。

在打开的对话框中,左边勾选Cyclone IV E,右边勾选EP4CE6,如下图所示。完成后点击OK确定,关闭对话框。

接下来点击下方的SOF Data选中,然后点击右边的Add File按钮,如下图所示。

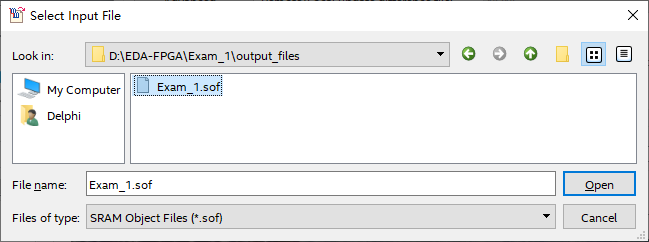

在打开的对话框中,定位到工程目录下,选择前面编译生成的文件Exam_1.sof(与工程同名),如下图所示。选中后点击Open按钮关闭对话框。

确认所选器件及转换文件都正确后,点击下方的Generate按钮,如下图所示。

转换成功后,会弹出下图的提示框,点击OK关闭。

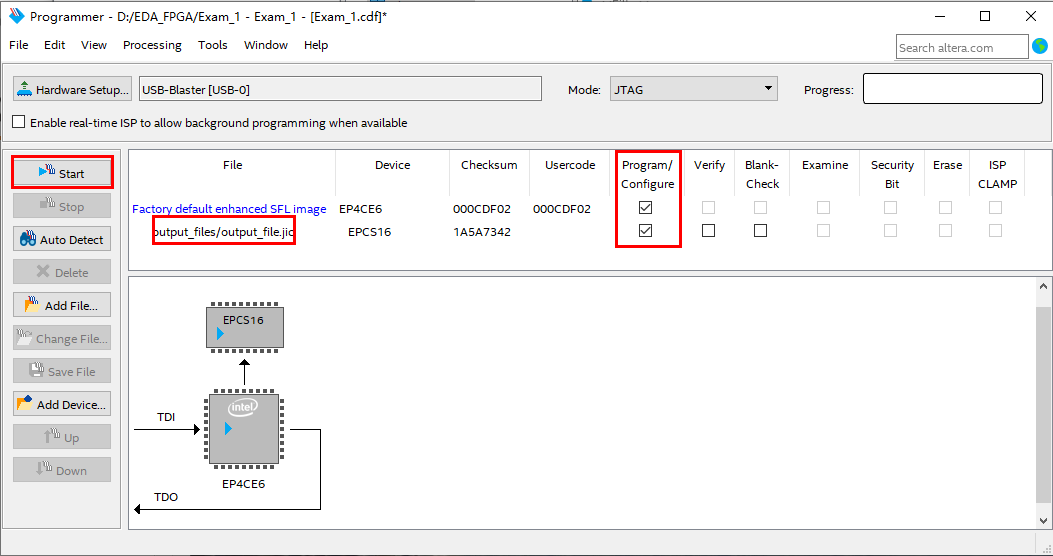

此时,在.sof所在目录下会生成一个同名的、以.jic为后缀的文件,该文件就可以写入到FLASH器件中了。再次点击工具条上的编程按钮(参见前面6),在打开的对话框中,先把前面的.sof文件删除(选中,点击Delete按钮),然后再导入.jic文件(点击Add File按钮,选中.jic文件并打开),检查一下打开的文件是否正确,并勾选Program/Configure,最后点击Start按钮把配置程序写入FLASH器件,如下图所示。

等待进度条为100%后同,表示写入成功。此时可把开发板断电,然后再上电,就可以看到程序已经在运行了。可再次执行第7步,验证结果是否正确。

9、清除FLASH中的固件

有时候希望把写入FLASH中的内容清除掉,可在编译对话框中,勾选Erase一项,并保证前面的Program/Configure同时勾选,然后点击Start按钮,当进度条到100%时,就把外部FLASH器件中的内容清空了。一般为了保险,在下载FLASH之前,都会先进行清空操作。

浙公网安备 33010602011771号

浙公网安备 33010602011771号