Crash Course CS 学习笔记 Class6-9

6.寄存器与内存(register&RAM)

如何存住一bit的信息

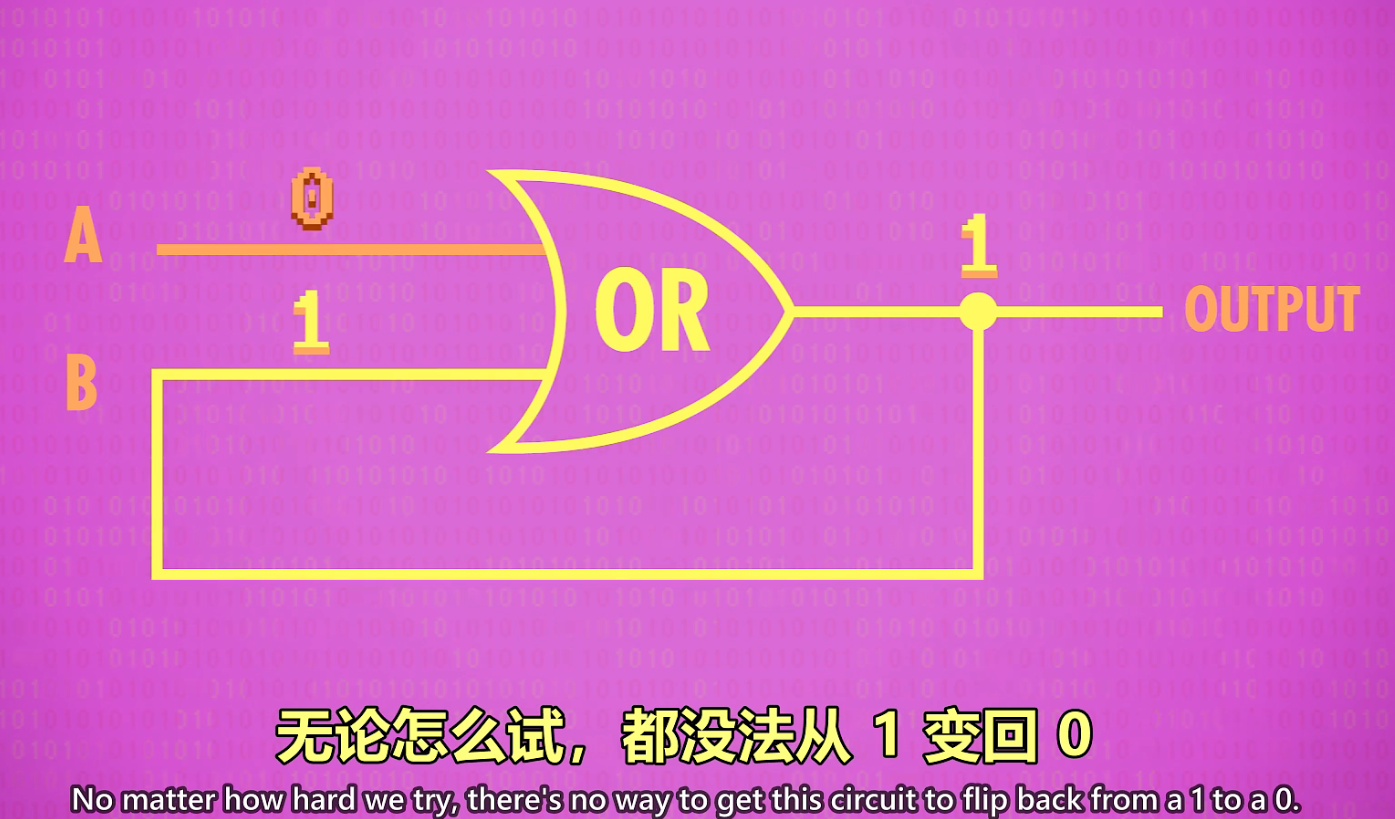

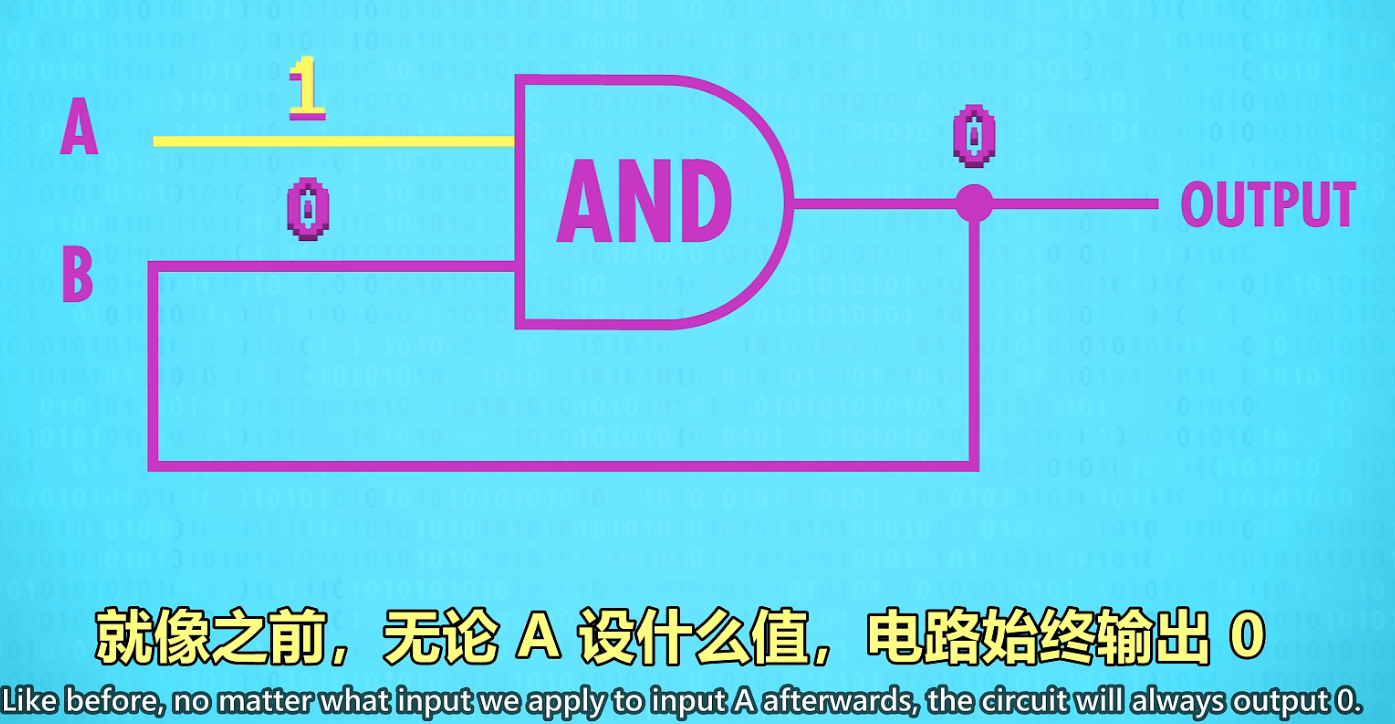

考虑将逻辑门的输出联回输入端,or门可以锁住1,and门可以锁住0(注意这里的大前提是电源联通,电源不联通不可能锁住1)

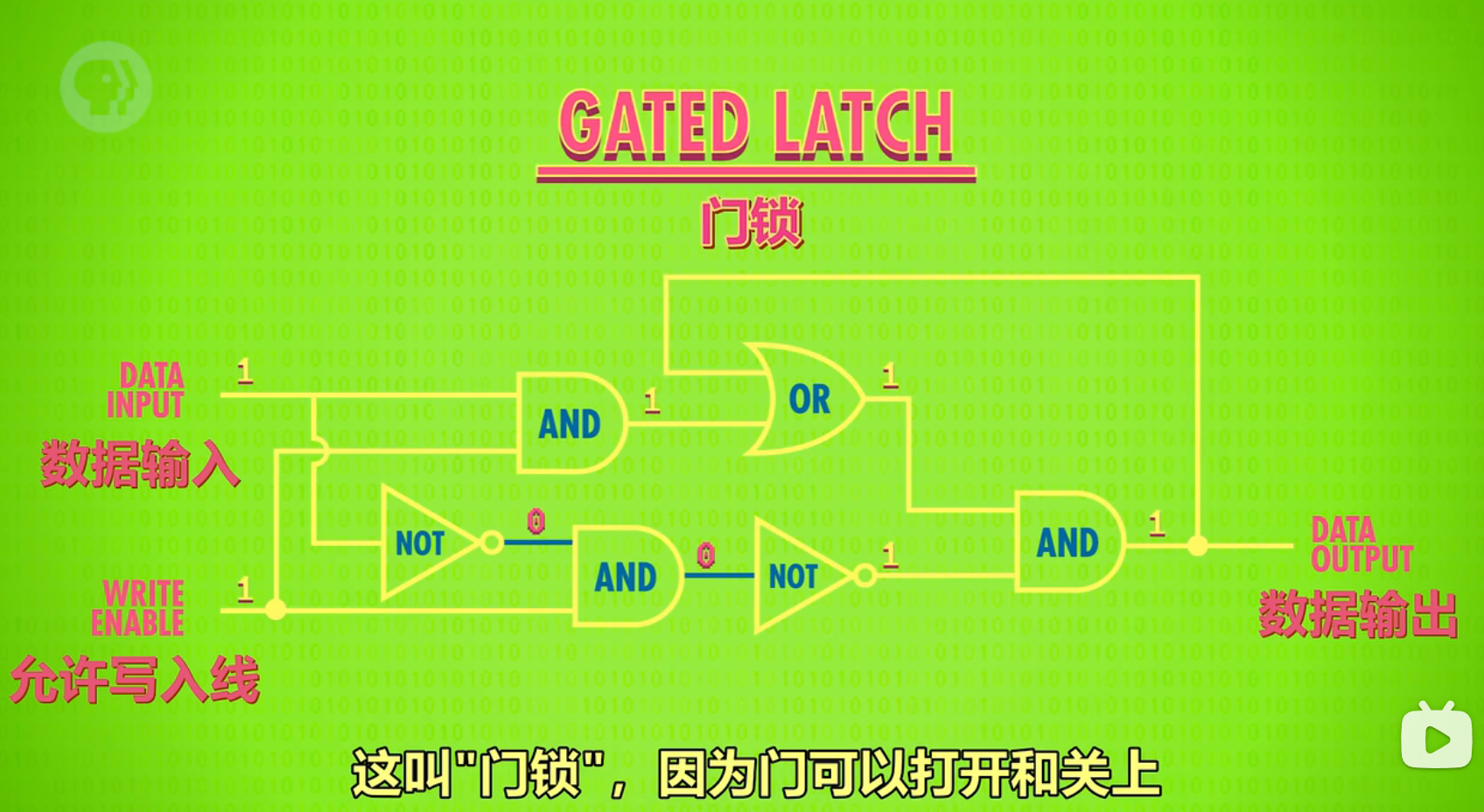

将两个门连接起来,得到锁存器

set与reset分别代表输入1,0,当set与reset均为0时,电路会一直输出锁住的值,实现保存1bit的信息

这个电路被称为锁存器,因为它能锁住1bit的信息,放入数据(set,reset)称为写入,输出数据(output)称为读取

设置和复位可通过一条线加NOT门实现,在此基础上增加一条线控制允许数据写入,实现门锁

将8个锁存器并排连接,可以实现存储8位数字,即8位寄存器(8 bits-register),8为位宽

16x16门锁矩阵

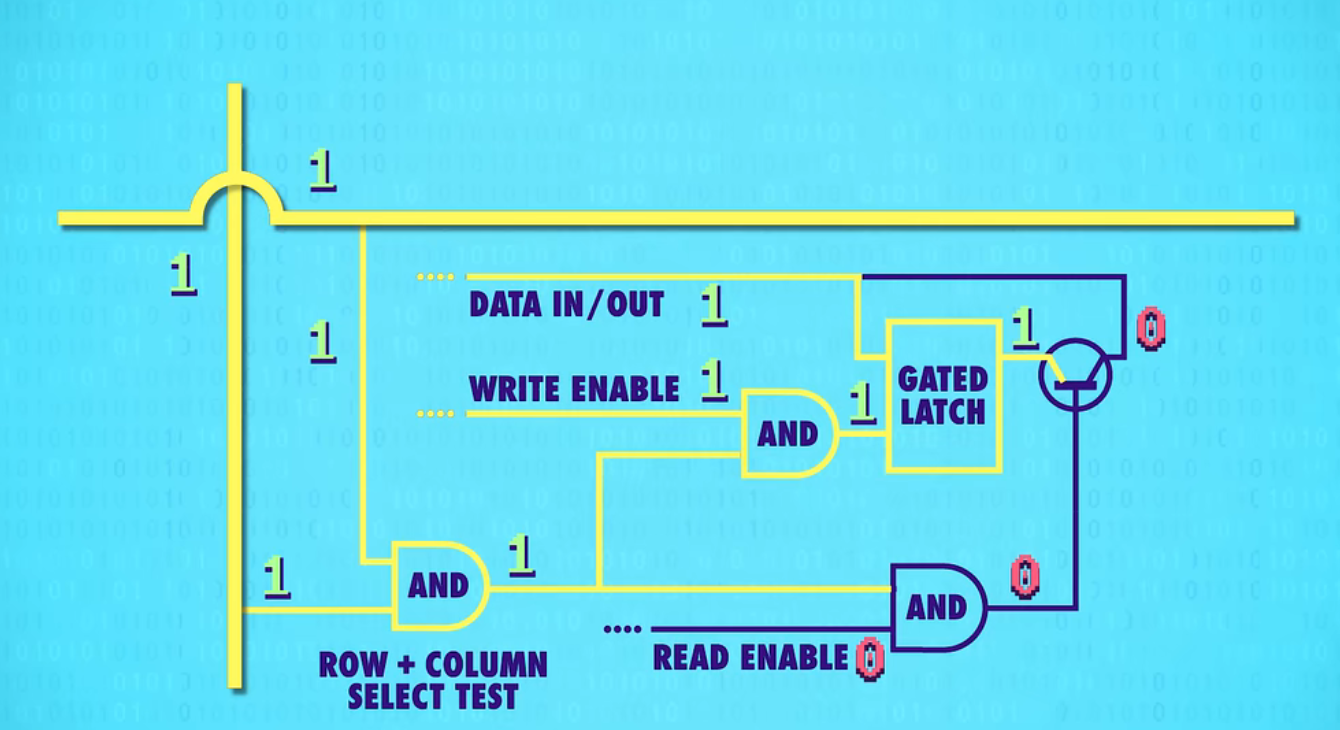

若通过并排连接的方式实现256个寄存器连接,需要线数过多,考虑以矩阵形式排列锁存器,每一行和每一列分别用一根线连接,形成16x16的锁存器网格

通过开启指定行与列的线,可以实现定向选择寄存器,并且因为其他寄存器不会被选择,所以允许写入线和写入,读取线可以共同一条,所需线为16+16+3=35根,大大减少线的数量

行数和列数转换为二进制后拼接在一起可以作为位置码,通过多路复用器对位置码进行解码即可进行指定寄存器

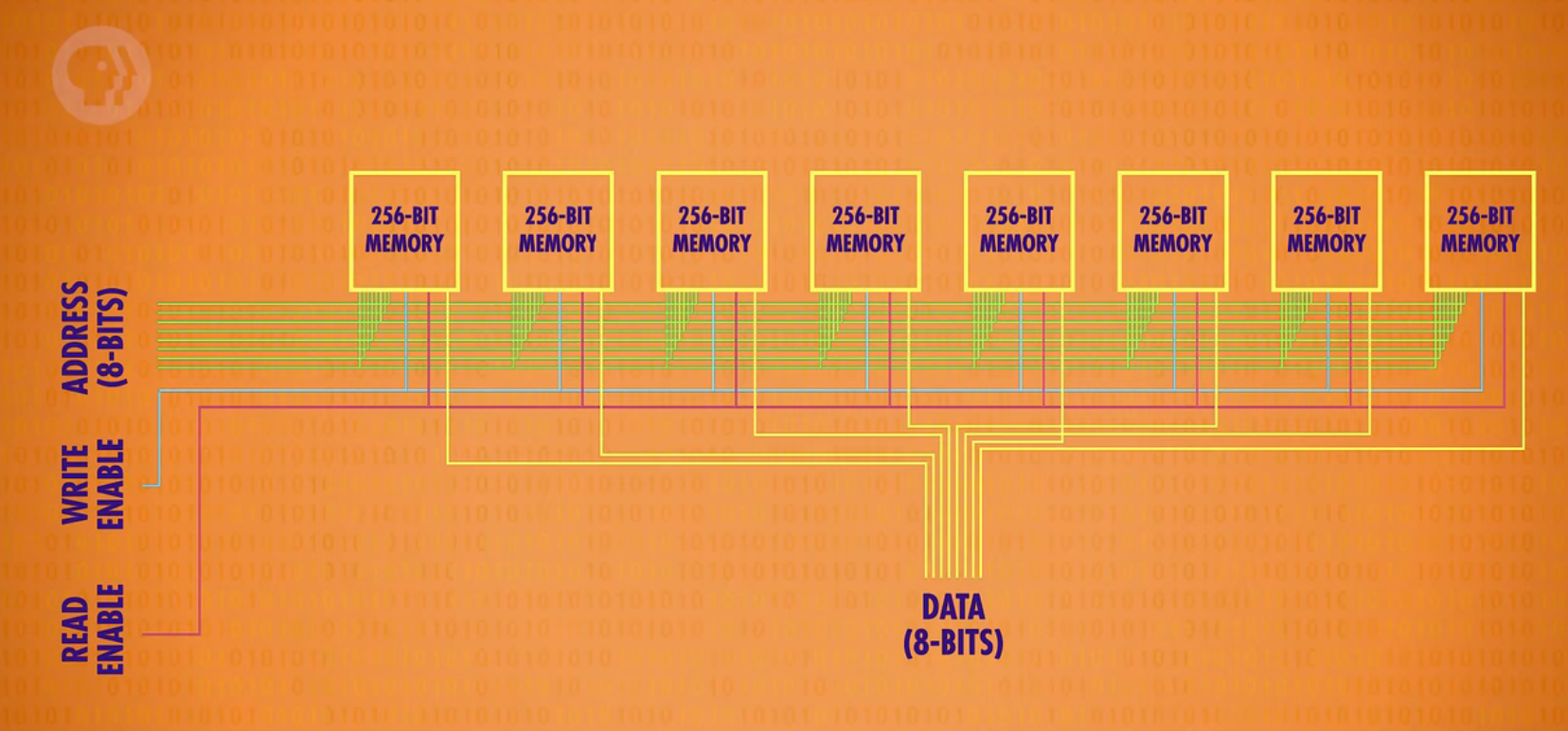

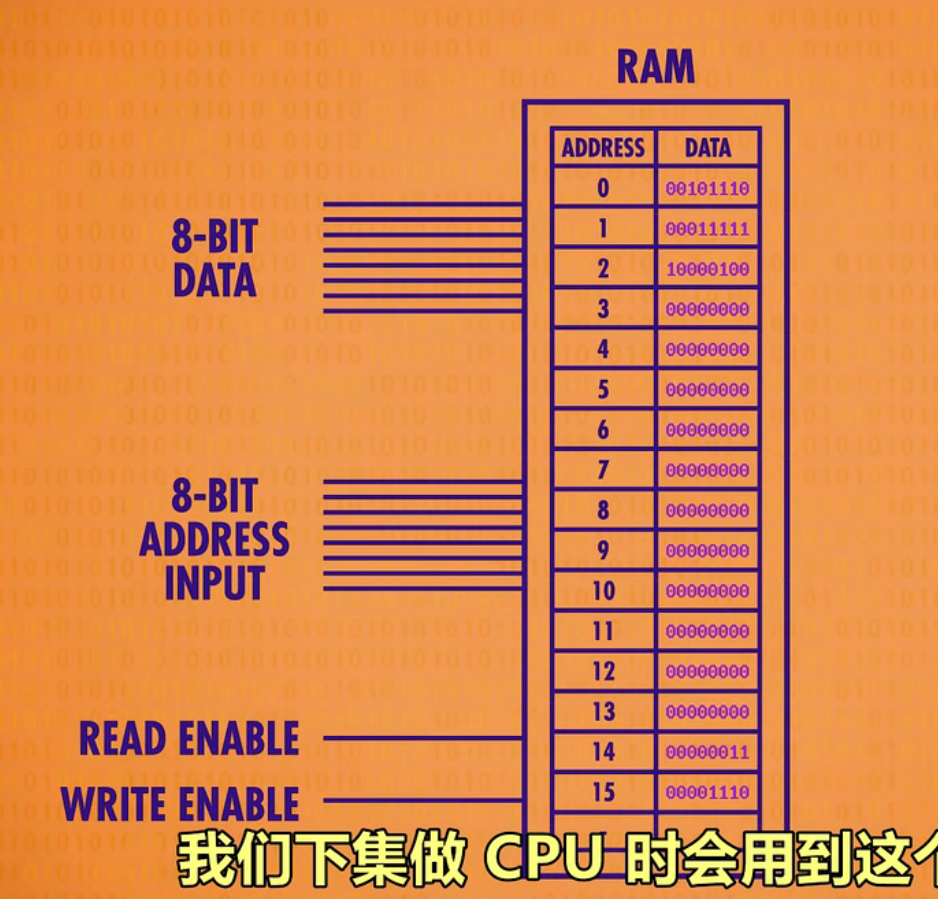

每一个256位内存只能根据地址码进行1位的存储,因此使用8个256位内存,给所有内存相同地址,将1个八位数的每一位分别存储在相应的256内存中,实现存储一个8位二进制数。

这里一共能够存储256个8位二进制数,即256bytes

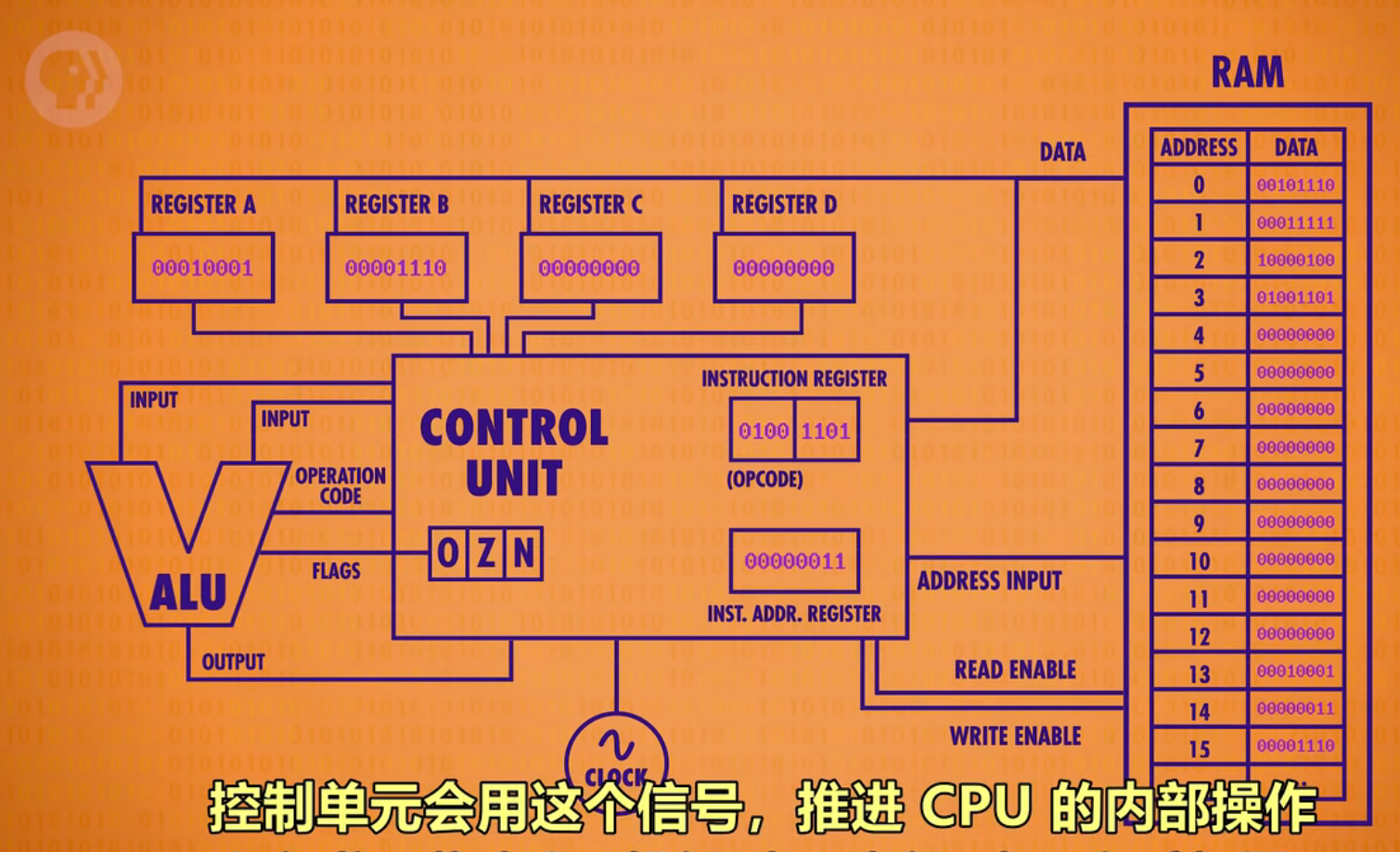

7.中央处理器(CPU)

cpu 的工作流程为取指-解码-执行

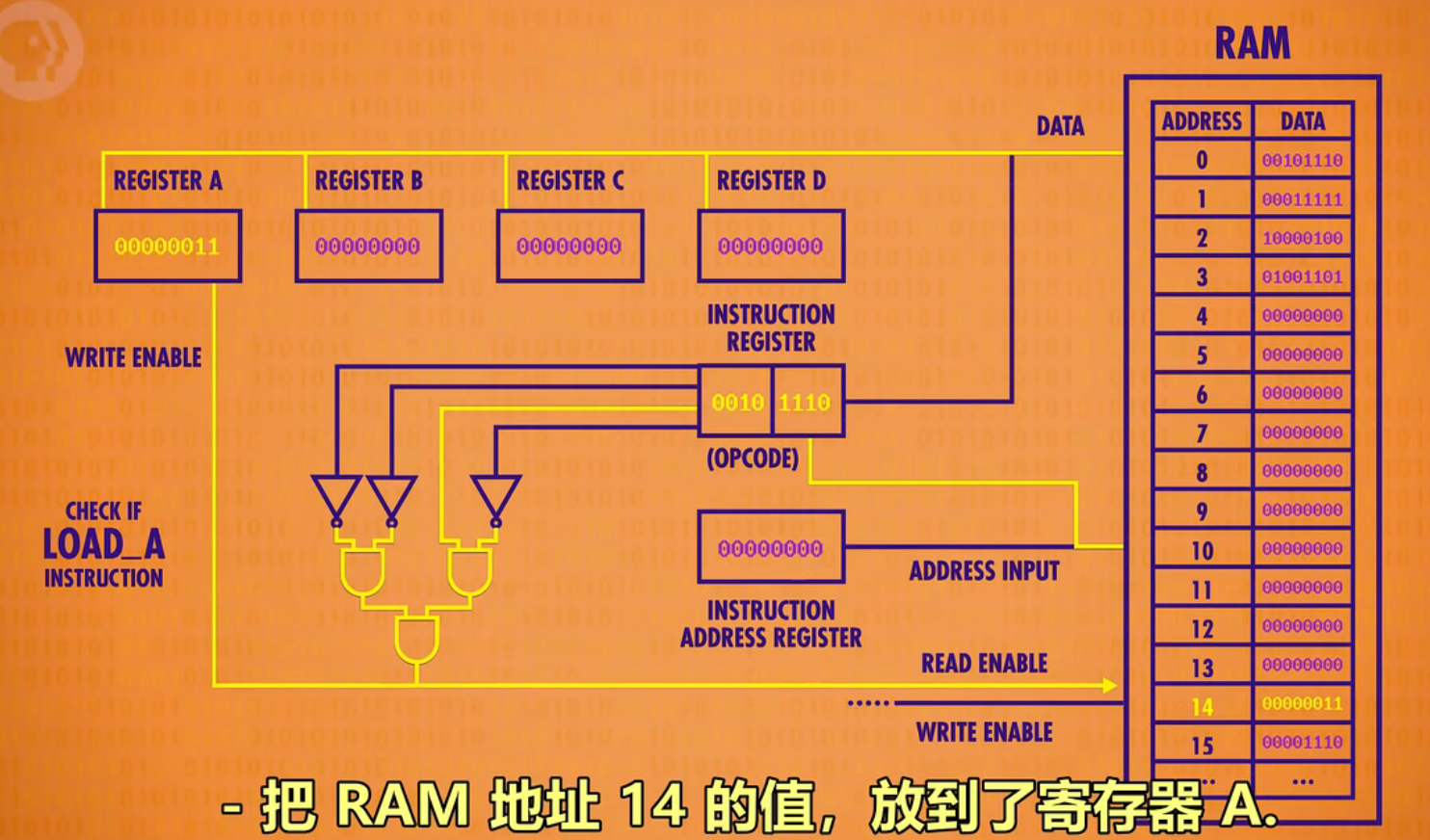

首先根据指令地址寄存器中保存的地址从内存中取出对应的指令(00000000->00101110),并保存到指令寄存器中 ->取指

然后将指令寄存器中的指令输入解码器进行解码,解码器位一系列逻辑电路构成,可以识别操作码

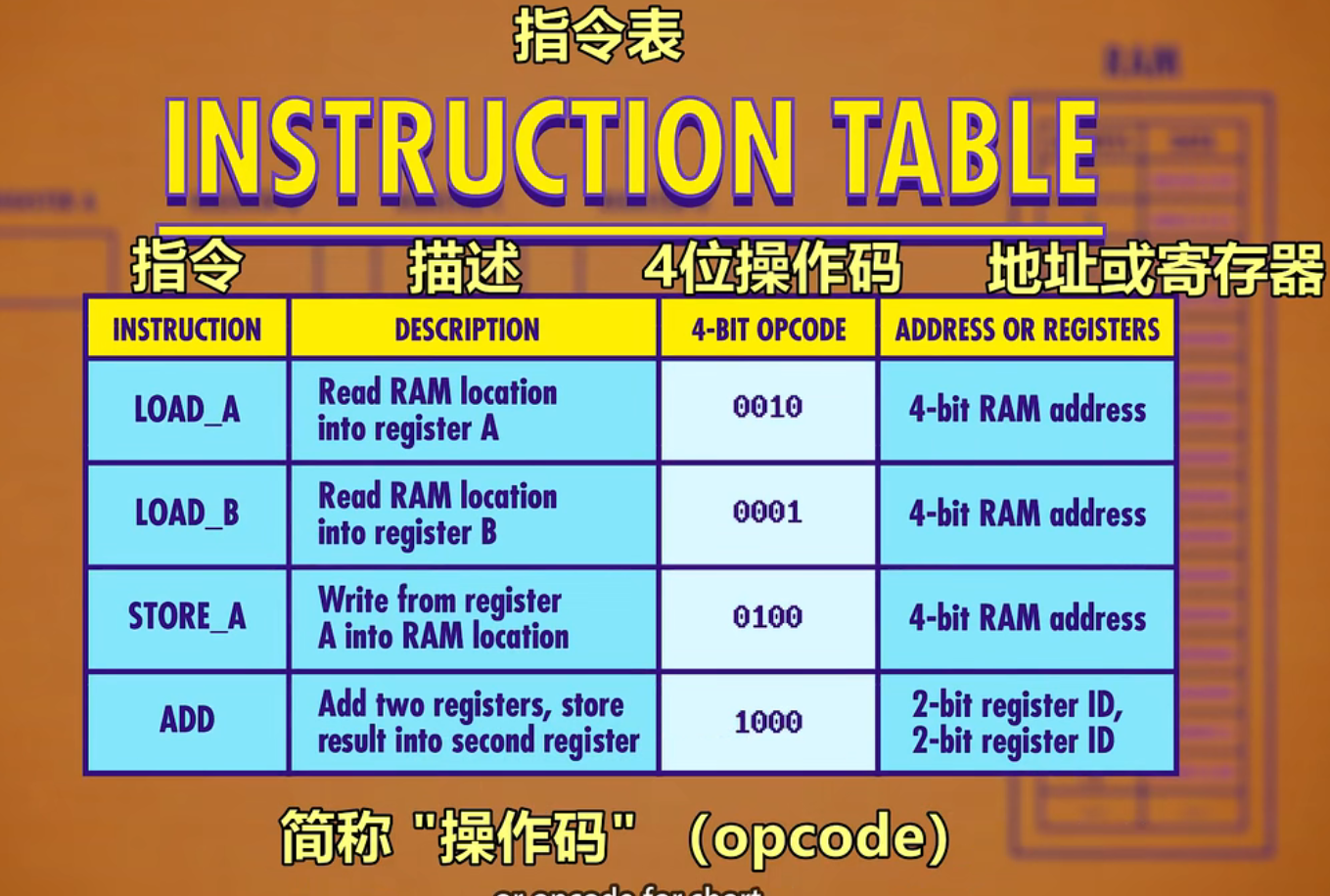

指令由8位数字构成,前四位为操作码,后四位为该操作涉及的数据在内存中的地址

例子中0010为将数据放入A寄存器,数据位于内存中14的位置,操作码输入逻辑电路,激活识别LOAD_A的电路->解码

LOAD_A激活内存的读取线,从内存14的位置读出数据00000011(3),并且也激活寄存器A的允许写入线,,将3写入寄存器A中。最后指令地址解码器中的地址+1->执行

将解码器,指令寄存器与指令地址寄存器整合位控制单元,控制单元是cpu的指挥中心

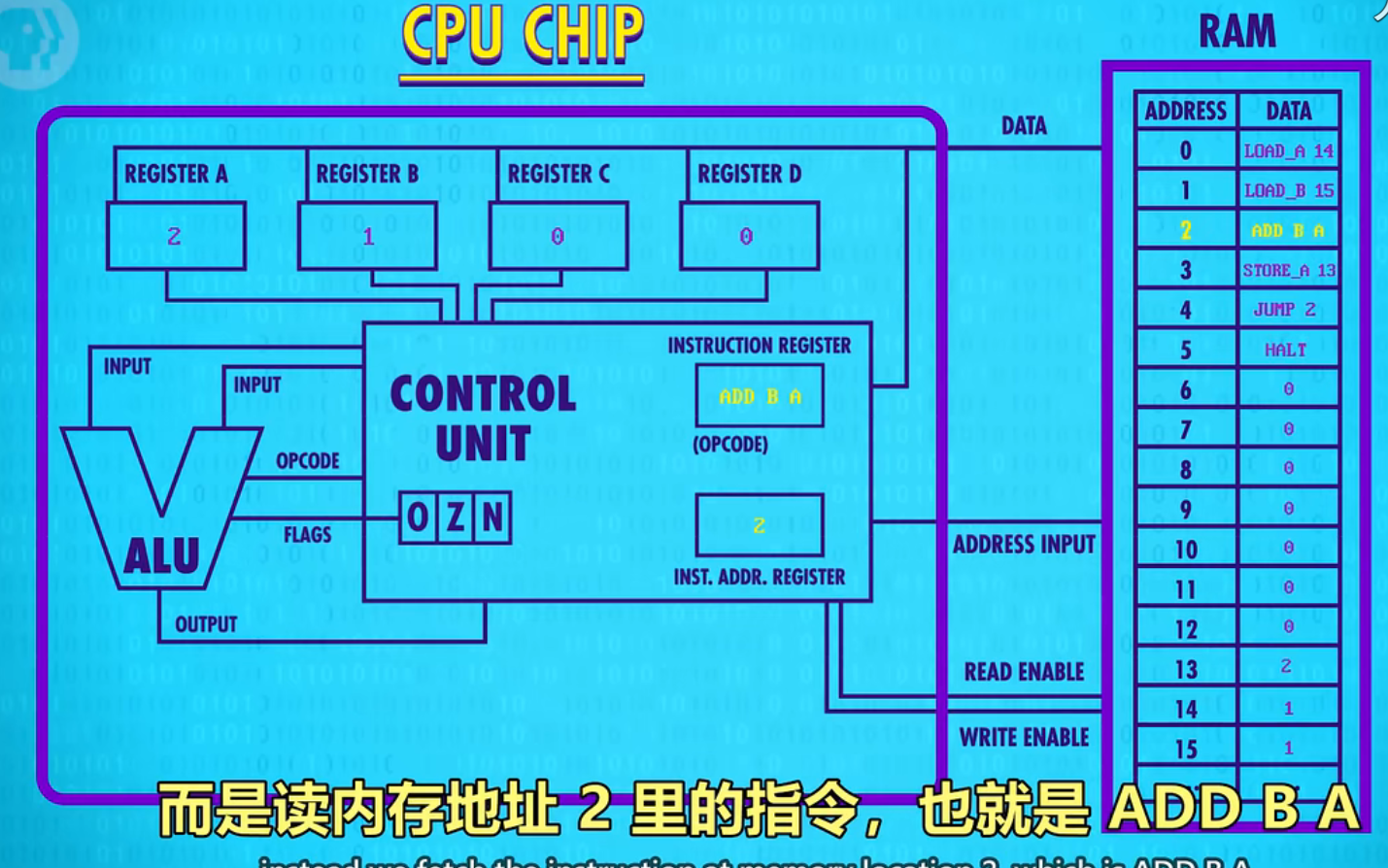

当执行到内存3的指令时,我们发现是add指令,将b+a的结果赋给a,这时要将ALU连入电路

取指,解码后,控制单元启用寄存器B作为ALU的第一个输入,启用寄存器A作为ALU的第二个输入,ALU计算a+b的值后,将值输入控制单元,再由控制单元将值写入寄存器A中,实现add

在cpu中,通过时钟控制步骤的进行,取指->解码->执行所需的时间被称为时钟速度。提高时钟速度称为超频,降低时钟速度称为降频

8.指令与程序

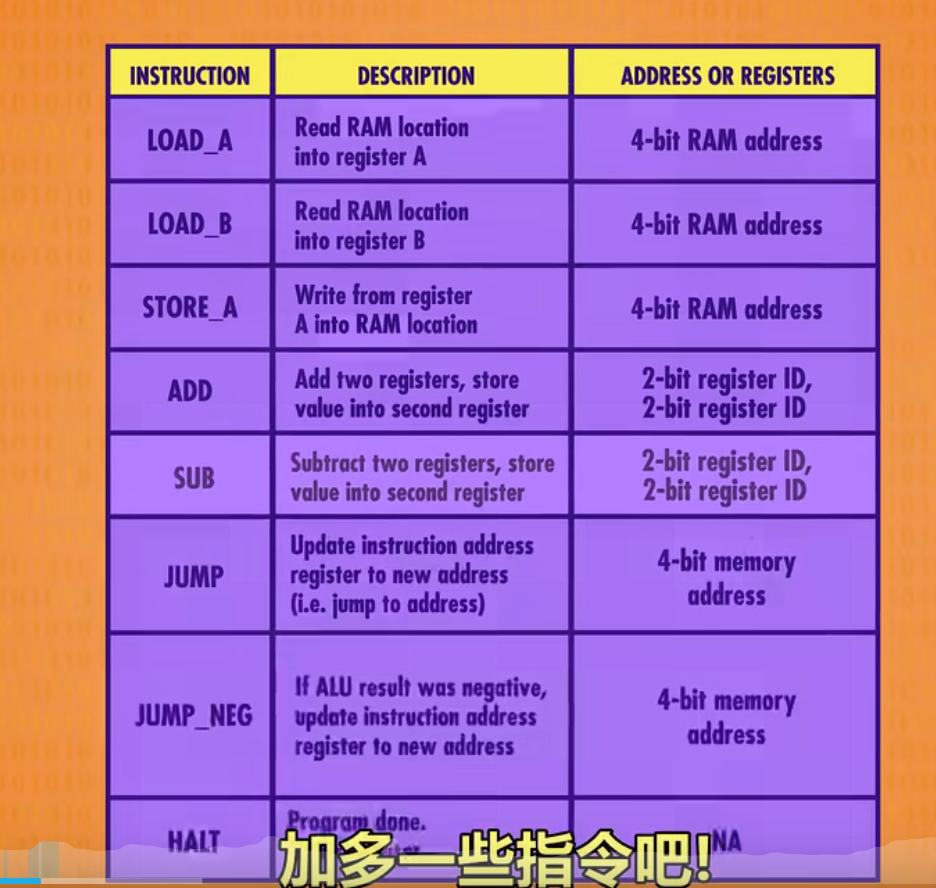

LOAD_A 将数据保存在A寄存器中

LOAD_B 将数据保存在B寄存器中

ADD B A 计算A+B的值并将值保存到A寄存器中

STORE_A 将A寄存器的数据写入内存

SUB B A 计算A-B的值并将值保存到A寄存器中

JUMP 跳转至另一指令

JUMP_NEG 若结果ALU输出负数标志则跳转至另一指令

HALT 停止运行

实现JUMP跳转指令的方式是将指令后四位写入指令地址寄存器,例子中的JUMP会永远跳回ADD指令,出现死循环

加入JUMP_NEG后,当程序执行到第二次时,ALU做1-5=-4,此时输出负数指令,激活下一条命令JUMP_NEG,从而跳出循环。图中的程序实现了取余

实际中指令所对应的地址不止是4位,一种是增加指令长度,让指令本身加长,另一种是可变指令长度,指令后对应的地址存放的不再是数据的地址,而是存放 数据的地址 的地址(立即值),甚至可以一直访问下去以获取任意地址长度,但是这样会使寻址变得麻烦

9.高级CPU设计

(1)在硬件层面设计指令取代程序计算(例如除法)

SSE等指令集

(2)为CPU增加缓存(cache)

RAM在CPU的外部,从RAM中读取数据要消耗非常多的时钟周期,因此在CPU内部增加了缓存

每次从RAM中读取一批指令到缓存中,CPU从缓存中读取指令的速度非常快,从而提高运行速度

当缓存满了而又要读新指令时,系统会对比缓存与RAM中的数据是否一致,若不一致则将指令记入脏位中,等待同步写入RAM中

(3)指令流水线与并行编程

并行需要考虑数据冲突与指令依赖,在现代CPU中有较为成熟的分支预测系统

(4)超标量处理器

利用其他空闲电路同时进行操作

(5)多核处理器