1.硬件电路

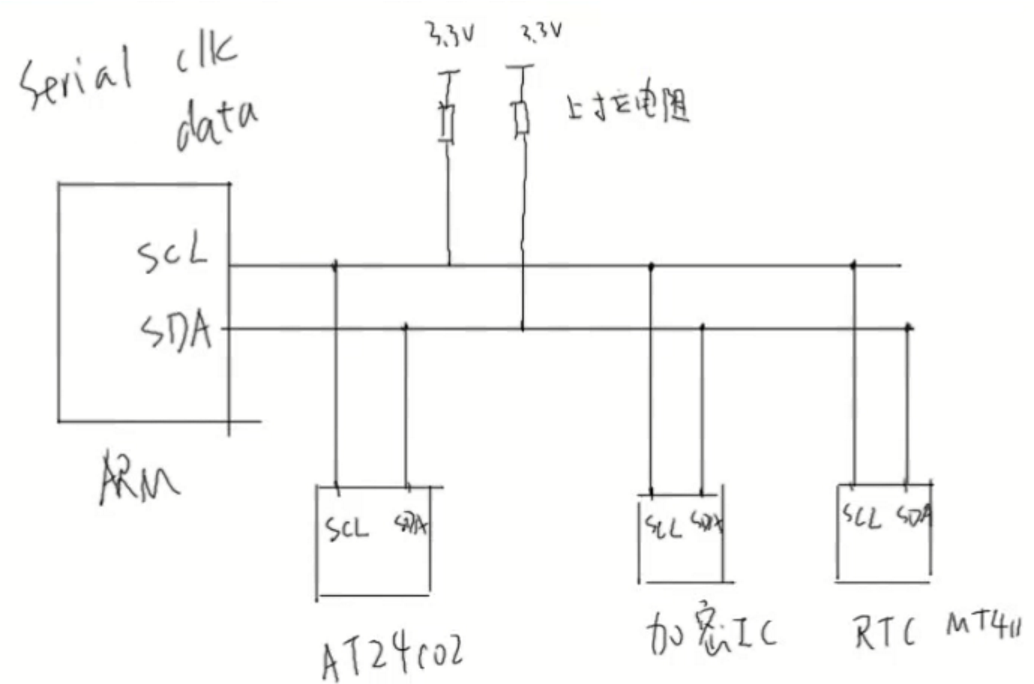

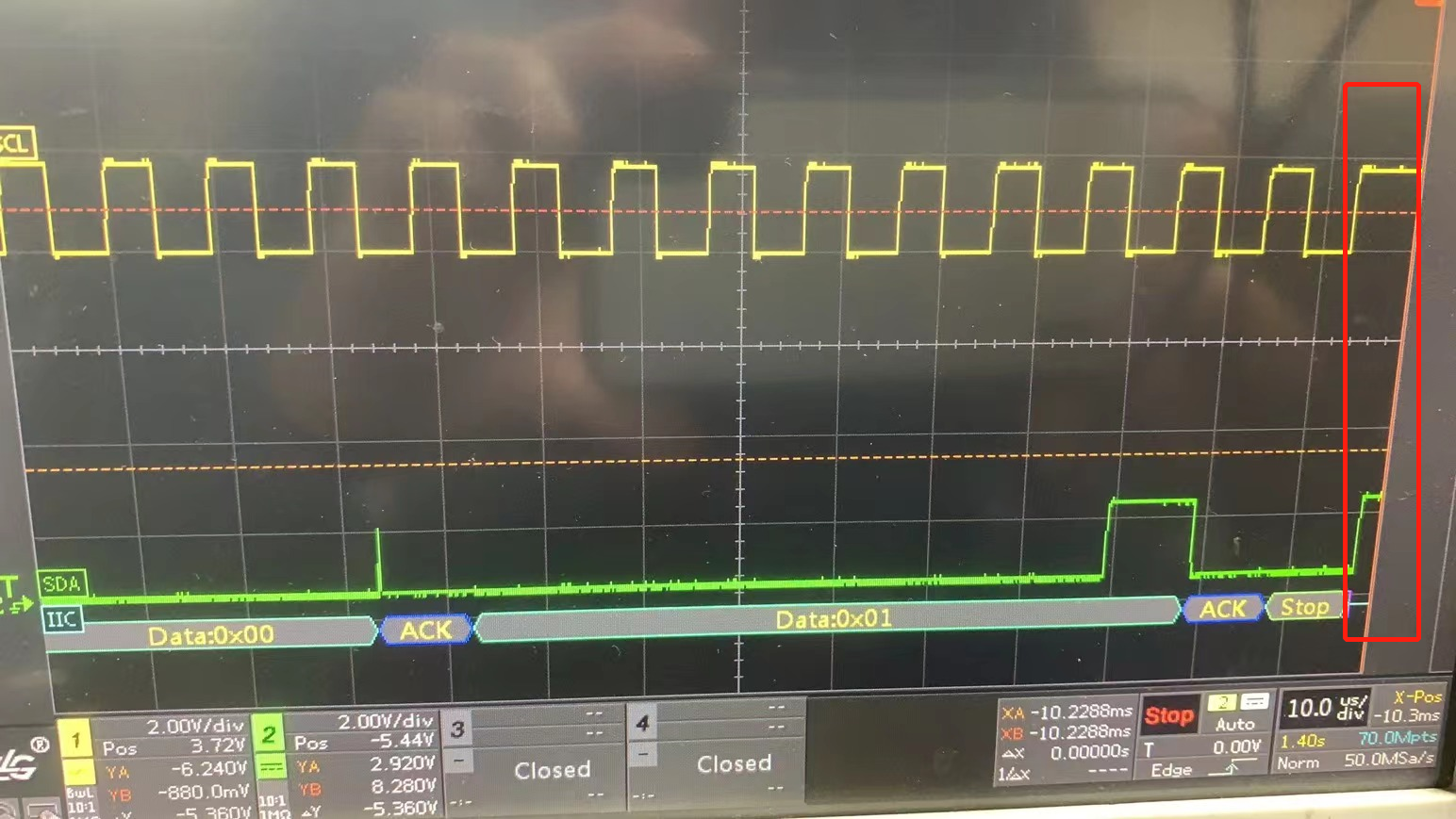

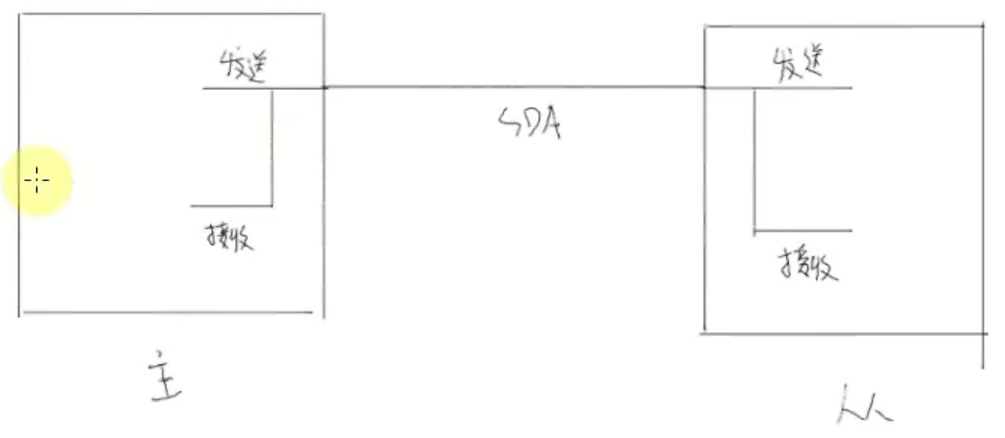

I2C总线是由Philips公司开发的一种简单、双向二线制同步串行总线。如下图:

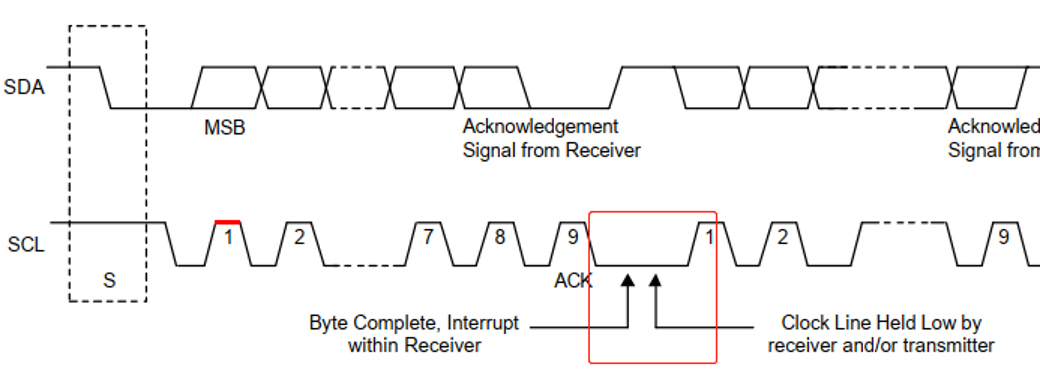

SDA(串行数据线)和SCL(串行时钟线)都是双向I/O线,需通过上拉电阻接电源VCC.当总线空闲时.两根线都是高电平。

2.i2c协议规则

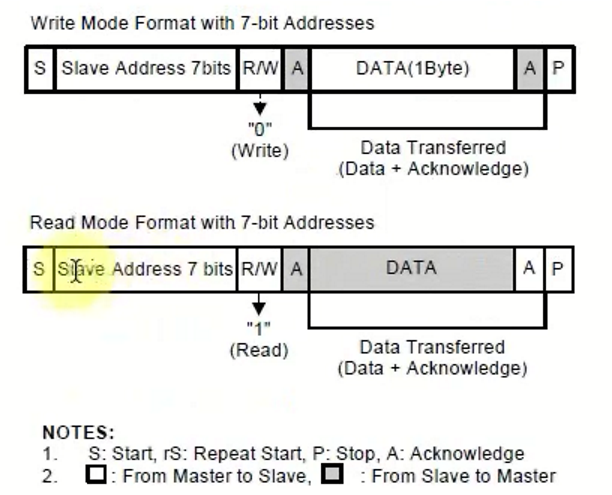

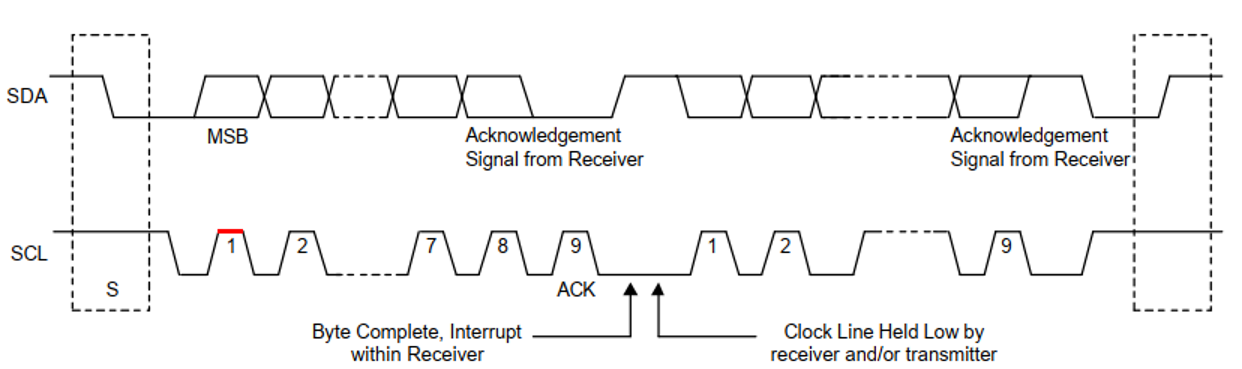

传输过程如下:

主控发送start讯号(S)

主控发送从设备地址(slave dev addr)

主控发送方向(W/R)

从设备应答(ack)

主控(or从设备)发送数据(data)

从设备(or主控)应答(ack)

…

主控发送停止讯号(P)

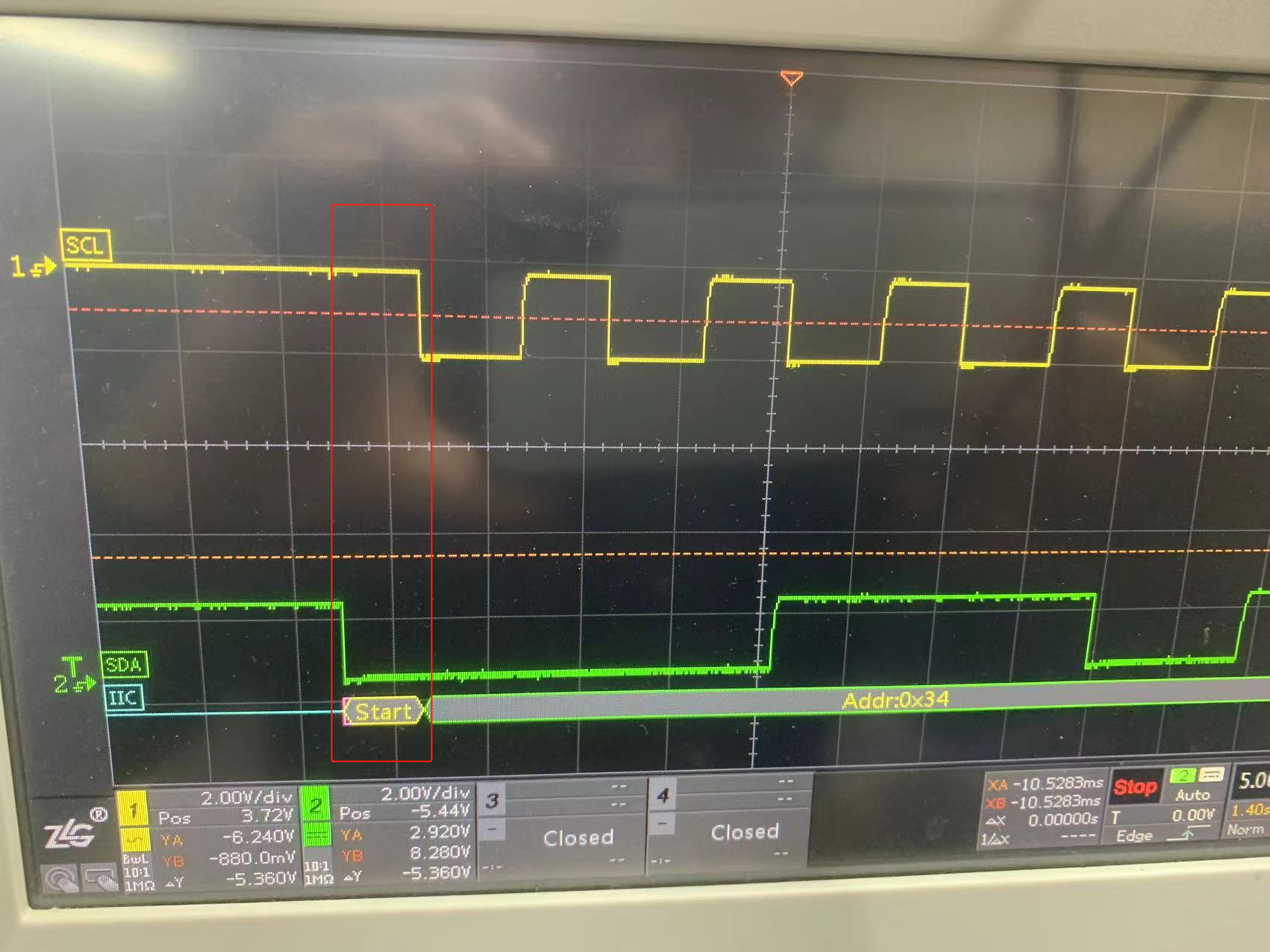

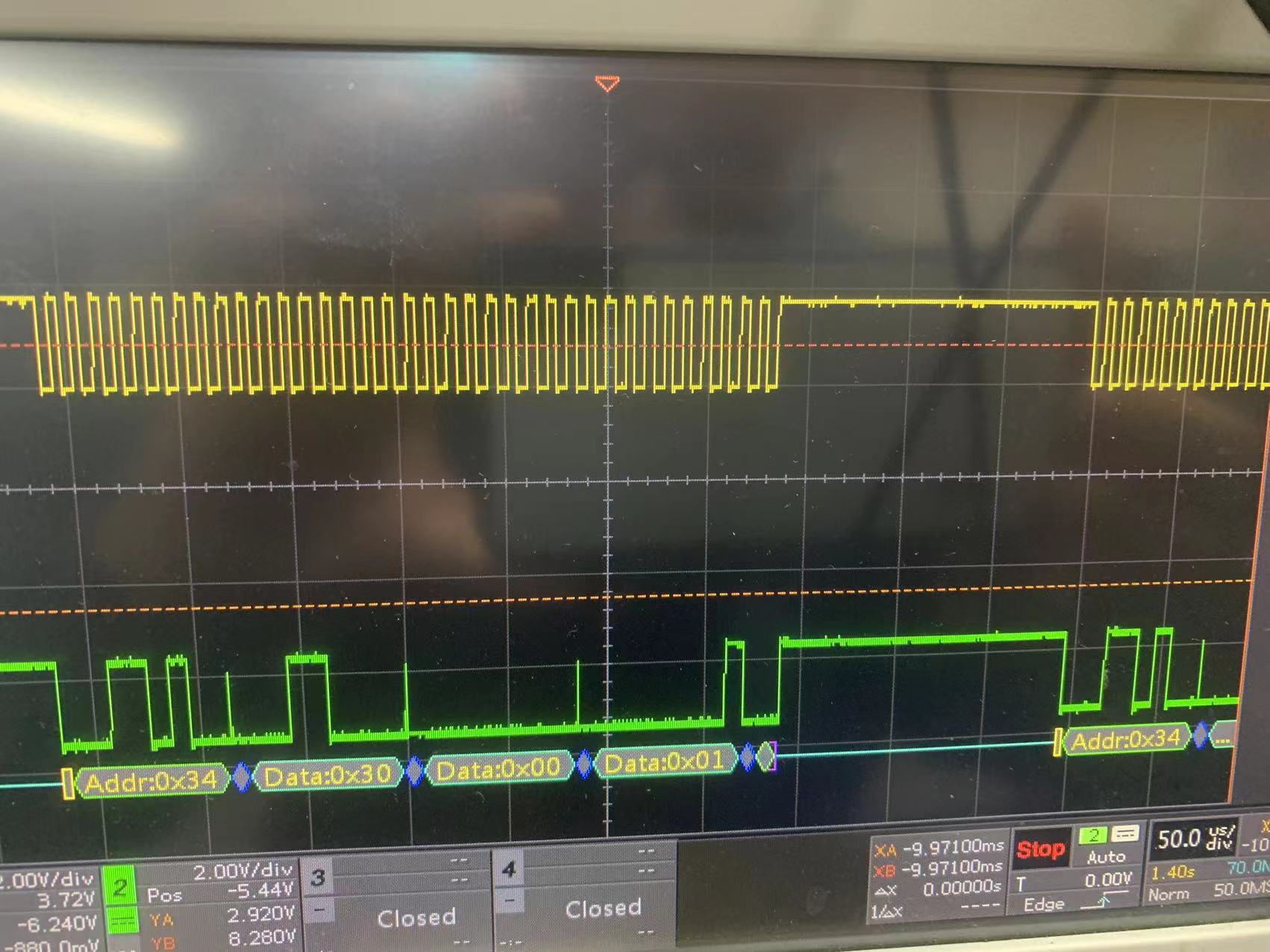

下图是具体的s3c2440 一次i2c读写过程:

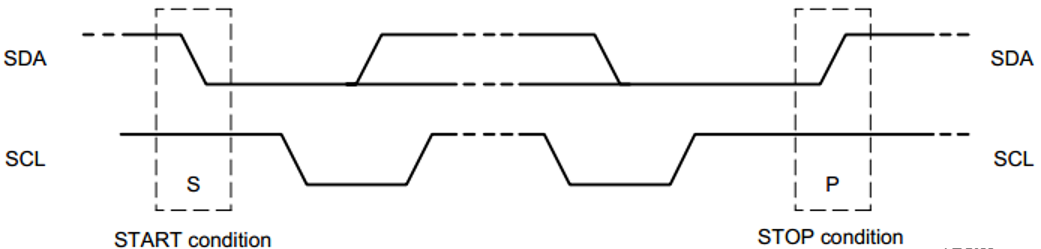

2.1 start & stop讯号

start信号:SCL是高电平,SDA被主控拉低

stop信号:SCL是高电平,SDA被主控拉高

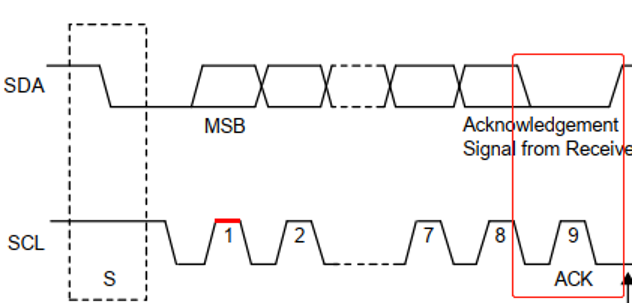

2.2 ack讯号

第9个时钟周期,SDA被拉低表示ack讯号

2.3 DATA格式

用 9个clk传输8bit数据(7bit 从设备地址 + 1bit方向 ),MSB高位先出。第9个clk是ack讯号。

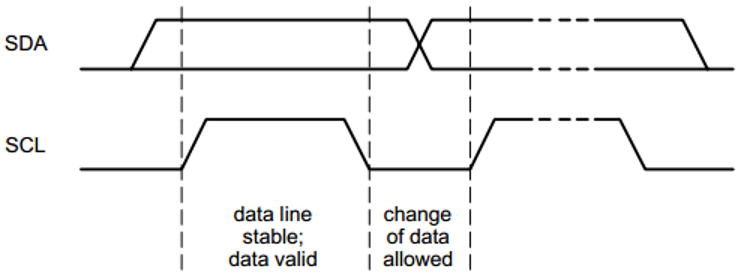

2.4 数据有效性

SDA 线上的数据必须在SCL高电平周期保持稳定,在 SCL 低电平时才能允许改变。

换言之,SCL为高电平时表示有效数据,SDA为高电平表示“1”,低电平表示“0”;SCL为低电平时表示无效数据,此时SDA会进行电平切换,为下次数据表示做准备。

2.5一次数据传输

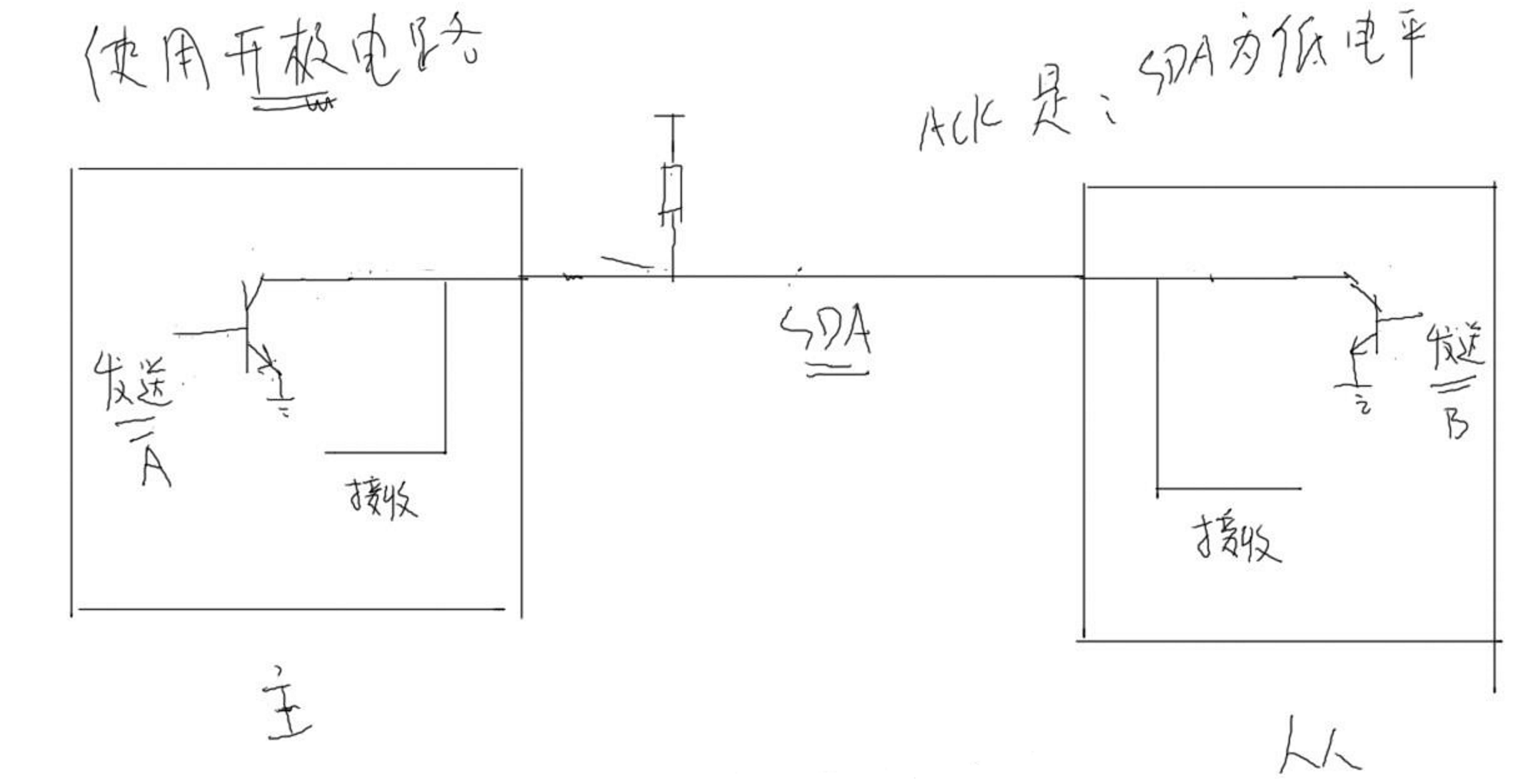

2.6 一条SDA上实现双向传输的原理(开极电路)

条件:

1.主设备发送时,从设备不发送(通过SCL控制即可,比如让前8个clk主控发送数据到SDA,让第9个clk从设备发送数据到SDA)

2.主设备发送数据时,从设备的“发送引脚”不能影响SDA数据。反之,从设备发送数据时,主设备的"发送引脚"不能影响到SDA数据。那么如何做到?(SDA内部电路用三极管,开集电路)

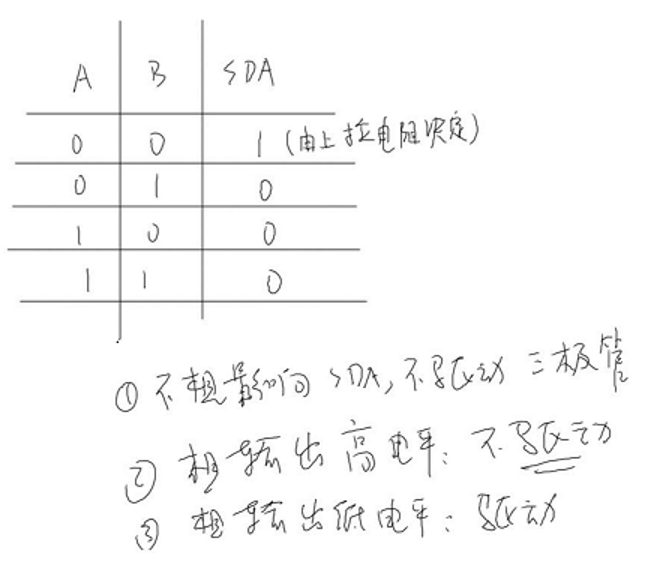

从上图得出当A,B都为低电平时,三极管不导通,SDA的电平取决于外部电路,这里SDA有上拉电阻,所以对应高电平

当主控拉高A时,三极管导通,此时SDA接地,电平被拉低

同理,当从设备拉高B时,三极管导通,此时SDA接地,电平被拉低

那么电平真值表如下:

所以,实现双向传输时:

如果是master-> slave进行数据传输,那么让主控驱动三极管,拉低SDA。

如果是slave-> master进行数据传输,那么让从设备驱动三极管,拉低SDA。

否则,都不驱动三极管,SDA一直输出高电平,处于idle状态

2.6 SCL被从设备拉低表示busy状态

在第9个clk 后i2c会产生中断,此时SCL被拉低,表示busy状态,表示谁都不允许再使用i2c, 然后等到中断处理结束了,也就是处于idle状态了,此时会释放出SCL,那么主控可以继续发送SCL讯号表示可以继续进行i2c通信了。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 如何调用 DeepSeek 的自然语言处理 API 接口并集成到在线客服系统

· 【译】Visual Studio 中新的强大生产力特性

· 2025年我用 Compose 写了一个 Todo App