又看到一本好书

当wire[3:0] a;时,assign y = | a; 和 assign y = a[3] | a[2] | a[1] | a[0]; 一样。这个叫reduction, python里有reduce和map函数。不精确地说,map对数组里的每个元素执行操作,n进n出;reduce也对每个元素执行操作,n进1出,再如求sum。reduction在一定程度上可代替循环,MIT 6.111上的例子可能也好久没更新了。

The data types in the variable group represent abstract storage in behavioral modeling and are used in the outputs of procedural assignments. There are five data types in this group: reg, integer, real, time, and realtime. The most commonly used data type in this group is reg and it can be synthesized. The inferred circuit may or may not contain physical storage components. The last three data types can only be used in modeling and simulation. In Verilog-1995, the variable group is known as the register group. Since this term is the same for a physical hardware register (i.e., a collection of flip-flops), it is changed in the Verilog-2001 documentation to avoid confusion.

In Verilog-1995, port names, modes, and data types are declared separately.

eq1 eq_bit0_unit(.i0(a[0]), .i1(b[0]), .eq(e0)); 比eq1 eq_bit0_unit(a[0]), b[0]), e0); 更代码清晰和不容易出错: 比如eq1改了port的顺序。

像python里的命名参数,eq1 eq_bit0_unit(i0=a[0], i1=b[0], eq=e0); 不好么?

Objective-C里 [self panLatitude:x longitude:y]; 方头方脑的芯片为啥不多用[]? :-) [-]都不用按Shift键。[nand a-x y-b]

assign eq = p0 | p1; The new value is assigned to eq after the propagation delay. In a nonblocking assignment, the evaluated expression is assigned at the end of the always block. According to the Verilog standard, the execution of two always blocks can be scheduled in any order.

timescale 1 ns/10 ps 然后每次 # 200; 为啥不timesacle 200ns? 哦,FPGA开发板上的时钟好像频率是有限的。

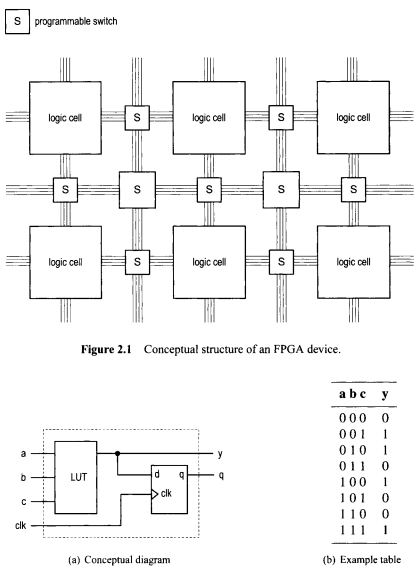

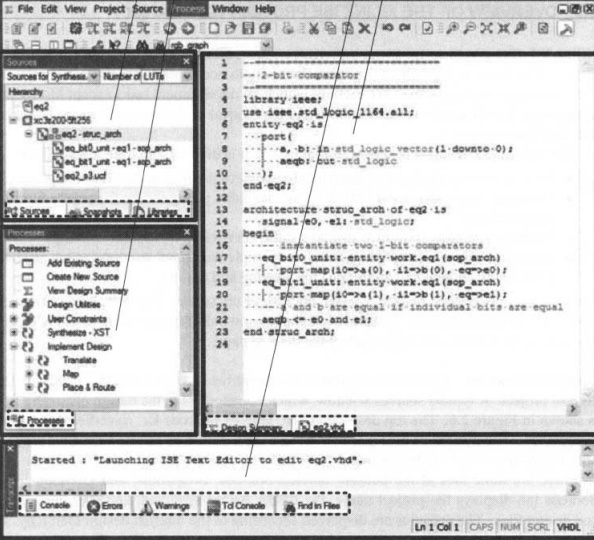

我去,真用了Look-Up-Table,还带锁存功能!为自己的直觉点个赞。:-) VHDL里好像用=>来接线:

不知道有没有Class Wizard和代码重构。例如可以看到每个module/entity的ports (class的property),当某个module的某些port改了名字后,在菜单里选refactor,自动找到所有用了那些port的地方做相应修改。IntelliJ的IDEA好像可以对Java程序这么干。

wire [7:0] a, b; assign a = 8'b00000000; assign b = 0;

The first statement assigns an 8-bit value. "00000000", to a. The second statement assigns the integer 0 to b. Recall that the integer in Verilog is 32 bits and thus 0 is represented as "00000000000000000000000000000000". Since b is 8 bits wide, it is truncated to "00000000" during the assignment.

3'b000写成'b000是可以的。32x0不好吗?也许可以语法高亮在遇到0110111100这样的二进制数时,0用绿色1用红色,或字体大小粗细不一样。有的语言允许二进制数中间有空格或-。鼠标指针停留自动显示总共多少位(和对应的16进制或8进制数)。编译时遇到截断或扩展给出警告。

浙公网安备 33010602011771号

浙公网安备 33010602011771号