Verilog code for D flip-flop – All modeling styles

我这个第一个对,第二个不对:

module flipflop(output q, q_, input set, enable, reset); wire er, es; and g1(er, enable, reset), g2(es, enable, set); nor g3(q, er, q_), g4(q_, es, q); endmodule module ff2(output reg q, q_, input set, enable, reset); always @(enable)begin

q <= ~((enable & reset) | q_); q_ <= ~((enable & set) | q); end endmodule module test; wire q, q_; reg enable, set, reset; initial begin $monitor("enable=%b set=%b reset=%b q=%b q_=%b ", enable, set, reset, q, q_); set = 1; reset = 0; #1 enable = 1; #1 enable = 0; #1 set = 0; reset = 1; #1 enable = 1; #1 $finish; end //flipflop ff(q, q_, set, enable, reset); ff2 ff2(q, q_, set, enable, reset); endmodule

看别人的吧: Verilog code for D flip-flop - All modeling styles (technobyte.org) Verilog: T flip flop using dataflow model - Stack Overflow

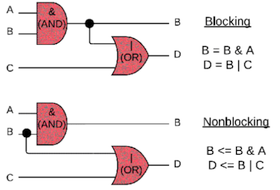

我倾向于认为Verilog的<=没那么强; 它可以偷偷地把 q <= ~((enable & reset) | q_); 换成if嘛。

1. 叫modeling style不叫coding style.

2. if (!condition) is bad coding style. if (condition)较好,把if里的和else里的对调一下。

惭愧,资料下了没细看就急着喷:

wire A_in, B_in, C_in; reg A_out, B_out, C_out; A_out <= A_in; B_out <= A_out + 1; C_out <= B_out + 1; 或 A_out <= A_in; B_out <= B_in; // 可这不是白干了吗? C_out <= C_in; assign B_in = A_out + 1; assign C_in = B_out + 1 * Verilog里把位运算叫reduction. ~|是操作符。a ~| b即可,用不着~(a | b). fork和join合成不了。

* Verilog PLI (Programming Language Interface) is a mechanism to invoke C/C++ functions from Verilog code.

*** Verilog 2001里@里的变量用,分隔即可,不用写or. always @*,不用@(*). 哎,换@*或@(*)后好像对了: ***

module ff2(output reg q, q_, input set, enable, reset);

always @* begin

q <= (enable & reset) ~| q_;

q_ <= (enable & set) ~| q;

end endmodule

* Verilog有$fopen,要是能打开named pipe就好了。父进程可以dup2,与进程通过stdin/stdout通信,如象棋的引擎。

* 好吧,我承认Verilog比python难学,从晶体管到文件的大烩菜。C++有template, Verilog有parameter.

* SystemVerilog是Verilog 2001的扩展和增强,它把硬件描述语言和高层级验证语言(HVL)结合了起来。

这个帖子是以前写的。看了一点书后感受如下:1. 先多看点书再喷。:-) 2. @*不是好像对而是对。<= 是某个时候才执行的操作,@* 要求在q和q_变化时再次执行,也许q变执行下,q_变再执行下。3. 要看好书; 4. 个别书不知道是写书的不太会呢,还是不想多说…… 好像和1)冲突了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号