Icarus windows版及源码博客园下载

https://files.cnblogs.com/files/blogs/714801/iverilog-12.0-windows.7z

5,536KB 不带GTKWave. 玩玩在console看01就行。还有$dumpvars和$monitor呢。

Icarus Verilog is available in official MSYS2 repositories and mirrors: https://packages.msys2.org/search?t=pkg&q=iverilog

First, search the available package versions: pacman -Ss iverilog

Then, install the package for MINGW64 and/or MINGW32: pacman -S mingw-w64-x86_64-iverilog mingw-w64-i686-iverilog

https://files.cnblogs.com/files/blogs/714801/verilog-11.0.tar.gz

1,743KB 近7万行C++ Linux下编译应该不难,configure再make. byte code而不是汇编,LLVM JIT? :-)

Logic synthesis uses a Hardware Description Language to automate the most tedious and error-prone aspects of design. 像合成药物,用门电路合成你写的逻辑(if, switch, for)

simulation: the activity of producing conditions which are similar to real ones, especially in order to test something, or the conditions that are produced.

emulate/imitate: do something or behave in the same way as someone else, especially because you admire them. 在x86上跑安卓emulator.

stimulate: 刺激,激励. stipulate: 讲明,规定

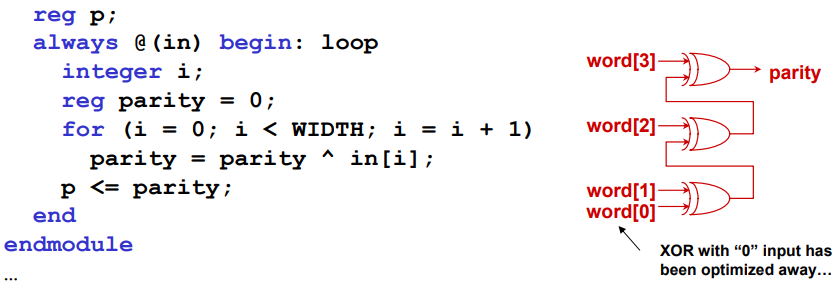

这么个for循环。深度学习利器之自动微分(2) 博客园 (cnblogs.com)

我一直想的是:for(int i = 0, j = 0; sqrt(i * j) != 0.4; i += 2, j -= -3);之类咋用硬件实现的?for(int i = 0; i < 100; i++) printf("%d\n", i), sleep(i); 这就是耍赖了……

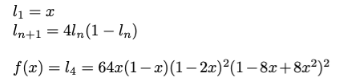

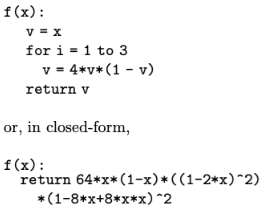

l = poly('x') for i in range(2,5): l = poly('4') * l * (poly('1') - l) print(i, l) print(' ',poly('64*x') * poly('1 - x') * poly('1 - 2*x') * poly('1 - 2*x') * poly('1 - 8*x + 8*x^2') * poly('1 - 8*x + 8*x^2')) D:\>poly.py 2 -4*x^2 + 4*x 3 -64*x^4 + 128*x^3 - 80*x^2 + 16*x 4 -16384*x^8 + 65536*x^7 - 106496*x^6 + 90112*x^5 - 42240*x^4 + 10752*x^3 - 1344*x^2 + 64*x -16384*x^8 + 65536*x^7 - 106496*x^6 + 90112*x^5 - 42240*x^4 + 10752*x^3 - 1344*x^2 + 64*x def __add__(a, b): d = {} for e,c in a.d.items(): d[e] = d.get(e, 0) + c for e,c in b.d.items(): d[e] = d.get(e, 0) + c return poly(d) def __sub__(a, b): return a + poly('-1') * b # :-)

logic-synthesis · GitHub Deep Reinforcement Learning (深度强化学习) for Logic Synthesis. Hmm,, 软硬件互帮互助了。Icarus好像有synthesis功能,因为字符串查找找到好多文件。里面的*.txt,如netlist.txt值得好好看。它好像用了lex和yacc: dir *.y /s dir *.lex /s

瞎猜瞎说: 不能import任何包,依然可以用python做事,但难度会大很多很多。电路设计里的library就像是python的各种模块。设计电路可以"import H265Decoder",也可以自己从头从底层做起。H265Decoder不从头开始,它又用了一大堆别的包。狭义的Verilog语言本身比python好学,因为语法特性少。Library或者说器件库里还有电气特性,对于真正的电路,尤其是模拟电路而言,比逻辑功能还重要。从能被编程的机器到能自己编程的机器,是巨大的一步,电脑编python程序还处于扯蛋阶段。电脑做逻辑合成相对简单些,因为输入和输出都相对受限。电脑能学会思考吗?编程在各式各样的的思考中难度系数如何?程序可并不都是Date d; if (d.getYear() % 100)...

Icarus的sample里有算sqrt的: https://files.cnblogs.com/files/blogs/714801/sqrt.zip

浙公网安备 33010602011771号

浙公网安备 33010602011771号