关于CMOS的一些知识点

1. CMOS开关阈值:

开关阈值VM定义为Vin=Vout的点,为使噪声容限最大并得到对称特性,希望Wp>Wn(若Vdd=2.5,则比例为3时,Vm=1.22);增加PMOS宽度,Vm移向Vdd;增加NMOS宽度,Vm移向GND。这一特性在某些场合可以消除噪声。

2. 如何减小一个门的传播延时(tp-hl,tp-lh):

- 减小负载电容。传播延时本质上由电容充放电造成

- 增加晶体管宽长比。但是注意增加W/L也增加电容,一旦本征电容超出外部负载,加宽长比就没有了意义,只是增加面积而已。

- 提高Vdd。但增加Vdd到一定程度后就没用了,反而会带来功耗增加,热电子,击穿等一系列问题。但要是工作电压太低,将加大延时、加大DC特性对器件参数(如VT)的敏感度、以及对外部噪声敏感。

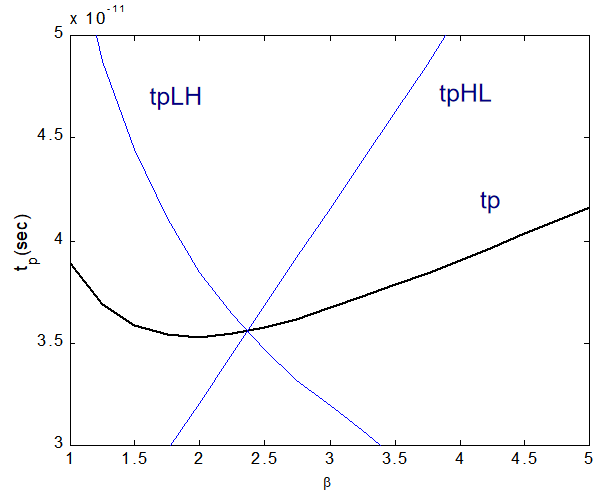

设β=(Wp/Lp)/(Wn/Ln);β=2.4时,tpLH=tpHL;β=1.9时,tp最小

3. 影响一个门delay的因素:

内部因素:Transition和Load;外部因素:PVT

同一种PVT条件下,cell delay主要由input transition和 output load决定。在大多数情况下,延迟随着输入transition time的增加而增加,但是延迟和输入transition time并不总是单调关系,尤其是在输出负载较小的情况下。

一般情况:

电压低、温度高、慢工艺——delay大,setup差

电压高、温度低、快工艺——delay小,setup好

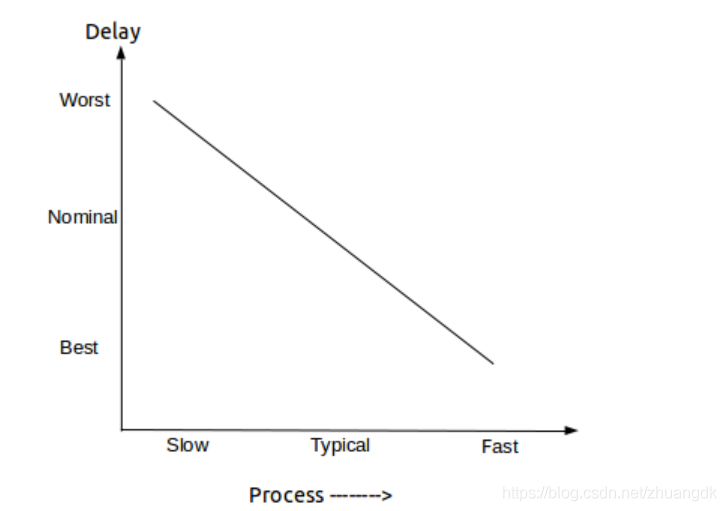

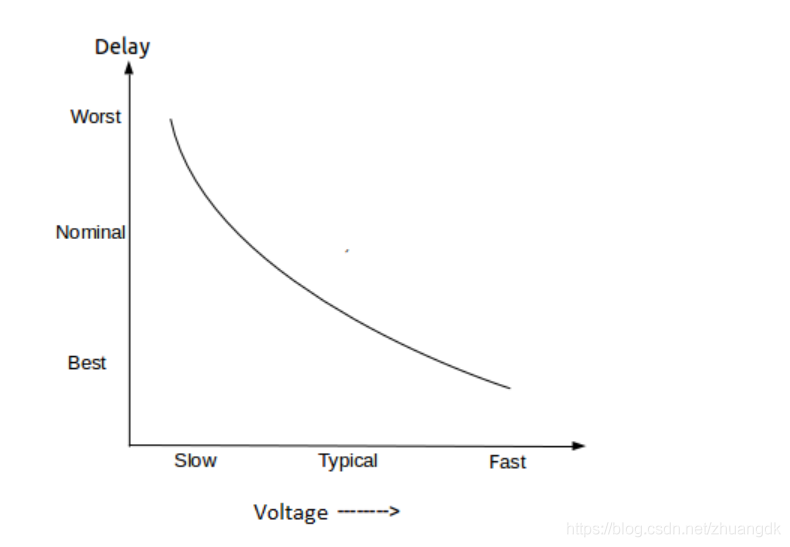

电压:

随着工艺越来越先进,超深亚微米工艺节点下芯片的供电电压越来越低。假设芯片以0.75V的电压工作。在芯片工作时有可能在特定的时间电压会发生变化。可以达到0.675V或0.825V。为了覆盖这个场景,我们考虑电压变化。

电源电压波动的一个重要原因是IR Drop。沿着电源网络电源被分配到芯片上的所有晶体管上。在整个芯片中,电源不是恒定的,它会随着cell的放置而变化。电源网络是由金属构成的,金属有自己的电阻和电容。因此,在电源网沿线有一个电压降。由于金属电阻的变化,所有标准电池和宏电路到达电源引脚的电源电压并不相同。考虑有两个cell,一个放置在直流电源附近,另一个放置在远的地方。由于越远的cell的互连线长度越长,它的电阻越大,导致IR降越高,从而降低了到达最远cell的供电电压。由于电压较低,这个cell比放置在更近的cell需要更多的延迟来上电。如果更近的cell得到更高的电压,那么cell更快,因此传播延迟也减少。这也是为什么在晶体管上有不同的延迟。cell的延迟取决于饱和电流,cell的饱和电流取决于电压。因此电压影响了一个单元的传播延迟。电源线路的自感也会造成电压降。例如,当一个晶体管切换到高电压时,它用电流给输出负载充电。这种时变电流(在短时间内)会产生相反的自感电动势。电压降的幅值为V=L*dI/dt,其中L为自感,I为通过线路的电流。

IR Drop是由电流流过电源网络的寄生电阻引起的。IR Drop降低了芯片工作的必要电压值。

电压变化的第二个重要原因是由寄生电感与电阻和电容结合引起的电源噪声。通过寄生电感的电流引起电压跳变。这两种效应一起不仅会导致电压下降,而且还会导致电压超调。

由于所有这些因素,我们必须考虑电压的变化。图2显示了电源电压与延迟的关系。

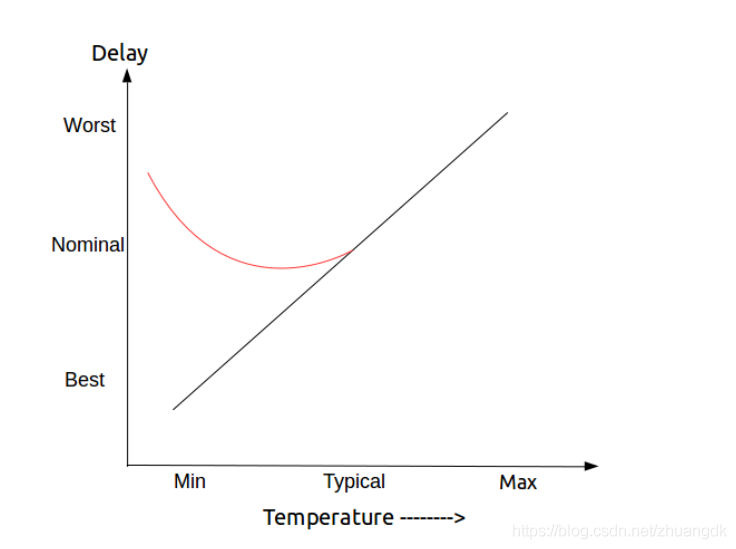

温度:

晶体管密度在整个芯片上是不均匀的。芯片的一些区域有更高的密度和更高的翻转,因此这部分会导致更高的功耗,而芯片的有些区域有较低的密度和较低的翻转,该区域具有较低的功耗。因此芯片某些区域的结温可能更高或更低,这取决于晶体管在该区域的密度。由于整个芯片的温度变化,它会在所有的晶体管中引入不同的延迟。这里讨论的温度变化是关于结的,而不是环境温度。芯片内部接点的温度变化范围可能很大,所以需要考虑温度变化。cell的延迟随着温度的升高而增加。但并非所有技术节点都是如此。对于深亚微米技术,这种行为是相反的。这种现象叫做逆温。

温度反转:延迟取决于输出电容和ID电流(与Cout成正比,与ID成反比)。当温度升高时,延迟也会增加(由于载流子浓度和迁移率的变化)。但当温度降低时,亚微米技术的延迟变化表现出不同的特征。对于小于65nm的技术节点,延迟随着温度的降低而增加,在-40℃时达到最大。这种现象被称为“逆温”。

为什么会发生逆温?

随着温度的升高,迁移率和阈值电压开始下降。延迟与迁移率成反比,与阈值电压成正比。迁移率和阈值电压的综合影响决定了延迟的大小。

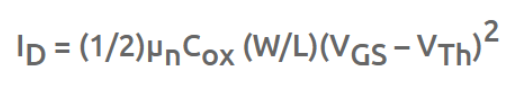

考虑MOSFET电流方程可以更好地理解;

在较高的技术节点中,电源电压很高,(VGS - VTh)值较大时,VTh的影响很小。因此,迁移率起着重要作用。因此,在较高的技术节点上,当温度降低时,迁移率升高,从而导致延迟减少。

在较低的技术节点(具体来说,小于65nm),电源电压非常低,VTh的影响则变大,而温度与Vth成反比,温度下降时,Vth升高,导致延迟增加。

浙公网安备 33010602011771号

浙公网安备 33010602011771号