FSM状态机设计

1. 状态机主要分为两类:Moore型 & Mealy型

Moore状态机:输出仅仅与当前状态有关

Mealy状态机:输出不仅取决于当前状态,还和输入有关

2. 三段式状态机:

第一段:时序逻辑描述current state和next stage的转换

第二段:组合逻辑描述next stage的变化

第三段:描述输出响应(用组合逻辑还是时序逻辑都可以,具体看需求)

3. 经典例子:序列检测器设计

输入X随机序列,输出Z,假设检测序列是1001;它分为可重叠和不可重叠两类

可重叠:检测到的序列的最后可以作为下一个序列的开始

X:0010010011001

Z:0000010010001

不可重叠: 检测到的序列的最后不可以作为下一个序列的开始

X:0010010011001

Z:0000010000001

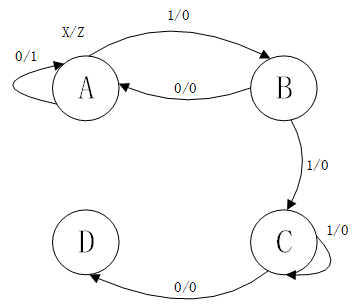

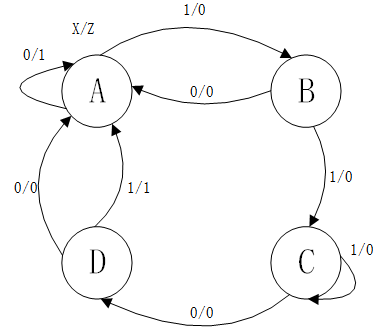

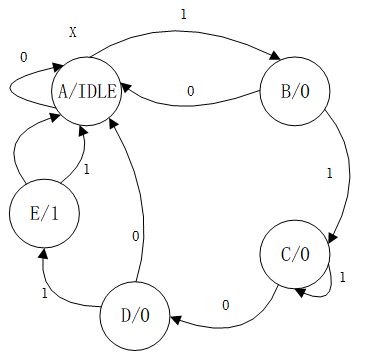

可重叠检测“1101”

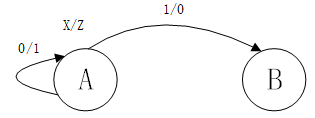

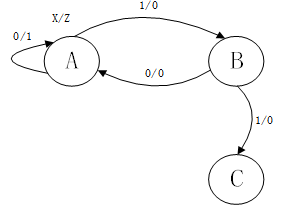

Mealy型:4个状态

Step1:设立初始状态

Step2:B状态有两个方向,取1,则进入C状态,取0,非检测序列,进A;B其实表示这个序列的开头,A到B只是表示序列开始。

Step3:C有两个方向,如果取1,继续C状态。因为C其实表示连续的最后一个1,,比如序列是001110...,则状态是AABCCD...

Step4:D有两个方向,如果是0,则情况是1100,回到A,序列未开始,如果是1,则是1101,检测输出,此时因为是可重叠,所以回到B,表示这个1是序列的开头

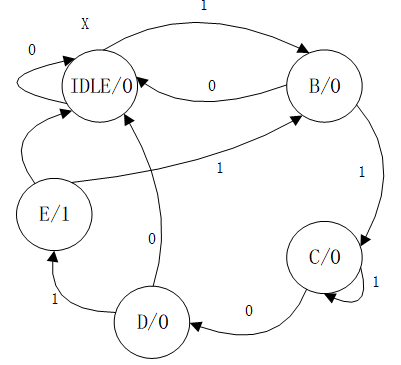

Moore型:5个状态

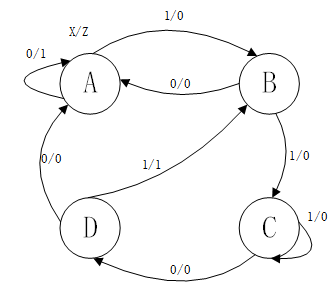

不可重叠检测“1101”

Mealy型

不可重叠永远是重新再来,D回到A

Moore型

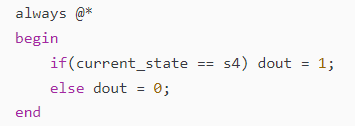

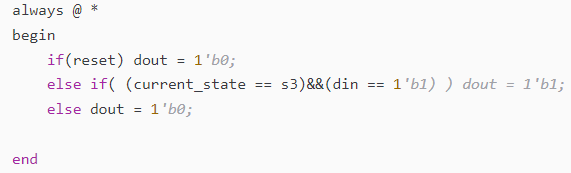

4. RTL编码:三段式

浙公网安备 33010602011771号

浙公网安备 33010602011771号