为什么不推荐全局异步复位?----兼谈ResetRecoveryTime

常见的D-触发器异步复位代码如下:

module resetff(

output reg dat_o;

input clk_i, nRst_i;

input dat_i;

);

always @ (posedge clk_i or negedge nRst_i)

if(!nRst_i)

dat_o <= 1’b0;

else

dat_o <= dat_i;

endmodule

一般情况下这是没有问题的,但当Module的边界就是FPGA的边界时,可能会引起灾难性的后果(… is very dangerous if the module boundary represents the FPGA boundary.)。例如Reset Recovery Time Violating。

先了解一下什么是Reset Recovery Time。

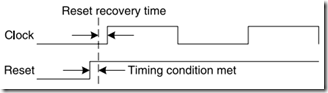

Altera文档的说法是:Recovery time is the minimum length of time for the deassertion of an asynchronous control signal.这种说法有点模糊,另一种说法如下:The reset recovery time is a type of setup timing condition on a flip-flop that defines the minimum amount of time between the deassertion of reset and the next clock edge.

顺便说明一下,Recovery Time和Removal Time都是和de-assertion相关的。

如下图所示:

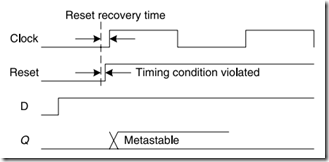

当Reset Recovery Time violated时,有意思的是,触发器输出Q会进入亚稳态:

也是基于上述原因,不推荐全局异步复位。

posted on 2012-04-27 16:38 freshair_cn 阅读(967) 评论(0) 编辑 收藏 举报