DDR读写简介及相关

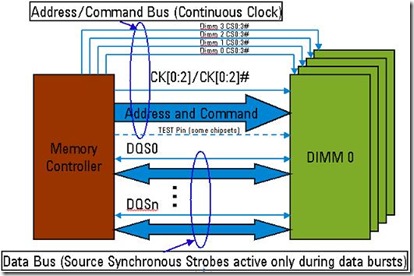

DDR总线的体系结构如下:

其中DQS是源同步时钟,在接收端使用DQS来读出相应的数据DQ,上升沿和下降沿都有效。DDR1总线,DQS是单端信号,而DDR2&3, DQS则是差分信号。DQS和DQ都是三态信号,在PCB走线上双向传输。CK是地址/命令时钟,是单向信号。

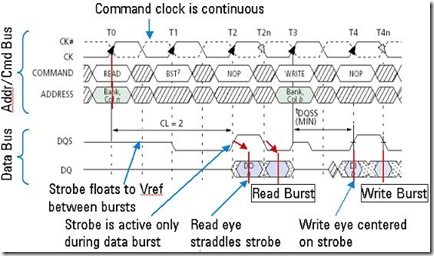

DDR总线读写时序如下:

读操作时,DQS信号的边沿在时序上与DQ的信号边沿处对齐;写操作时,DQS信号的边沿在时序上与DQ信号的中心处对齐。所以在做DDR控制器时,要把DQS时钟做90度的相移。上图中,Addr/Cmd Bus意思是地址/命令总线,都是时钟的上升沿有效,其中命令由:/CS(片选),/RAS, /CAS,/WE(写使能)决定,比如:“读”命令为:LHLH,“写”命令为:LHLL等。操作命令很多,主要是NOP(空超作),Active(激活),Write,Read,Precharge (Bank关闭),Auto Refresh或Self Refresh(自动刷新或自刷新)等(细节请参考:Jedec规范JESD79)。

许多计算机使用时钟频率为533MHz的DDR2内存,更先进的DDR2内存正在日益普及,它的时钟频率在400 MHz-800 MHz之间,新的DDR3内存的时钟频率则可以工作在800MHz-16OOMHz之间。DDR3内存芯片还有另外一个长处:更低的能耗,它的运行电压是1.5伏,低于DDR2内存芯片的1.8伏和DDR1内存芯片的2.5伏。在使用电池的设备中能够延长电池续航时间,因为能耗低,产生的热量也就少,从而对冷却的要求也就低一些。

DDR 2&3几个新增特性的含义是:ODT( On Die Termination),DDR1 匹配放在主板上,DDR2&3把匹配直接设计到DRAM芯片内部,用来改善信号品质。OCD(Off Chip Driver)是加强上下拉驱动的控制功能,通过减小DQS与/DQS(DQS是数据Strobe,源同步时钟,数据的1和0由DQS作为时钟来判断) Skew(时滞)来增加信号的时序容限(Timing Margin)。Posted CAS是提高总线利用率的一种方法。AL(Additive Latency)技术是相对于外部CAS,内部CAS执行一定的延时。

posted on 2012-01-10 11:41 freshair_cn 阅读(10804) 评论(0) 编辑 收藏 举报