使用Quartus建立第一个FPGA工程

欢迎使用sina微博@颠覆的饕餮进行讨论,一起探讨学习~ ~嘿嘿

到 www.altera.com.cn 免费申请到Quartus网络版并且安装,这个过程非常简单。

安装好Quartus后,我们开始建立第一个FPGA工程,我们开始建立第一个FPGA工程。

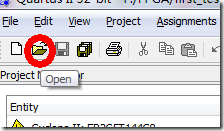

打开后界面是

单击左上角 file->new project wizard 出现下面的界面

当然是next

之后在指定建立工程的路径

注意路径不能有中文!!

之后就是工程名,同样不能使用中文。

软件自动完成顶层设计名~嘿嘿

之后next,出现

要我们加入已有文件,当然我们没有任何文件加入,直接next~

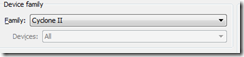

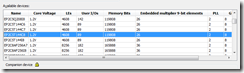

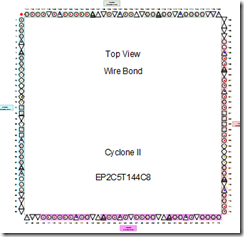

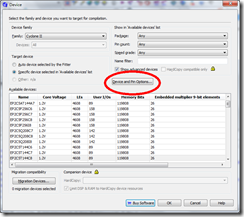

之后就是选择型号了~如图

我是用

然后next,出现

让你选择外部工具,注意都我用的是

同样从 www.altera.com.cn 申请modelsim初学版,免费的~~然后呢我们用的是verilog进行开发所以选verilog HDL

之后出现汇总表,

当然是next。

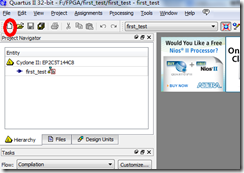

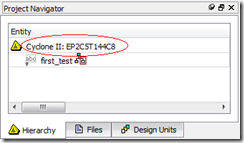

这样工程就建立ok了~~

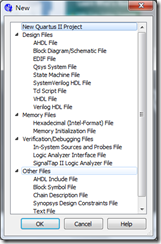

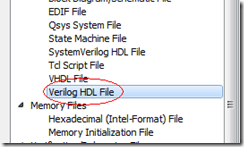

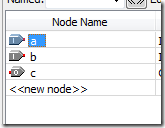

开始我们敲我们的代码~首先我们必须建立一个空文本,如图

点击圈圈中的图标,出现

选择

然后输入:

/*******************************************************

module: first_test

author: TT

description: Just the first FPGA project.

*******************************************************/

module first_test (a,b,c);

input a;

input b;

output c;

assign c = a&b;

Endmodule

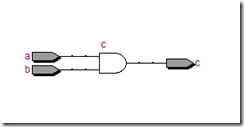

先对代码进行分析/* */内的是注释,不用管它

module指定模块名字,括号里面的是端口列表,我们有3个端口 a b c

之后指定端口的类型,很明显的 input和output。

再然后是对c进行赋值,这里使用到关键字assign 一般assign表示描述的是组合逻辑。

很明显,我们只是描述了1个与门,c等于a与b。

最后的Endmodule代表模块结束

之后点击:

进行综合布局布线

会弹出是否保存,当然yes,跳出保存文件名称,软件已经自动生成,不要改动~直接ok

一路通过,但是出现12个警告~

3个Parallel compilation is not licensed and has been disabled表示你使用的是多核cpu,并行编译不被许可,这个是网络版的限制,可以不理他

Feature LogicLock is only available with a valid subscription license. You can purchase a software subscription to gain full access to this feature.这个同样是网络版的限制,也不理他

No clocks defined in design.没有使用时钟,这个是由于我们只描述了一个组合逻辑,没有使用时钟,无伤大雅

Found 1 output pins without output pin load capacitance assignment这个是没有指定输出引脚后面的电容,跟以后的门级仿真有关,我们先放过,其实一般也就让它过去了。。。。。

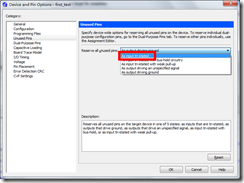

The Reserve All Unused Pins setting has not been specified, and will default to 'As output driving ground'.这个表示你没有指定没用到的管脚状态。。。我们要解决的就是这个。

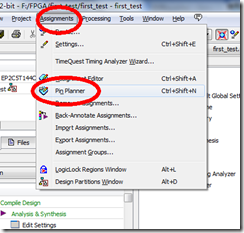

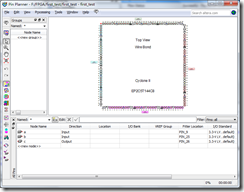

首先先为我们的与门分配管脚

跳出

我们只要在

上面输入选择的指定管脚就ok了,当然你也可以拖动

上面的管脚到

上面完成分配

我们随意指定为

直接关闭~

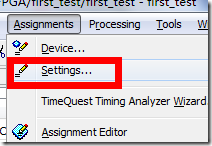

然后点击

再点击

选择

然后一路ok~

然后重新进行我们的综合

就是圈圈的位置~~

大功告成~只有10个警告了~都是可以无视的~~

看看报表

只用了一个门,也是我们意料中的~~

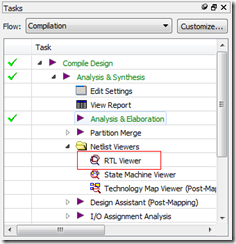

看看

如图

也是意料中的~~

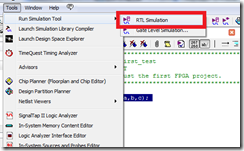

然后我们进行仿真

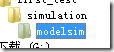

之后在

打开我们生成的test bench

在们工程目录的

中,一般文件名与工程名一样,后缀是vt

我们只要拉到45行,把原来的

initial

begin

// code that executes only once

// insert code here --> begin

// --> end

$display("Running testbench");

end

改为

initial

begin

a=1'b0;

b=1'b0;

#10;

a=1'b1;

b=1'b0;

#10;

a=1'b0;

b=1'b1;

#10;

a=1'b1;

b=1'b1;

#10;

$stop;

end

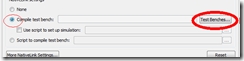

然后

点击test benches

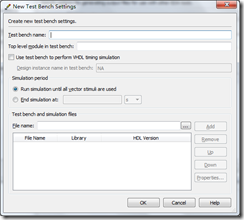

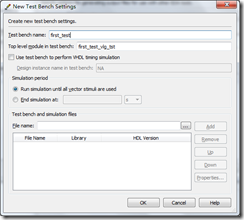

再接下来的对话框点击New

出现

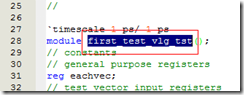

我们回到

的文本中,到28行

然后回到这里

我们的

就是文件的名字,不需要vt

就是刚刚我们在28行得到的模块名

之后在

加入文件,点击Add

一路ok

然后点击

进行仿真。